通信设备中的电场和磁场会干扰通信信号,从而引起电磁干扰(EMI),并通过注入噪声来降低系统性能。在便携式电子设备中,调压模块(VRM)会同时产生传导和辐射EMI。VRM通常是开关模式电源,利用调制技术来输出所需的DC电压。在VRM中,可以采用扩频调频作为降低EMI的技术。通过使用此技术,噪声可以在更宽的带宽上传播,并且可以消除特定频率下出现的峰值和平均噪声。

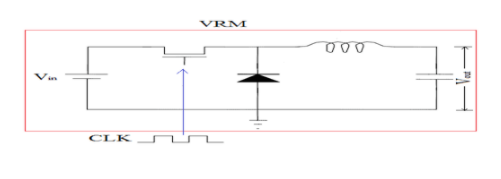

带时钟信号的VRM提供给开关设备

VRM扩频频率调制

在通信系统板中用作VRM的开关模式DC-DC稳压器利用扩频频率调制技术来降低EMI和噪声。通常,DC-DC转换器采用固定或恒定开关频率操作。这种调制方法的快速切换会产生基频和谐波频率的噪声,以及传导和辐射的EMI。

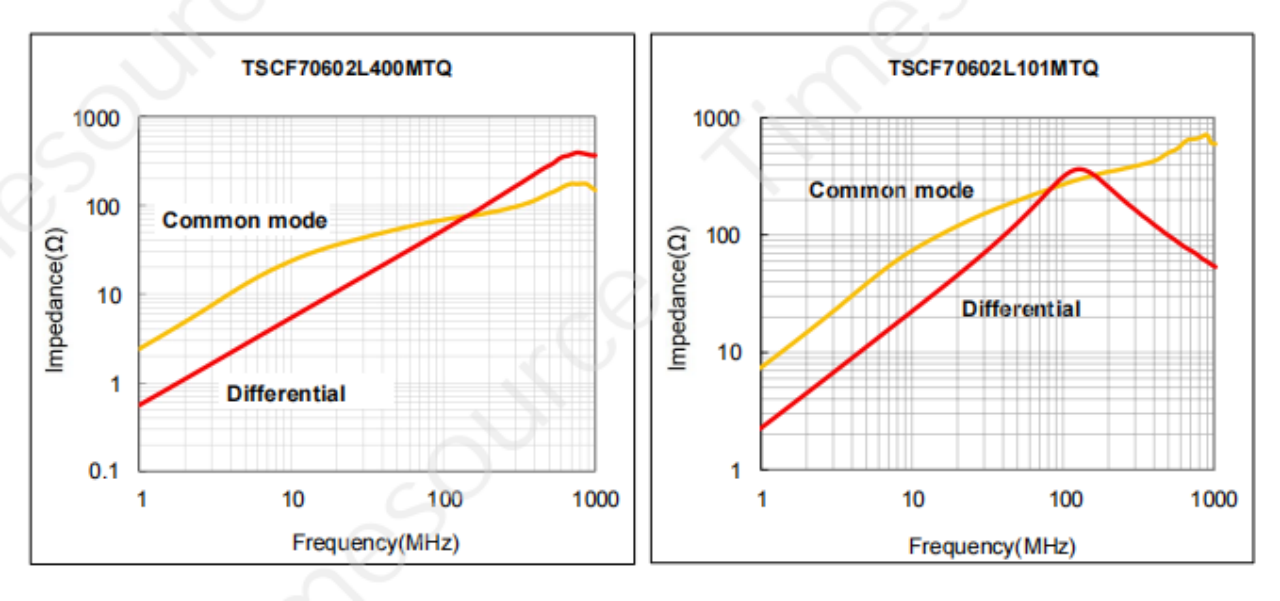

不良的pcb设计布局以及电容器和电感器的不良放置会增加EMI和噪声的影响,并且通常是导致VRM问题的主要原因。在某些包含多个DC-DC稳压器的电子设备中,EMI和噪声集中在一个特定的频率上,并开始危害正常的电路操作和邻近系统。扩频调制技术通过集中于任何特定频率来分散噪声。试图降低EMI的能量,振幅和强度。它还可以补偿DC-DC转换器中的输入电流和输出电压纹波。

在扩频调制中,开关转换器的时钟频率是不固定的。调制时钟的频率不断变化,因此每次都会产生不同频率的噪声和谐波。时钟在扩频调制中继续运行。通过使用非固定频率时钟,可以相对降低EMI峰值能量,并将EMI能量分配到其他频率。

扩频频率调制技术

即使周期性调频在扩展噪声频谱方面很有效,我们的讨论仍将集中在伪随机调制上。在这种技术中,时钟以伪随机方式从一个频率转换到另一频率。这提供了基频的充分衰减和更宽的频谱扩展。

伪随机调制中流行的方法是随机脉冲位置调制(RPPM),随机脉冲宽度调制(RPWM),以及具有固定占空比(RCFMFD)或具有可变占空比(RCFMVD)的随机载波频率调制。在RPPM中,时钟脉冲的位置在每个开关周期内都是随机的。它与恒定PWM开关相当,时钟周期的起始位置是随机的,而不是在开关周期开始时开始。在RPWM中,平均脉冲宽度保持在所需的占空比,但是脉冲宽度连续变化。RCFMFD的特性是具有随机开关周期的固定占空比。用恒定的脉冲宽度替换RCFMFD中的恒定占空比后,它将转换为RCFMVD。在RCFMVD中,占空比是随机的,但是平均占空比满足期望值。

如果您正在处理可处理电信频率范围的稳压电源电路,那么就需要通过扩频技术对其进行调制。VRM扩频频率调制通过将其频率扩展到更宽的带宽来降低EMI,噪声和纹波效应。与恒定开关频率调制技术相比,它还提高了效率,总损耗大大降低。

编辑:hfy

-

PCB设计

+关注

关注

396文章

4939浏览量

95858 -

电磁干扰

+关注

关注

36文章

2510浏览量

108095 -

调压模块

+关注

关注

0文章

4浏览量

8726 -

DC-DC稳压器

+关注

关注

0文章

17浏览量

10717

发布评论请先 登录

电磁干扰如何影响示波器

单片机系统的电磁兼容性(EMC)设计

浅谈晶振在PCB设计中的要点

干货分享 I PCB设计电磁兼容问题交流与解答(二)

从入门到精通:PCB设计必须遵守的5大核心原则

大功率PCB设计 (一):电压需求与隔离

改善EMC的PCB设计原理

PCB设计师必看!这些‘反常识’操作正在毁掉你的电路板

为了减少电磁干扰,装置在硬件设计时应该遵循哪些原则?

深度解读PCB设计布局准则

霍尔元件PCB布局的10个防干扰技巧

开关电源的PCB设计

时源芯微 开关电源电磁干扰的控制技术

PCB设计电压调节模块关于电磁干扰布局

PCB设计电压调节模块关于电磁干扰布局

评论