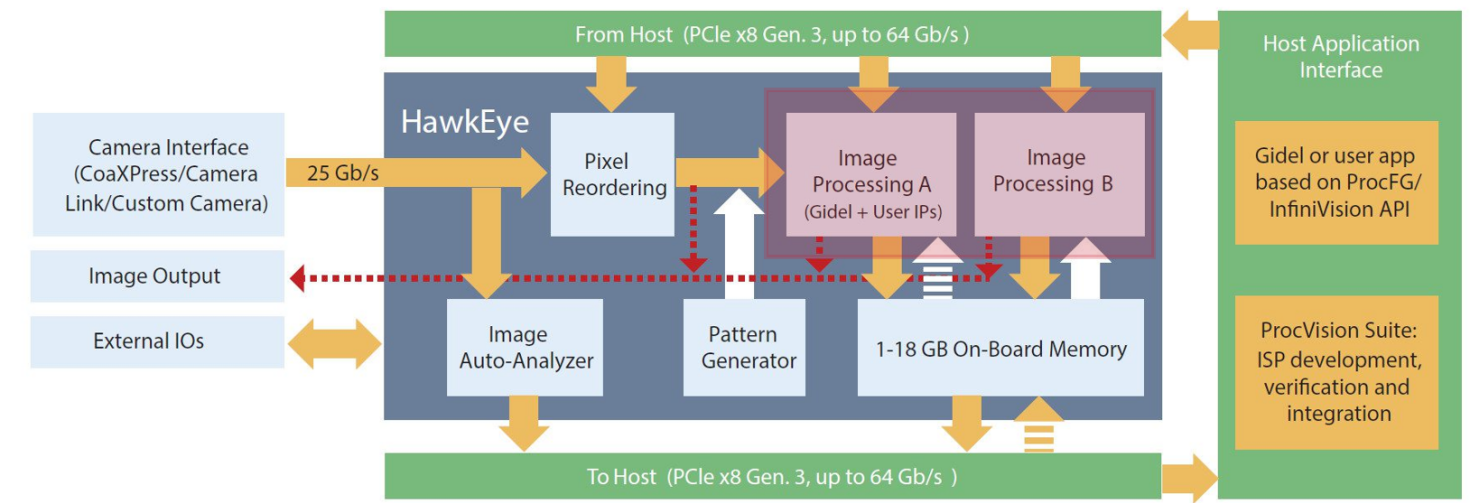

图像处理算法在各种场景中都有广泛应用,借助于FPGA并行计算的优势可以将算法性能有效提升,但为了提升系统整体性能,仅仅提升某一部分的性能是不够的,一个好的方法是在FPGA内实现全部视频输入输出接口和图像算法的完整通路。本Overlay的视频输入来自OV5640摄像头,包含多个可任意切换的图像处理算法,并包含了一个HDMI输出接口显示处理结果。

图像处理算法在各种场景中都有广泛应用,借助于FPGA并行计算的优势可以将算法性能有效提升,但为了提升系统整体性能,仅仅提升某一部分的性能是不够的,一个好的方法是在FPGA内实现全部视频输入输出接口和图像算法的完整通路。本Overlay的视频输入来自OV5640摄像头,包含多个可任意切换的图像处理算法,并包含了一个HDMI输出接口显示处理结果。

设备清单

- PYNQ-Z2套件

- OV5640 Camera Board

(如Waveshare OV5640或者其它兼容版本)

- PMOD-Camera adapter

- HDMI monitor

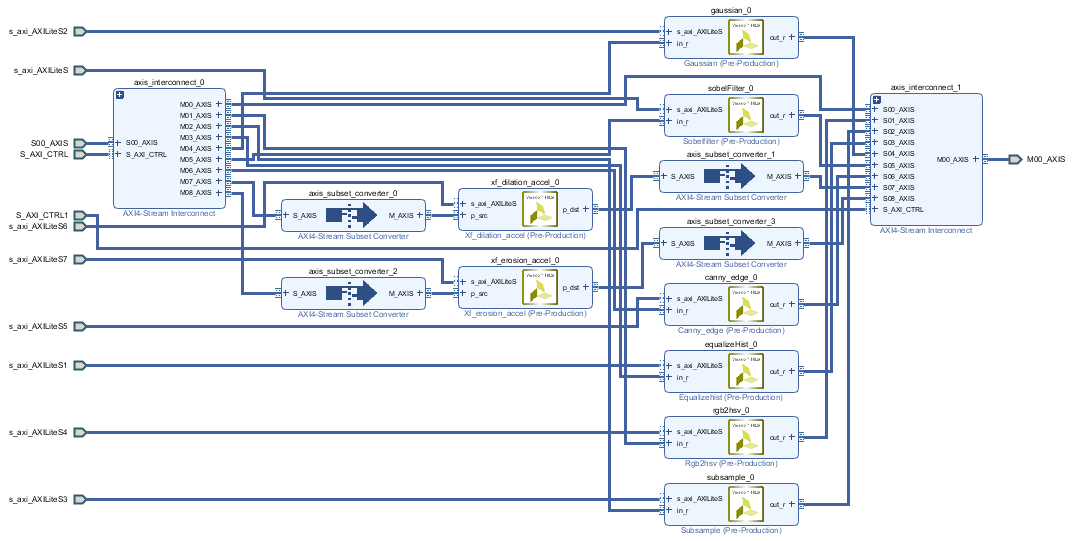

系统架构

算法列表

Overlay中实现了多个图像处理算法,在HLS中实现并封装为IP后在Block Design中被调用,读者如有兴趣可以在Github的/boards/src/ip/目录获取源代码。

1) rgb2hsv

2) subsample

3) equalizehist

4) gaussianBlur

5) sobel

6) canny

7) dilation

8) erosion

快速开始

环境需求PYNQ v2.4,在PYNQ-Z2板卡联网并启动后在终端中运行如下代码安装Overlay到本地:

# (on PYNQ v2.4 only)

sudo pip3 install --upgrade git+https://github.com/xupsh/Pynq-CV-OV5640.git

案例演示

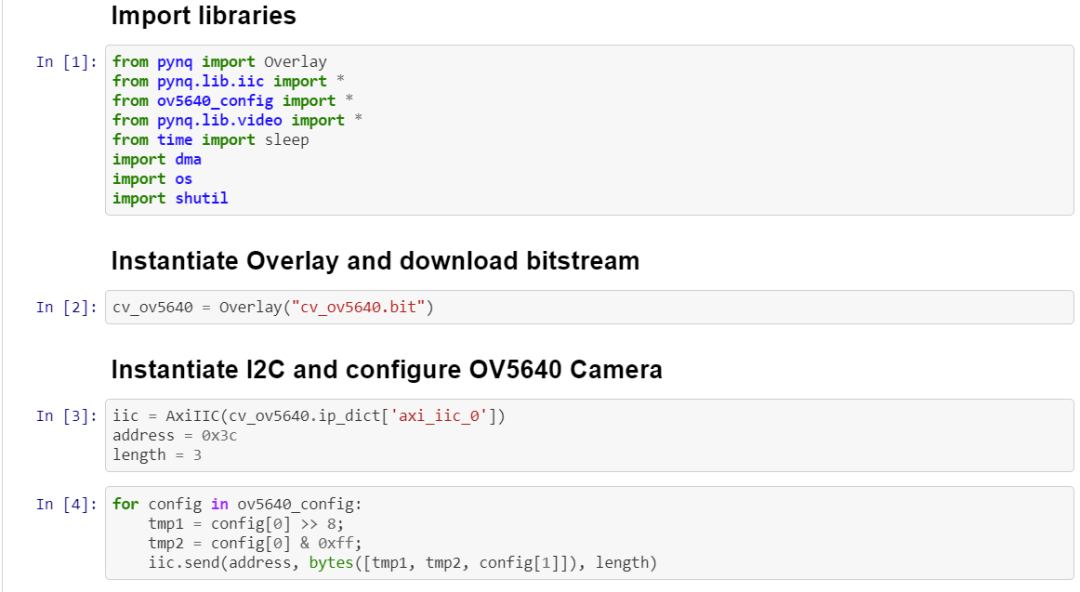

Notebook名称:pynq4cv.ipynb

在Overlay中例化了一个I2C接口来对OV5640进行配置,我们可以在Jupyter Notebook上通过Python对摄像头进行初始化,也可以通过改动ov5640_config.py文件的内容来修改配置。

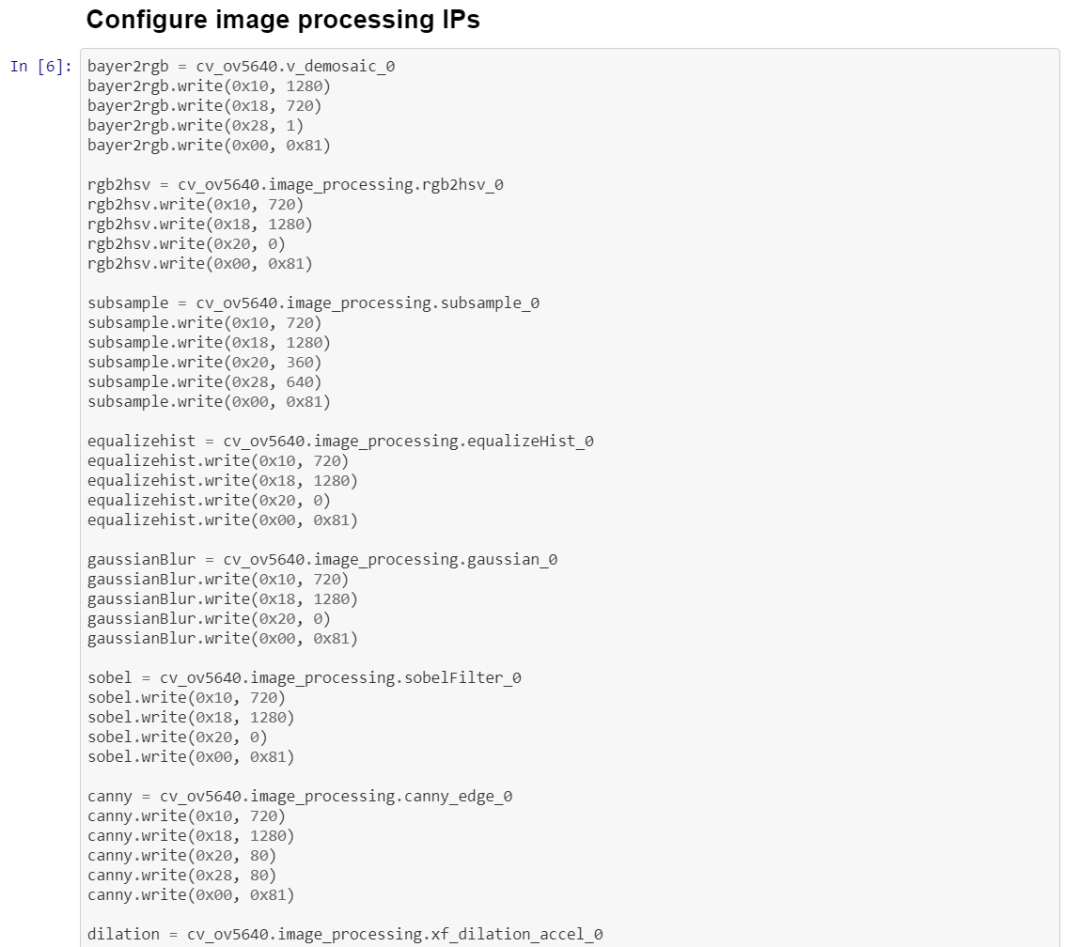

接下来,我们对Overlay中实现的图像处理算法进行配置。

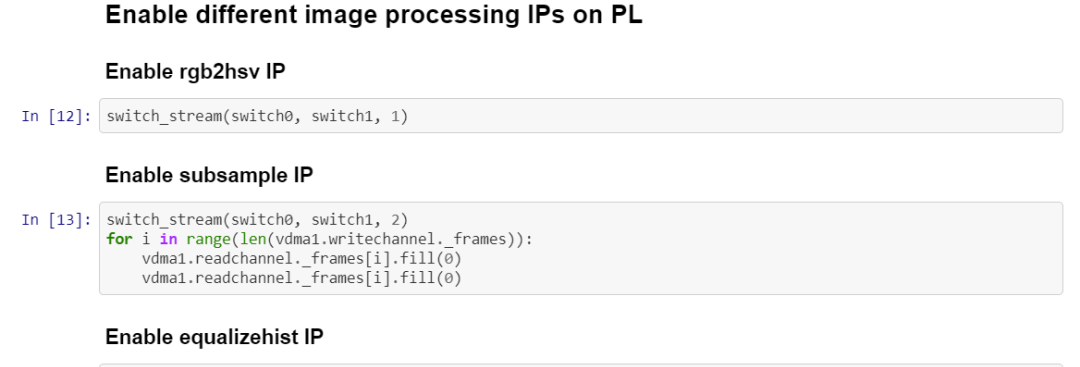

配置完成后,还需要选择使能Overlay中的某一个算法来对从OV5640获取的图像进行处理,默认不经过任何图像处理算法,从OV摄像头获取的图像直接在HDMI显示器上显示。

我们也可以抓取OV5640拍摄的图片并在Jupyter Notebook上显示。

接下来,我们可以使能不同的图像处理算法,通过观察HDMI显示器的输出,观察不同算法的处理结果。

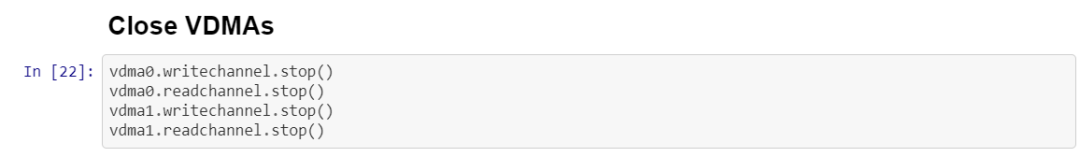

在运行完毕后,记得关闭VDMA,以防止运行其它Overlay时报错。

总结与展望

本案例在PL内实现了一个完整的视频通路,对图像数据直接进行硬件加速处理。相比于USB摄像头减少了图像数据从PS到PL拷贝和回传的负载,提高了系统的性能同时极大降低了图像处理的延时

编辑:hfy

-

FPGA

+关注

关注

1664文章

22508浏览量

639500 -

图像处理

+关注

关注

29文章

1350浏览量

59714

发布评论请先 登录

综合图像处理硬件平台设计资料:2-基于6U VPX的双TMS320C6678+Xilinx FPGA K7 XC7K420T的图像信号处理板

寻找对RISCV众核并行计算感兴趣的伙伴、朋友

寻找对RISCV众核并行计算感兴趣的伙伴

为啥 AI 计算速度这么惊人?—— 聊聊 GPU、内存与并行计算

一文看懂AI大模型的并行训练方式(DP、PP、TP、EP)

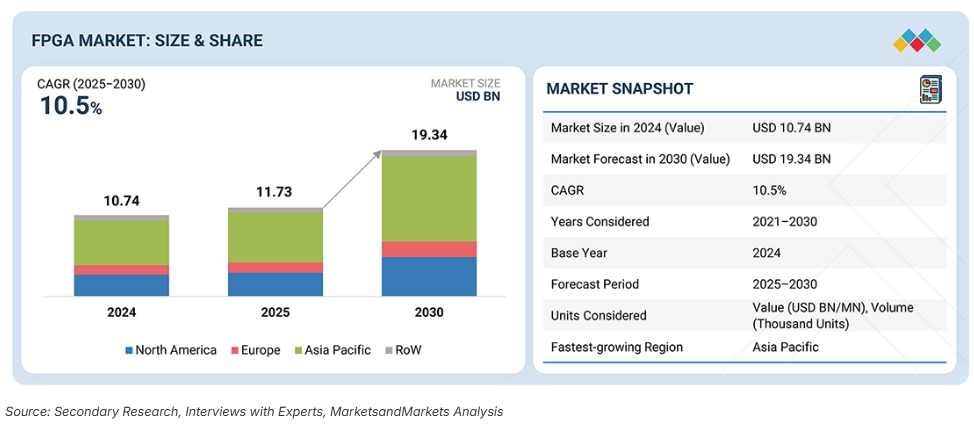

MarketsandMarkets FPGA行业报告,2026~2030 FPGA市场洞察

从自然仿真到智能调度——GPU并行计算的多场景突破

在树莓派Pico上运用不同的并行化手段

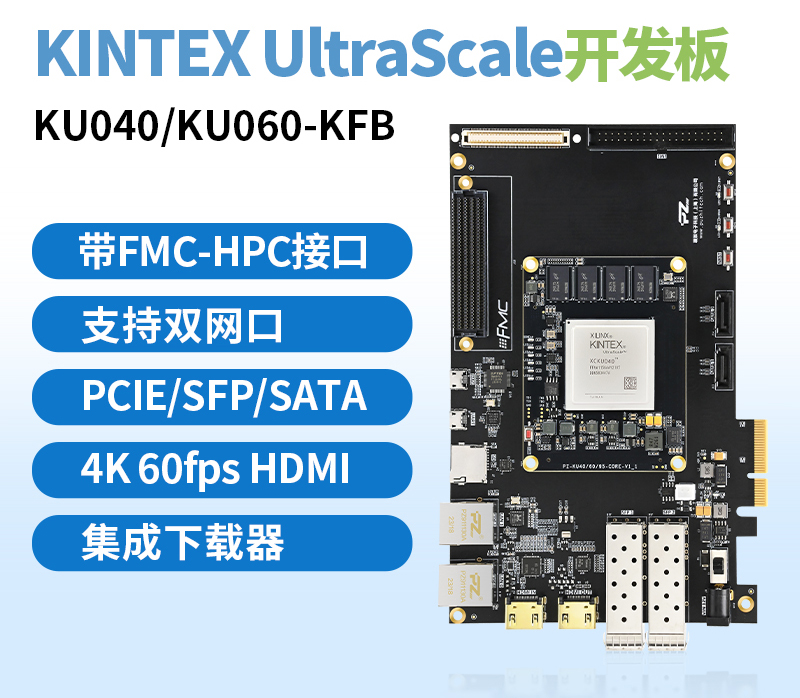

Kintex UltraScale 纯 FPGA 开发平台,释放高速并行计算潜能,高性价比的 FPGA 解决方案

AI芯片:加速人工智能计算的专用硬件引擎

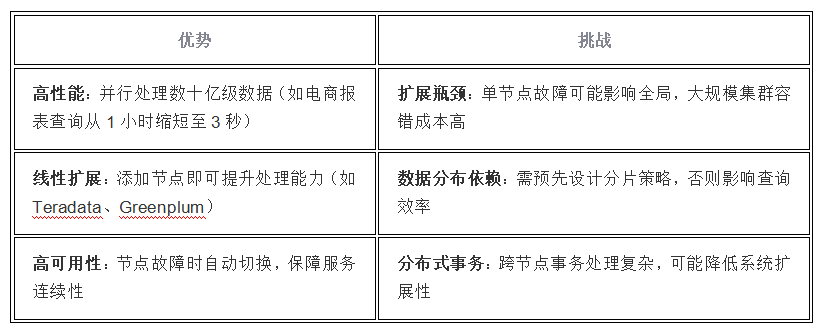

多节点并行处理架构

基于FPGA并行计算的图像处理案例

基于FPGA并行计算的图像处理案例

评论