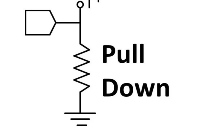

在上拉电阻和下拉电阻的电路中,经常有的疑问是:上拉电阻为何能上拉?下拉电阻为何能下拉?下拉电阻旁边为何经常会串一个电阻?

简单概括为:电源到器件引脚上的电阻叫上拉电阻,作用是平时使该引脚为高电平,地到器件引脚上的电阻叫下拉电阻,作用是平时使该引脚为低电平。低电平引脚在IC内部与GND相连接;高电平引脚在IC内部与超大电阻相连接。 上拉就是将不确定的信号通过一个电阻钳位在高电平,电阻同时起限流作用,下拉同理。对于非集电极(或漏极)开路输出型电路(如普通门电路),其提升电流和电压的能力是有限的,上拉和下拉电阻的主要功能是为集电极开路输出型电路提供输出电流通道。上拉是对器件注入电流,下拉是输出电流;强弱只是上拉或下拉电阻的阻值不同,没有什么严格区分。 当IC的I/O端口,节点为高电平时,节点处和GND之间的阻抗很大,可以理解为无穷大,这个时候通过上拉电阻(如4.7KΩ,10KΩ电阻)接到VCC上,上拉电阻的分压几乎可以忽略不计;当I/O端口节点需要为低电平时,直接接GND就可以了,这个时候VCC与GND是通过刚才的上拉电阻(如4.7KΩ,10KΩ电阻)连接的,通过的电流很小,可以忽略不计。 本文转载自:电子发烧友网 免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。 关于【M博士问答】

关于贸泽

贸泽电子设计圈由贸泽电子(Mouser Electronics)开发和运营,服务全球广大电子设计群体。贸泽电子原厂授权分销超过800家知名品牌,可订购500多万种在线产品,为客户提供一站式采购平台,欢迎关注我们,获取第一手的设计与产业资讯信息!

原文标题:上拉电阻为什么能上拉?看完恍然大悟

文章出处:【微信公众号:贸泽电子设计圈】欢迎添加关注!文章转载请注明出处。

-

电阻

+关注

关注

88文章

5814浏览量

179950

原文标题:上拉电阻为什么能上拉?看完恍然大悟

文章出处:【微信号:Mouser-Community,微信公众号:贸泽电子设计圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

用这种方法来估测CH552的上拉电阻可以吗?

MOS管加下拉电阻的原因是什么?

MCU未使用IO如何处理?

199元的嵌入式“黑马”:明远智睿RK3568核心板为何能引爆市场?

选择厚声贴片电阻的原因有哪些?

浮思特 | 电子电路下拉电阻详解:原理、计算与应用指南

上拉电阻为何能上拉?下拉电阻为何能下拉?答案在此

上拉电阻为何能上拉?下拉电阻为何能下拉?答案在此

评论