下拉电阻是电子电路设计中的重要组成部分,尤其在处理数字逻辑、晶体管和通信接口时。本教程将系统讲解其基本原理、计算方式、应用场景、选型要点、功耗考量,以及在晶体管和串行通信线路中的实际应用。

什么是下拉电阻?

下拉电阻是连接在信号线(如微控制器输入引脚或晶体管栅极)与地(GND)之间的电阻元件。其主要功能是确保当信号线无主动驱动时,能稳定维持在确定的低逻辑电平(通常为0V或接地电位)。

数字输入引脚通常呈现高阻抗特性,这意味着它们仅需极小的驱动电流。若无下拉电阻,悬空(未连接)的输入引脚可能拾取环境噪声导致电压波动,进而引发电路异常行为。因此下拉电阻的核心作用体现在:

• 消除数字电路中的悬空输入(不确定电压状态)

• 确保无主动驱动时保持稳定低电平(对应0V)

合理选值的下拉电阻可提供明确的接地路径。当输入被主动驱动为高电平时,电阻几乎不影响信号传输。常见应用场景包括按钮开关电路和数字逻辑电路。

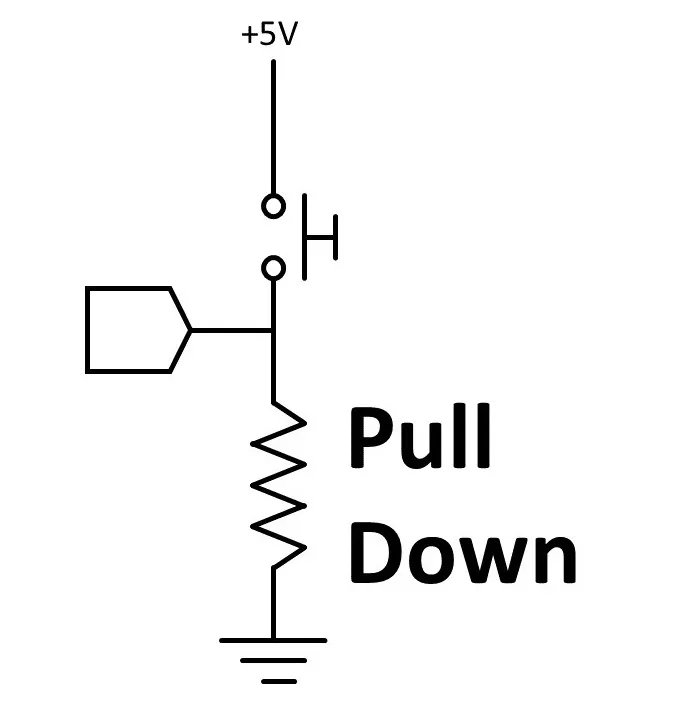

电路图中,下拉电阻通常以标准电阻符号表示,连接在输入引脚与接地符号之间。图1展示了典型的下拉电阻配置方案。

图1

图1下拉电阻计算公式

虽然下拉电阻的核心功能是建立确定低电平状态,但掌握相关计算公式有助于合理选型,需重点考虑:

• 阻值过低会在高电平输入时造成功耗浪费

• 阻值过高可能因漏电流导致电压无法有效下拉

根据欧姆定律:

当输入无驱动时,输入引脚电压为:

VIN = 0V

当输入高电平(如5V或3.3V)时,流过电阻的电流:

I = (V - 0V) / R

其中I为电流(A),V为电阻两端电压(V),R为电阻值(Ω)。

下拉电阻选型指南

理想的下拉电阻值需满足:

• 足够低:确保无信号时可靠下拉至0V

• 足够高:避免高电平信号时电流过大

典型取值范围为1kΩ-100kΩ,具体选择需考量:

• 电路输入阻抗特性

• 系统功耗限制

• 开关速度要求(低阻值响应更快)

实用选型建议:

• 通用场景(Arduino/Raspberry Pi等微控制器):10kΩ-47kΩ(10kΩ最常用)

• 强抗干扰需求:1kΩ-10kΩ(抗噪能力强但功耗较高)

• 低功耗场景:47kΩ-100kΩ(易受噪声和漏电流影响)

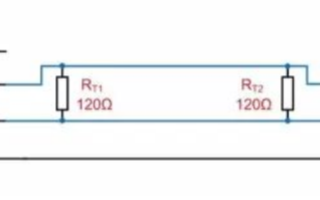

• 高速信号(I²C/SPI接口):1kΩ-4.7kΩ

典型应用场景

下拉电阻广泛应用于需要默认低电平的电路:

• 数字输入引脚:防止信号悬空

• 按键消抖:确保未按下时为明确低电平

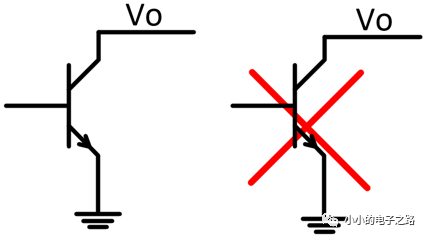

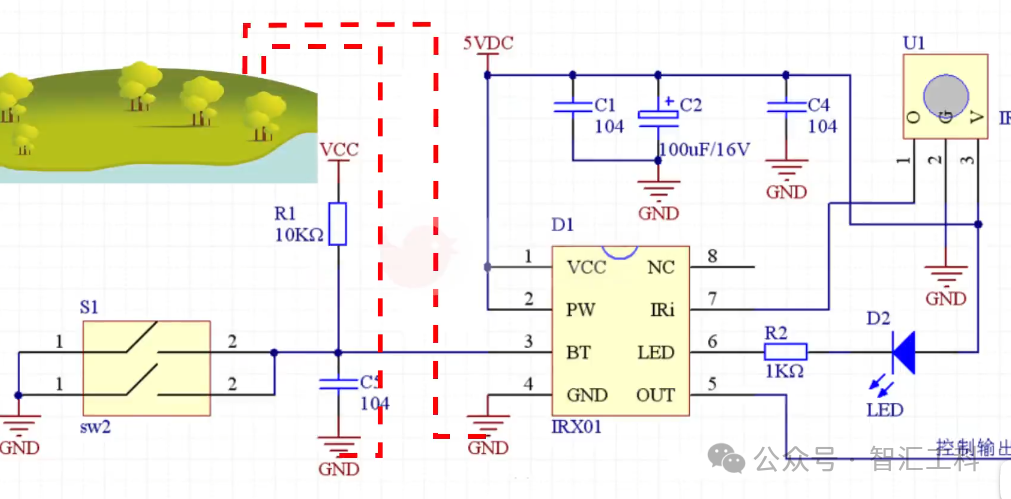

• 晶体管基极/栅极控制:无信号时保持0V,防止误触发

• 通信接口(I²C/UART/SPI):维持线路空闲时为低电平

计算实例

示例1:

5V逻辑电平系统,选用10kΩ下拉电阻:

I = 5V / 10,000Ω = 0.5mA

该电流既满足低功耗要求,又能可靠下拉。

示例2:

5V微控制器系统,考虑驱动源输出阻抗(ROUT=100Ω),选用10kΩ下拉电阻:

高电平电压 = 5V × {10000Ω /(100Ω + 10000Ω)}= 4.95V

该值远高于5V系统的高电平阈值。

驱动电流计算:

I = 5V / (100Ω + 10000Ω) = 0.495mA

属于较低功耗范围。

-

下拉电阻

+关注

关注

4文章

154浏览量

21422 -

电路设计

+关注

关注

6746文章

2802浏览量

220445 -

电子电路

+关注

关注

78文章

1294浏览量

69421

发布评论请先 登录

上拉电阻和下拉电阻的选型和计算

浮思特 | 电子电路下拉电阻详解:原理、计算与应用指南

浮思特 | 电子电路下拉电阻详解:原理、计算与应用指南

评论