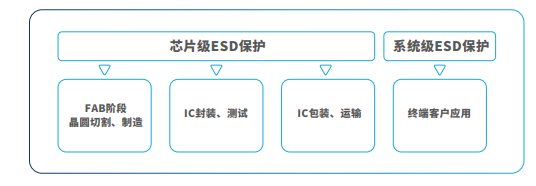

本文对电容器的ESD(Electrostatic Discharge:静电放电)耐性进行说明。

ESD耐性的测试方法耐性

人体和设备所携带的静电向整机及电子元件放电时,由于增加了冲击性的电磁能量,则产品必须具备一定量ESD耐力。

ESD耐性测试方法根据产生静电的模型,分为以下三种:

①HBM

②MM

③CDM

其中,我们为您说明一般较多用作电容器ESD耐性测试方法的①HBM。

①HBM(Human Body Model:人体模型):假设由人体静电放电时的测试

②MM(Machine Model:机械模型):假设由机械静电放电时的测试

③CDM(Charged Device Model:带电设备模型):假设由带电设备静电放电时的测试

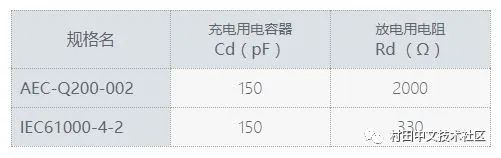

HBM的ESD测试规格有AEC-Q200-002和IEC61000-4-2等,HBM模型常熟如下表所示因规格有所不同。

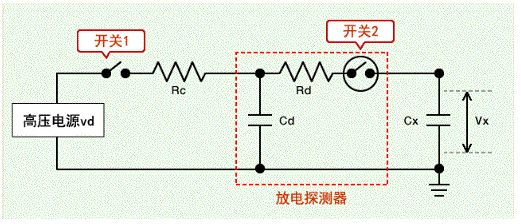

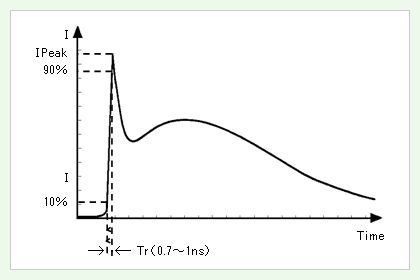

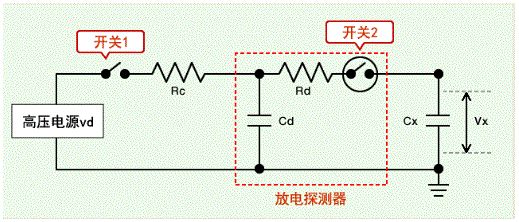

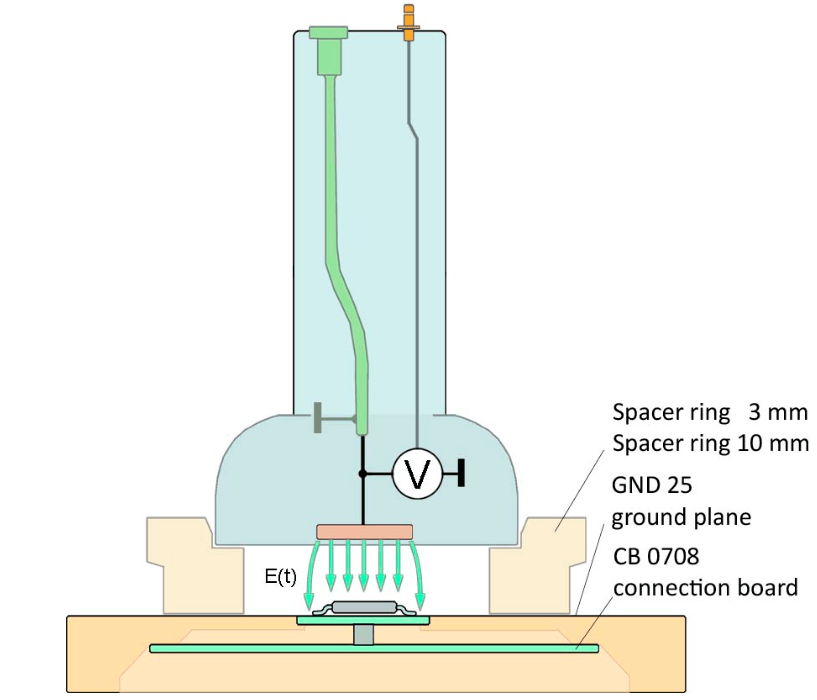

AEC-Q200-002HBM的ESD测试电路及放电电流波形如图1、图2所示。

(i)开关2为断开状态,开关1闭合,施加高压电源,充电用电容器(Cd)存储电量。

(ii)开关1断开,开关2闭合,电对测试对象电容器(Cx)施加Cd存储的电量,进行测试。

※Cx:测试对象电容器 Cd:充电用电容器 Rd:放电用电阻 Rc:保护电阻

图1.HBM的ESD测试电路

图2.放电电流波形

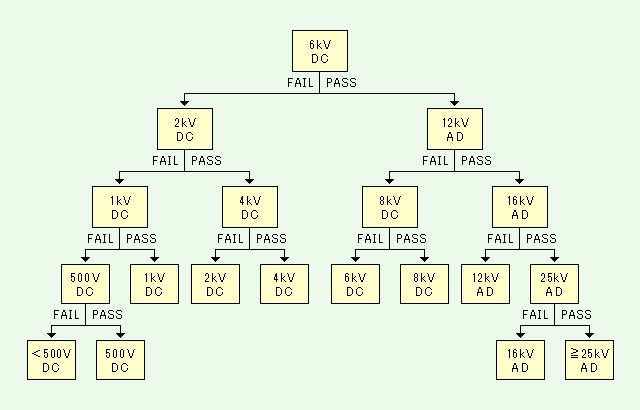

根据AEC-Q200-002,HBM的ESD测试流程如图3所示,级分类如表1所示。根据图3的流程进行测试,耐电压的分级如表1所示进行分类。

图3.HBM的ESD测试流程

表1.HBM的ESD测试流程

电容器静电容量与ESD耐性的关系

测试对象电容器的静电容量对电容器两端产生的电压有影响。

图4.HBM的ESD测试电路

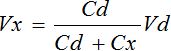

测试对象电容器的静电容量(Cx)和两端产生的电压(Vx)有如下关系。

电源电压(Vd)及充电用电容器的静电容量(Cd)恒定时,测试对象电容器的静电容量(Cx)越大,测试对象电容器两端产生的电压(Vx)越小。

因此一般的测试对象电容器静电容量越大,ESD耐性有变大的趋势。

实际上,如电介质的种类及厚度之类的设计上的差异,耐电压的性能范围也有不同,并非所有的都如上述的趋势一样。

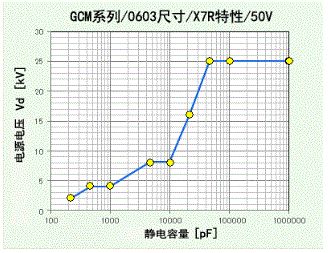

(参考数据)多层陶瓷电容器(GCM系列)的ESD耐性

展示了多层陶瓷电容器(GCM系列)的ESD耐性参考数据。

图5. 高介电常数型电容器的ESD测试结果(Vd=25kV为测量范围)

-

电容器

+关注

关注

64文章

6945浏览量

106613 -

ESD

+关注

关注

50文章

2375浏览量

178861 -

静电

+关注

关注

2文章

546浏览量

38014

原文标题:【工程师必看】一文了解电容器的ESD耐性

文章出处:【微信号:murata-eetrend,微信公众号:murata-eetrend】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

ESD测试的详细解释

基于JEDEC标准的闩锁效应测试方法

为什么 ESD 测试能过,但实际应用还是被击坏?

浪涌测试、脉冲群测试、ESD测试的对比

半导体芯片的ESD静电防护:原理、测试方法与保护电路设计

浅谈静电放电(ESD)测试

三星电子成功研发量子耐性安全芯片S3SSE2A 应对未来网络安全挑战

用ADS7830做一个按键检测,做3KV ESD测试时,ESD信号打到外壳的地时,ADS7830会锁死,怎么解决?

集成电路电磁兼容性及应对措施相关分析(三)集成电路ESD 测试与分析

集成电路电磁兼容性及应对措施相关分析(三)—集成电路ESD 测试与分析

ESD耐性的测试方法耐性

ESD耐性的测试方法耐性

评论