背景Linux会把进程分为普通进程和实时进程,普通进程采用CFS之类调度算法,而实时进程则是采用SCHED_FIFO或SCHED_RR。无论优先级高低,实时进程都会优先于SCHED_NORMAL中的所有进程先执行,因为后者里面都是普通的非实时进程。

具体可以参看Linux阅码场早期文章: 宋宝华:关于Linux进程优先级数字混乱的彻底澄清

内核线程的优先级Linux内核会将大量(并且在不断增加中)工作放置在内核线程中,这些线程是在内核地址空间中运行的特殊进程。大多数内核线程运行在SCHED_NORMAL类中,必须与普通用户空间进程争夺CPU时间。但是有一些内核线程它的开发者们认为它们非常特殊,应该比用户空间进程要有更高优先级。因此也会把这些内核线程放到SCHED_FIFO中去。

那么问题来了,某个内核线程的实时优先级到底该设为多少呢?

要回答这个问题,不仅需要判断这个线程相对于所有其他实时线程是否更加重要,还要跟用户态的实时进程比较谁更重要。这是一个很难回答的问题,更何况在不同的系统和工作模式下这个答案很有可能还会各不相同。所以一般来说,内核开发人员也就是看心情直接随便选一个实时优先级。

现在的一些内核实时线程如下:

最近大神Peter Zijlstra又看到有内核开发者随便给内核线程设置优先级,终于看不下去了, 指责这种把内核线程放入SCHED_FIFO的做法毫无意义:

“the kernel has no clue what actual priority it should use for various things, so it is useless (or worse, counter productive) to even try”

所以他发了一个系列[PATCH 00/23] sched: Remove FIFO priorities from modules 把设置内核线程优先级的接口干脆都给删了,省得再有人瞎搞。

这个系列Patch(点击阅读原文可直达)主要做了下面几件事情:

删除了原有的sched_setschedule() / sched_setattr() 接口

增加了

sched_set_fifo(p)

sched_set_fifo_low(p)

sched_set_normal(p, nice)

其中调用sched_set_fifo()会将指定进程放到SCHED_FIFO类中,其优先级为50——这只是min和max之间的一半位置。

对于需求不那么迫切的线程,sched_set_fifo_low()将优先级设置为最低值(1)。

而调用sched_set_normal()会将线程返回给定好的值SCHED_NORMAL类。

通过只留下这三个接口可以避免开发者们再不停地去随机选取内核线程优先级,因为这样本来毫无意义,当然如果需要的话系统管理员还是可以按需调整不同进/线程的优先级。

到目前为止,这个系列Patch已经有不少得到Reviewed-by,相信如果合入后,内核线程混乱的优先级状况会得到持续改善。

责任编辑:pj

-

内核

+关注

关注

4文章

1475浏览量

43089 -

Linux

+关注

关注

88文章

11814浏览量

219527

发布评论请先 登录

【瑞萨FPB-RA6E2试用】线程+PWM+串口通信

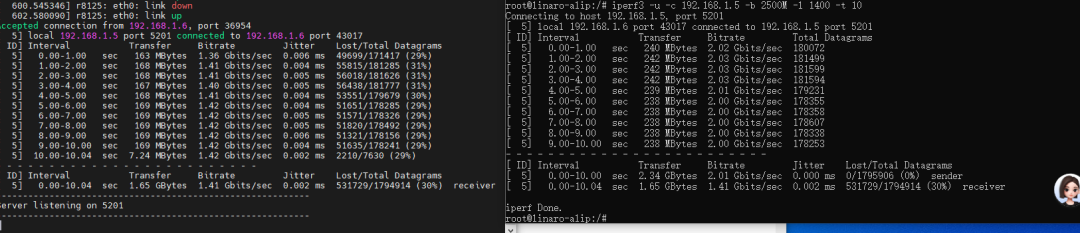

内核配置项引发网络性能下降的深度剖析

【瑞萨FPB-RA6E2试用】【瑞萨FPB-RA6E2】RTOS(Real-Time Operating System,实时操作系统)《线程》个人理解及项目实现

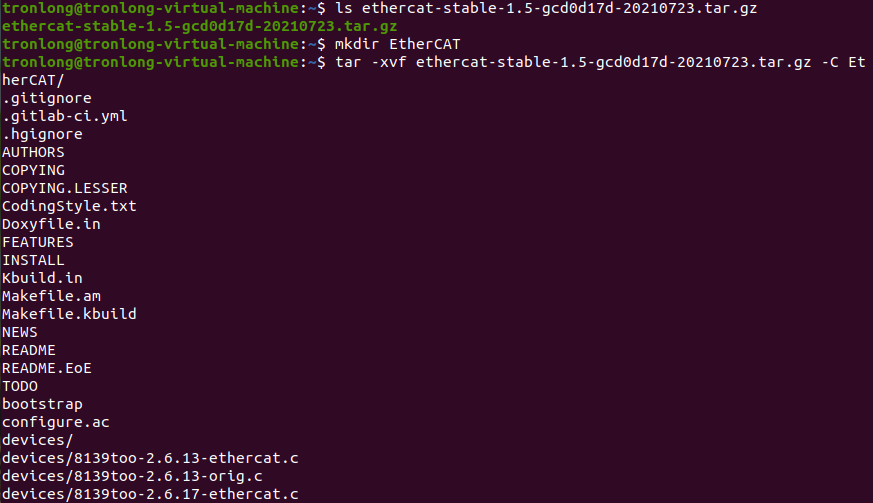

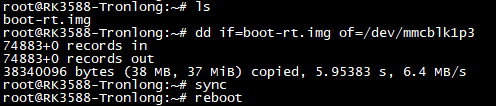

DR1M90 开源 IgH EtherCAT 主站案例:伺服电机正反转实时控制方案

三防漆哪种好?别再问了!记住这个选型逻辑,比品牌更重要

UPS电源价格/报价全解析:告别迷茫,一文读懂预算该怎么花

Linux-RT特点及简单应用

【飞凌OK153-S开发板评测】系统实时性及codesys测试

【飞凌OK-T153 开发板试用】实时性测试

创龙 瑞芯微 RK3588 国产2.4GHz八核 工业开发板—IgH EtherCAT主站开发案例(下)

创龙 瑞芯微 RK3588 国产2.4GHz八核 工业开发板—IgH EtherCAT主站开发案例(上)

线程超时函数中 assert 失败是什么原因导致的?

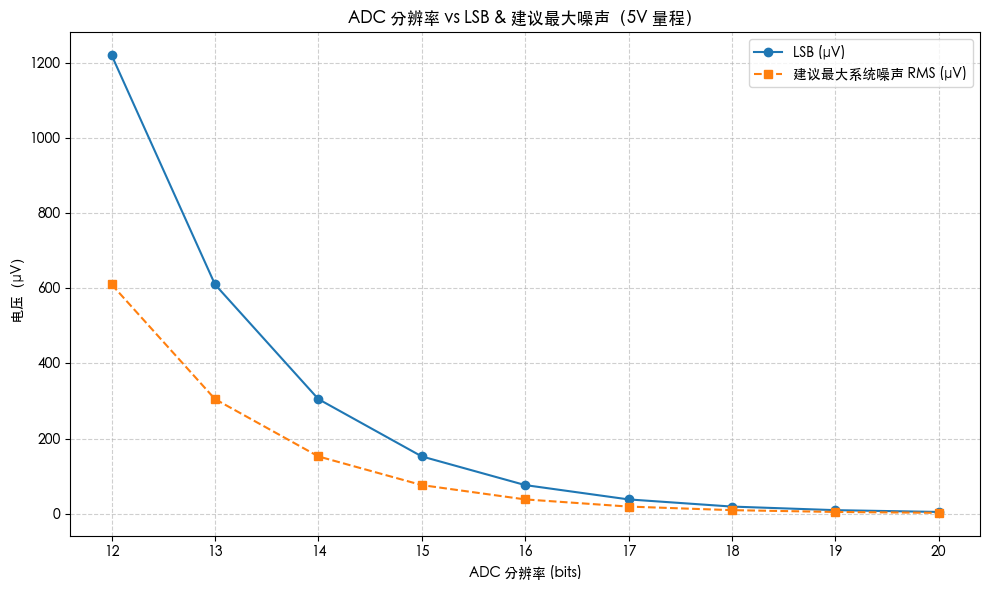

分辨率 vs 噪声 —— ADC的挑战

大牛多年研发电源问题汇总(受益匪浅)

智多晶FIFO_Generator IP介绍

为什么说内核线程放入SCHED_FIFO的做法毫无意义?

为什么说内核线程放入SCHED_FIFO的做法毫无意义?

评论