Verilog HDL简称Verilog,它是使用最广泛的硬件描述语言。

诞生时间:1983年。

可以分为5个层次:(自顶向下)

第一层,系统级(system):用高级语言设计模块的外部性能的模型

第二层,算法级(Algorithmic):用高级语言实现设计算法的模型

第三层,寄存器传输级(RTL):描述数据在寄存器之间的流动以及如何处理这些数据的模型。这是其他高级语言不具备的能力

第四层,门级(gate-level):描述逻辑门以及逻辑门之间的连接的模型

第五层,开关级(switch-level):描述器件中三极管和存储节点以及它们之间连接的模型

注:前三层属于行为级,第四层属于逻辑级,第五层属于开关级

Verilog的特点:

1. 它与C语言相似,语法灵活

2. 能够抽象出电路行为和结构

3. 支持逻辑设计中层次与范围的描述

4. 具有电路仿真和验证机制

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog

+关注

关注

31文章

1374浏览量

114726

发布评论请先 登录

相关推荐

热点推荐

商汤科技NEO-unify如何打造原生视觉语言理解与生成

当前,多模态模型普遍采用“视觉编码器(VE)用于理解,变分自编码器(VAE)用于生成”的组合式设计。这套范式虽行之有效,却也内在割裂了感知与创造,常面临模块协同与效率权衡的挑战。

Verilog HDL语法学习笔记

Verilog HDL 语 言 最 初 是 作为 Gateway Design Automation 公 司 ( Gateway DesignAutomation 公司后来被著名的 Cadence Design Systems 公司收购)模拟器产品开发的硬件建模语言。

FPGA 入门必看:Verilog 与 VHDL 编程基础解析!

很多开发者第一次接触FPGA,都会有同样的疑问:FPGA是硬件,不是软件,怎么写程序?答案就是用硬件描述语言(HDL),最常用的就是Verilog和VHDL。今天,我们就带你入门,搞清楚FPGA编程

C语言特性

的执行效率和资源利用率有着严苛的要求。C 语言生成的代码简洁紧凑,能够在有限的硬件条件下快速运行,满足嵌入式系统对性能的高要求。例如,在智能家居设备的控制芯片中,C 语言编写的程序可以高效地处理传感器

发表于 11-24 07:01

【产品介绍】Modelsim:HDL语言仿真软件

概述ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术、和单一内核

使用NucleiStudio生成tb仿真需要的.verilog文件

打开仿真顶层文件tb_top.v,存放在ITCM模块里面的指令是通过readmemh函数读入.verilog文件实现的:

下面通过对NucleiStudio IDE进行设置,实现将c

发表于 11-05 07:07

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

本篇将详细介绍如何利用Verilog HDL在FPGA上实现SRAM的读写测试。SRAM是一种非易失性存储器,具有高速读取和写入的特点。在FPGA中实现SRAM读写测试,包括设计SRAM接口模块

CICC2033:关于C语言仿真的一些说明

C语言运行说明

操作说明(以helloworld为例)

1、在SDK环境下写好C语言相关代码。

最简单的写法为根据已有demo进行更改。如果说需要重新创建新的SDK项目,具体写法可以参考官

发表于 10-21 14:18

为什么我选择VHDL入门

篇。 从长期来看,两个语言大概率都要学一下;但是从初学角度而言,总要选择一个入门语言。 根据网上的信息,总结对比结论: Verilog 的优势: 1. Verilog 语法接近C,学习

verilog模块的调用、任务和函数

在做模块划分时,通常会出现这种情形,某个大的模块中包含了一个或多个功能子模块,verilog是通过模块调用或称为模块实例化的方式来实现这些子模块与高层模块的连接的.

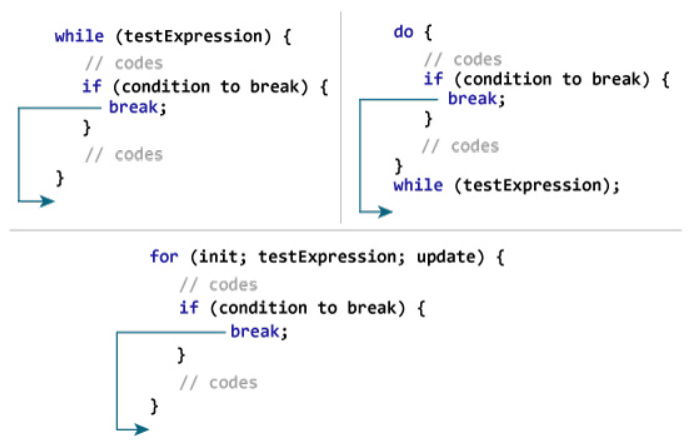

深入理解C语言:C语言循环控制

在C语言编程中,循环结构是至关重要的,它可以让程序重复执行特定的代码块,从而提高编程效率。然而,为了避免程序进入无限循环,C语言提供了多种循环控制语句,如break、continue和goto,用于

快速理解Verilog语言

快速理解Verilog语言

评论