近年来,在半导体行业,极紫外光刻(Extreme Ultra-Violet,以下简称EUV光刻)成为备受众多企业关注的光刻技术之一。

前段时间,***积体电路制造股份有限公司宣布,已采用7纳米EUV工艺。今年,三星公司正式发布了7纳米EUV芯片Exynos 9825,该公司称此芯片将晶体管性能提高了20%至30%,将功耗降低了30%至50%。

之所以备受关注,一个重要的原因是,有传闻称,EUV光刻有望成为摩尔定律的“救星”。

半个多世纪以来,半导体行业按照摩尔定律不断发展,由此驱动了一系列的科技创新。随着芯片尺寸越来越逼近物理极限,摩尔定律在未来是否依旧奏效,成为现在全行业都在关注的问题。

那么,这项技术能否为摩尔定律“续命”?它又是否已经到了最好的应用节点?针对上述问题,科技日报记者采访了业内专家。

将电路图和电子元件“刻”到“底片”上

在认识EUV光刻前,让我们先来认识一下光刻技术。

“其实,光刻技术跟照相技术差不多,照相是将镜头里的图画‘印’到底片上,而光刻是将电路图和电子元件‘刻’到‘底片’上。”北京理工大学材料学院副研究员常帅在接受科技日报记者采访时介绍道,在光刻工艺中,通常以涂满光敏胶的硅片作为“底片”,电路图案经光刻机,缩微投射到“底片”上。制造芯片,要重复几十遍这个过程。

“光刻技术的主要作用,就是把芯片上的线路与功能区做出来。”曾在半导体行业工作多年的北京理工大学材料学院博士生孟令海对科技日报记者表示,利用光刻机发出的光,通过带有图形的光罩,对涂有光刻胶的薄片进行曝光,光刻胶见光后会发生化学反应,从而使光罩上的图形印到薄片上,线路和功能区随之显现。

常帅表示,在芯片加工过程中,光刻是其中一个重要的步骤,其甚至被认为是集成电路制造中最为关键的步骤,决定着制造工艺的先进程度。

摩尔定律指出,芯片上可容纳的元器件数目每隔18个月翻1倍,同时芯片性能每隔18个月提高一倍,而价格下降一半。

“光刻技术的‘雕刻’精细度,直接决定了元器件、电路等在芯片上所占的体积。因而,光刻是决定芯片能否按照摩尔定律继续发展的一项重要技术,如果没有光刻技术的进步,芯片制造工艺就不可能从微米进入深亚微米再进入纳米时代。”常帅说。

孟令海向记者说,随着芯片制造工艺由微米级向纳米级发展,光刻机所采用的光波波长也从近紫外(NUV)区间的436纳米、365纳米,进入深紫外(DUV)区间的248纳米、193纳米。

EUV光源波长为主流光源的1/14

EUV光刻所用的光波,是波长为13.5纳米的极紫外光。相比当前主流光刻机所采用的193纳米光源,EUV光源的波长约为前者的1/14,这使其能在硅片上“刻”出更细的痕迹。

“业内形容EUV光刻的精细程度,常打的一个比方是,好比从地球上射出的一缕手电筒光,其能精准地照到月球上的一枚硬币。”孟令海说。

为满足摩尔定律的要求,技术人员一直在研究、开发新的芯片制造技术,来缩小线宽并增大芯片的容量。“线宽是指芯片上最小导线的宽度,是衡量芯片制作工艺先进性的重要指标之一。”常帅说。

“如今,芯片制造商大多使用波长为193纳米的光刻技术,用其在‘底片’上‘描绘’出精细的图案。但实际上,193纳米光刻目前已经达到了技术极限,只能支持80纳米的线宽工艺,无法在芯片上实现更小线宽。”常帅说,由于光源更细,EUV光刻技术可以满足22纳米及更小线宽的集成电路生产要求。

“可以说,EUV是目前距离实际生产最近的一种深亚微米光刻技术。如果采用该光刻技术,可在芯片上实现10纳米以内的线宽。”孟令海说。

摩尔定律不只对性能提出要求,另一个要求是成本的降低。所以,“救星”还必须承担起省钱的重任。EUV光刻技术恰好能符合这个要求。

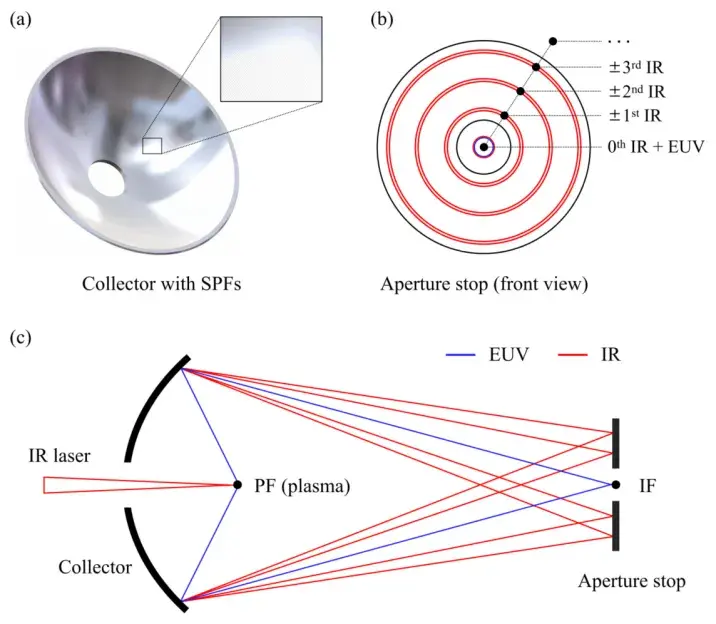

常帅介绍道,光刻机在工作过程中,要频繁地进行曝光。简单来说,就是用光线照射硅片,让未受掩模遮挡部分的光刻胶发生化学反应,这样才能将石英掩模上的电路图显影到硅片上,以便后续进行刻蚀、去胶等一系列工序。

“目前,主流制造商生产1枚芯片,可能需要进行4次,甚至更多次的曝光。若采用EUV光刻技术,只需1次曝光就够了,这样就可大幅降低生产制造成本。”孟令海说,换句话说,EUV光刻技术不仅提升了刻录的精细程度,也能让芯片的价格更便宜,符合摩尔定律对成本的要求。

不仅如此,EUV光刻技术之所以受到各大集成电路生产厂商的关注,还因为该光刻技术是传统光刻技术的拓展,能使现有生产工艺得以延续。

让摩尔定律至少再延续10年

既然EUV光刻技术好处多多,这么看来,为摩尔定律“续命”的重任,可以放心交给它了。

然而,事实并非如此。

常帅和孟令海介绍,目前来看,EUV光刻技术进展比较缓慢。同时,极紫外光刻光学系统的设计和制造也极其复杂,尚存在许多未被解决的技术难题。

据孟令海分析,EUV光刻技术目前主要面临三大挑战。

“首先是光源效率,即每小时能‘刻’多少片,按照量产工艺要求,光刻效率要达到每小时250片,而现在EUV光刻效率尚难达到这一要求,因此还需进一步提高,但实现难度相当大。其次是光刻胶,EUV光刻机和普通光刻机的技术原理不同,普通光刻机采用投影进行光刻,而EUV光刻机则是利用反射光,需要借助反光镜,这使得光子和光刻胶的化学反应变得不可控,有时会出现差错。最后是光刻机保护层的透光材料,要提高光刻机的刻录精度,就需要在其上面增加一个保护层,但现有保护层材料质量欠佳、透光性比较差。”孟令海说。

此外,据常帅分析,EUV光刻工艺的良品率也是阻碍EUV光刻发展的“绊脚石”。目前,采用一般光刻机生产的芯片,其良品率约为95%,而EUV光刻机的良品率仅为70%至80%。

“要想解决这些问题,关键是要提升市场订单数量,只有订单多了,厂商用得多了,才能吸引更多光源、材料等上下游企业共同参与研发,进而完善EUV光刻产业链。”常帅说。

即使在技术上达到要求,收益缺乏足够的吸引力,也很难让制造企业产生应用新技术的动力。目前看来,采用EUV光刻技术的生产成本十分高昂。

资料显示,最新的EUV光刻机价格或超过1亿欧元,是常规193纳米光刻机价格的2倍多。此外,由于功率极高,EUV光刻设备在生产时消耗的电量也远超现有同类机器。

那么,目前来看,EUV光刻技术能为摩尔定律的延续,起到哪些作用呢?

孟令海表示,在光刻线条宽度为5纳米及以下生产工艺中,EUV光刻技术具有不可替代性,在未来较长一段时间内,EUV光刻技术都可能成为延续摩尔定律发展的重要力量。“因此,如果解决了工艺技术和制造成本等难题,EUV光刻设备将是7纳米以下工艺的最佳选择,它可让摩尔定律至少再延续10年时间。”孟令海说。

-

半导体

+关注

关注

339文章

31241浏览量

266587 -

摩尔定律

+关注

关注

4文章

640浏览量

81153 -

EUV

+关注

关注

8文章

615浏览量

88960

发布评论请先 登录

中国打造自己的EUV光刻胶标准!

俄罗斯亮剑:公布EUV光刻机路线图,挑战ASML霸主地位?

长电科技邀您相约SEMICON CHINA 2026

垄断 EUV 光刻机之后,阿斯麦剑指先进封装

白光干涉仪在EUV光刻后的3D轮廓测量

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

当摩尔定律 “踩刹车” ,三星 、AP、普迪飞共话半导体制造新变革新机遇

EUV光刻胶材料取得重要进展

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

中科院微电子所突破 EUV 光刻技术瓶颈

晶心科技:摩尔定律放缓,RISC-V在高性能计算的重要性突显

ASML杯光刻「芯 」势力知识挑战赛正式启动

跨越摩尔定律,新思科技掩膜方案凭何改写3nm以下芯片游戏规则

电力电子中的“摩尔定律”(1)

EUV光刻有望成为摩尔定律的“救星”?

EUV光刻有望成为摩尔定律的“救星”?

评论