Intel的联合创始人戈登·摩尔是半导体业界黄金定律“摩尔定律”的提出者,Intel公司50多年来也是这一定律最坚定的捍卫者。但是这几年来,Intel自己反而在制程工艺上掉队了,甚至被小兄弟AMD用7nm超越了,今年的场面一度十分尴尬。

不过AMD对工艺赶超Intel一事也很意外,而且他们很清楚地知道Intel公司会搞定眼前的困难的,CPU架构及工艺上绝不可能轻敌,Intel现在只是在进度上落后了,并不代表他们没技术。

日前Intel也给自己的2019年做了一个总结,其中多次提到了摩尔定律及自家的工艺进展。Intel指出2019年他们供应了更多的芯片以满足市场需求,其中10nm工艺的就有Ice Lake及Agilex FPGA两款产品进入了HVM大规模量产阶段。

此外,Intel还重申他们在未来会重新回到2年一个周期的工艺升级路线上来,7nm工艺将在2021年推出,目前进展顺利,而5nm工艺研发也已经开始,这些先进的工艺将使得晶体管越来越小,集成度更高。

不过Intel依然没有公布7nm及5nm工艺的具体细节,我们现在知道的是7nm会是Intel首个使用EUV光刻技术的工艺,2021年首发于7nm Xe架构的数据中心芯片Ponte Vecchio,至于5nm工艺的进度及技术就欠奉了。

对Intel来说,2021年倒是好期待,但是难题在于2020年,10nm芯片今年只是出货了面向移动市场的低功耗版Ice Lake,高性能版的桌面版、服务器版Ice Lake要到明年下半年,在这之前14nm处理器还要再维持一两代。

责任编辑:wv

-

cpu

+关注

关注

68文章

11332浏览量

225933 -

intel

+关注

关注

19文章

3511浏览量

191658

发布评论请先 登录

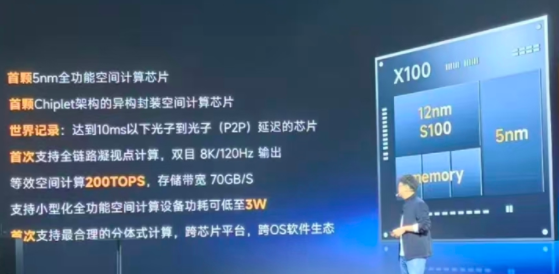

芯擎科技“龍鹰二号”:5nm舱驾融合芯片开启智能汽车AI新纪元

Coreless无芯工艺与ETS埋线路工艺的差异比对

数控车削加工工艺分析要点

SMT工艺革新:高精度贴装与微型化组装的未来趋势

0.2nm工艺节点的背后需要“背面供电”支撑

1600TOPS!美国新势力车企自研5nm芯片,转用激光雷达硬刚特斯拉

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

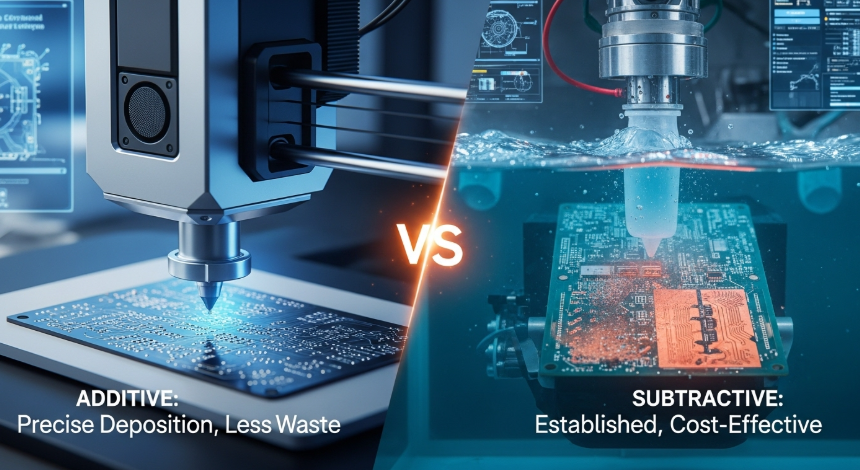

PCB工艺路线详解:加成法 vs 减成法,一文读懂核心差异与未来趋势

【「AI芯片:科技探索与AGI愿景」阅读体验】+工艺创新将继续维持着摩尔神话

三星代工大变革:2nm全力冲刺,1.4nm量产延迟至2029年

SMA接头创新设计:材料、工艺与功能升级

Intel重申未来将重新回到2年一个周期的工艺升级路线 5nm工艺研发也已经开始

Intel重申未来将重新回到2年一个周期的工艺升级路线 5nm工艺研发也已经开始

评论