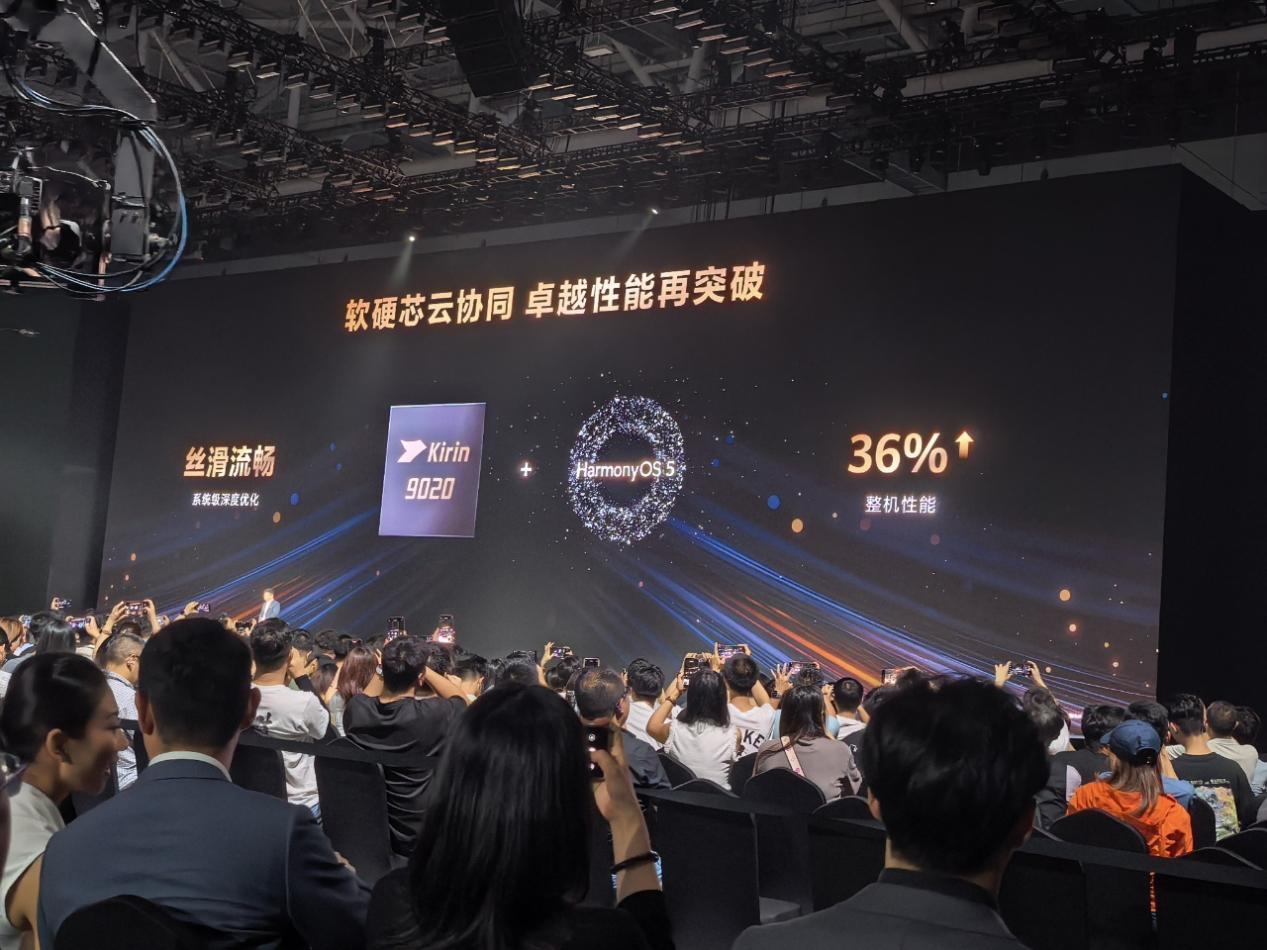

据消息,目前台积电正在积极备战5nm,华为已经在考虑将5nm工艺用在其下一代旗舰芯片——麒麟1020上,预计明年第三季度上市。

报道中称,华为麒麟1020将采用ARM Cortex-A78架构,得益于5nm工艺,麒麟1020每平方毫米可容纳1.713亿个晶体管,其性能较麒麟990提升50%,而高通骁龙865较前代骁龙855性能只提升了25%。

此外,苹果A14处理器和麒麟1020处理器将是首批使用5nm工艺的旗舰芯片,而高通系的5nm芯片则要到2021年才能量产。

责任编辑:gt

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

台积电

+关注

关注

44文章

5812浏览量

177081 -

华为

+关注

关注

218文章

36212浏览量

262714 -

晶体管

+关注

关注

78文章

10443浏览量

148687

发布评论请先 登录

相关推荐

热点推荐

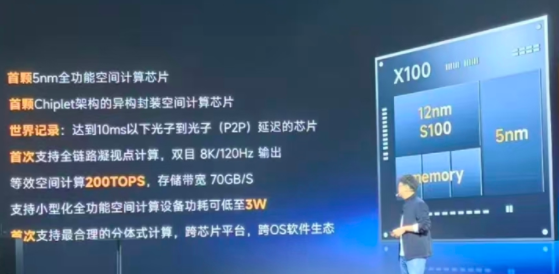

芯擎科技“龍鹰二号”:5nm舱驾融合芯片开启智能汽车AI新纪元

2026年4月25日,芯擎科技正式发布其新一代车规级舱驾融合芯片“龍鹰二号”。这款采用5nm先进制程工艺打造的芯片,以200 TOPS的算力峰值和7B大模型支持能力,直指AI舱驾融合市

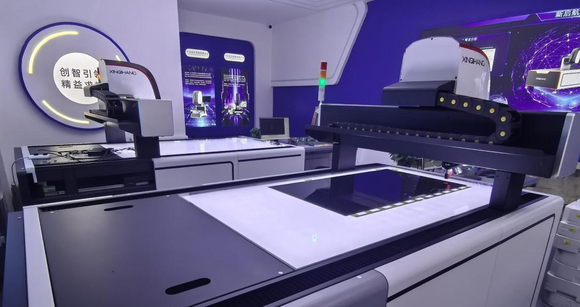

LCD液晶面板激光修复工艺助力制程良率提升

一、引言 LCD液晶面板作为显示产业的核心组件,其制程涵盖阵列、成盒、模组组装等多个复杂环节,任一环节的微小缺陷都可能导致面板失效。当前,线路短路/开路、坏点、暗带等制程缺陷是制约LCD面板良率

晶圆工艺制程清洗方法

晶圆工艺制程清洗是半导体制造的核心环节,直接决定芯片良率与器件性能,需针对不同污染物(颗粒、有机物、金属离子、氧化物)和制程需求,采用物理、化学、干法、复合等多类技术,适配从成熟

如何突破AI存储墙?深度解析ONFI 6.0高速接口与Chiplet解耦架构

6.0)支撑高性能 PCIe 5.0 SSD 存取

工艺覆盖全制程 (包含 5nm, 8nm, 12

发表于 01-29 17:32

三星2nm良率提升至50%,2027年前实现晶圆代工业务盈利可期

据报道,三星电子第一代2nm GAA制程(SF2)良率已稳定在50%,该数据也通过其量产的Exynos 2600处理器得到印证。

1.4nm制程工艺!台积电公布量产时间表

供应一度面临紧张局面。为应对市场激增的订单,台积电已启动新建三座工厂的扩产计划,旨在进一步提升产能,保障客户供应链的稳定交付。 与此同时,台积电在更尖端的1.4nm工艺研发上同样进展迅猛。公司正全力加速推进1.4

三星发布Exynos 2600,全球首款2nm SoC,NPU性能提升113%

)技术。相较于传统的3nm FinFET工艺,GAA架构提供了更出色的静电控制和更高的电流密度,使芯片性能提升12%,功

麒麟系统适配飞腾D3000+S50:信创终端的“性能革命”来了?

处理器,搭配摩尔线程MTTS50国产全功能GPU,已在银河麒麟V10等系统上完成多项实测验证,展现出卓越的协同能力与应用潜力 · 高性能计算 :飞腾D3000集成8个自研FTC862内核,主频高达2.5GHz,在多核

国产芯片真的 “稳” 了?这家企业的 14nm 制程,已经悄悄渗透到这些行业…

最近扒了扒国产芯片的进展,发现中芯国际(官网链接:https://www.smics.com)的 14nm FinFET 制程已经不是 “实验室技术” 了 —— 从消费电子的中端处理器,到汽车电子

发表于 11-25 21:03

【「AI芯片:科技探索与AGI愿景」阅读体验】+工艺创新将继续维持着摩尔神话

个先例,其变化形式如图6所示。

晶背供电技术已被证明,它可以很好地解决5nm以下芯片的电源完整性问题,同样也证明

它是优化特定版图设计任务的用力工具。

图6 功能性晶

随着工艺创新的层出不穷,相信摩尔神话还能持续,AI芯片也将为

发表于 09-06 10:37

从Ascend 910D看芯粒创新,半导体行业将迎重大变局

电子发烧友网报道(文/黄山明) 随着芯片制程工艺向更先进节点推进,如从7nm迈向5nm,再到3nm,物理层面的技术瓶颈愈发凸显,这使得行业在

快手上线鸿蒙应用高性能解决方案:数据反序列化性能提升90%

近日,快手在Gitee平台上线了鸿蒙应用性能优化解决方案“QuickTransformer”,该方案针对鸿蒙应用开发中广泛使用的三方库“class-transformer”进行了深度优化,有效提升

发表于 05-15 10:01

华为麒麟1020加入5nm工艺制程,其性能将提升50%

华为麒麟1020加入5nm工艺制程,其性能将提升50%

评论