晶圆代工的工艺节点有许多,做选择的主观因素是基于IC设计公司对于工艺和市场的判断,而客观因素,则是龙头代工企业的产能问题。

目前市面上的高端手机处理器中,除了三星的Exynos芯片之外,几乎全都采用台积电的7nm或其衍生工艺制成,这直接让台积电市值飙升到了2849.23亿美元,一举超过三星成为了亚洲最有价值的公司。

台积电第三季度财报显示,7nm营收占比高达27%,台积电今年新增的2%产能也全投在了这一节点,预计7nm年产能规模高达100万片。尽管如此,台积电还是低估了今年的晶圆代工市场,第四季度7nm产能接单全满,明年上半年也供不应求,甚至连16nm、12nm以及10nm也开始陷入产能不足的境地。

越来越细分的工艺节点

随着半导体工艺不断演进,摩尔定律已经很难去完美的遵循。于是乎,各种过渡工艺成为了代工厂的法宝。在台积电的原始7nm(N7)和5nm(N5)之间,就有N7P、N7+和6nm(N6)三种选择,而N5也有一个增强版本N5P,如此细分的工艺节点,究竟在性能上有多大的区分呢?

根据集微网此前报道,N7P 与 N7 的设计规则相同,晶体管密度没有增加,但新工艺优化了前端(FEOL)和中端(MOL)制程,可在相同功率下将性能提升7%、或在同频下降低10%的功耗。

N7+引进了ASML的EUV设备,并使用了5层的EUV光罩层。相较于N7工艺,N7+可以将晶体管密度提升了20%,同等功耗水平下能够提供10%的性能增幅,或者同性能节省15%的功耗。

N6虽然比N5低一个版本,但该节点的量产时间预计比N5还要晚。N6是N7的EUV等效工艺,其使用的EUV光罩层比N7+要多,而且兼容于N7,从而能让大部分N7客户更容易升级到这一节点。相比于N7,N6晶体管密度提升45%,可带来15%的性能提升或20%的功耗下降。

N5是台积电明年的重头戏,目前已知仅有华为和苹果将会倒入这一最先进的节点。该节点将全面使用EUV工艺(14-15层),相较于N7节点, N5的晶体管密度大增80%,并带来同功耗15%的性能提升或者同性能30%的节能。

N5P工艺作为N5的进阶版,在基础上采取了FEOL 和 MOL 优化。相比于N5,N5P能让芯片在相同功率下提升7%的性能,或在同频下降低15%的功耗。

均以N7为基准,通过上表不难看出,台积电这些细分节点每一代之间的区别并不大。所以,作为手机CPU厂商来说,最先进的工艺不一定是最好的选择。市场消息透露,N7+流片费用为2.1亿人民币,而N5全光罩流片费用更高达3亿人民币,在这些细分工艺之间的升级同样意味着高昂的成本,芯片厂商需要充分考虑个中商业因素。

芯片厂商的主观抉择

华为麒麟990系列的工艺选择很好理解,5G版本集成的5G基带会占用很多的晶体管,因此选择了目前最优的N7+工艺,而4G版本在GPU和NPU大幅优化过后,N7足矣。

而关于高通刚刚发布的骁龙865,外界存在诸多疑问,例如“为何不用EUV工艺?”、“为什么不找三星代工?”。集微网记者从第四届高通骁龙技术峰会上获悉,高通选择台积电的N7P来代工骁龙865,一方面更符合商业利益,另一方面能让供应链更多样化,因为同时推出的骁龙765/765G是由三星7nm代工。

值得一提的是,骁龙865的“5G伴侣”骁龙X55基带同样是采用了台积电的N7P工艺,由于X55大概率将会被下一代5G iPhone采用,业内人士@手机晶片达人 透露,原本高通也打算在三星代工骁龙X55,但苹果方面表示仅会使用台积电生产的骁龙X55。

最后,关于不支持5G的苹果A13和联发科的业界第一颗5G SoC “天玑1000”。前者因为不支持5G,退而求其次选择N7P工艺,合情合理。那么集成了5G基带的“天玑1000”为何只使用了台积电N7工艺呢?

据了解, “天玑1000”采用了主频高达2.6GHz的4个ARM Cortex-A77大核,而A77架构的性能相比上一代的A76架构提升了20%。GPU也采用了最新的ARM Mali-G77 MC9,相比上一代的Mali-G77提升了40%。

有了A77和G77这样的左膀右臂,联发科或许认为N7足矣。更重要的是,N7与N6兼容,联发科作为第一个试水5G SoC的芯片厂商,一旦采用N7的天玑1000带来了不错的营收,那么在衍生版本中平滑的升级到N6将会帮助联发科进一步扩大优势。

客观因素导致群雄逐“产”

各大手机厂商对于工艺节点的选择,还受到一个重要的客观因素影响,那就是台积电的产能问题。据了解,台积电今年N7+的产能十分稀缺,很难满足大客户的批量生产,所以只有麒麟990系列的5G版本采用了该工艺。

所以,对于台积电而言,加购EUV机台刻不容缓。因为N7之后的每一个工艺节点都需要用到EUV设备,而EUV设备的年产量十分有限,2018年总产量仅有22台,今年虽然增加了产能,但预计也只有30台左右。

其次,7nm和5nm的扩产必须双管齐下。此前,台积电大幅上调了今年的资本开支,从原定110亿美元增加到了140-150亿美元,增幅超过40%,其中有25亿美元用于5nm工艺扩产,剩余用于先进工艺研发和其他工艺产能扩充。根据台积电的规划,5nm工艺首先在南科Fab 18工厂一期量产,明年Q3机电室产能达到5.5万片晶圆/月,Fab 18工厂的二期工程也规划了5.5万片晶圆/月的产能。

相比于5nm,台积电7nm产能紧张的形势更为严峻。因为5nm目前已知仅有华为海思和苹果这两大客户,而在7nm方面,明年台积电不仅有联发科、高通这两个手机处理器大单,还有来自电脑CPU和GPU方面的AMD、挖矿机芯片方面的比特大陆抢夺产能,虽然苹果和华为旗舰芯片转向5nm能够空置出许多7nm产能,但还需要考虑到各类中低端5G手机也将逐渐会跟进到7nm节点。

可预期的时间内,市场需求将始终超过台积电的产能水平。

2020年将迎来5G手机的第一波爆发,手机芯片巨头群雄逐鹿的好戏一触即发,而这“鹿”的其中一面,则将会是台积电的产能。

-

台积电

+关注

关注

44文章

5812浏览量

177105 -

晶圆

+关注

关注

53文章

5451浏览量

132788 -

5G

+关注

关注

1368文章

49229浏览量

641423

发布评论请先 登录

85页PPT,看懂芯片半导体的封装工艺!

中达瑞和VIX-N220推扫式高光谱相机:助力中医舌苔面诊迈向客观化、智能化新时代

0.2nm工艺节点的背后需要“背面供电”支撑

BMS设计中如何选择MOSFET——关键考虑因素与最佳实践

AI如何重塑模拟和数字芯片工艺节点迁移

如何选择适合特定制程节点的清洗工艺

目前最先进的半导体工艺水平介绍

湿法刻蚀的主要影响因素一览

工艺与材料因素导致铜基板返修的常见问题

高精度半导体冷盘chiller在半导体工艺中的应用

半导体制冷机chiller在半导体工艺制程中的高精度温控应用解析

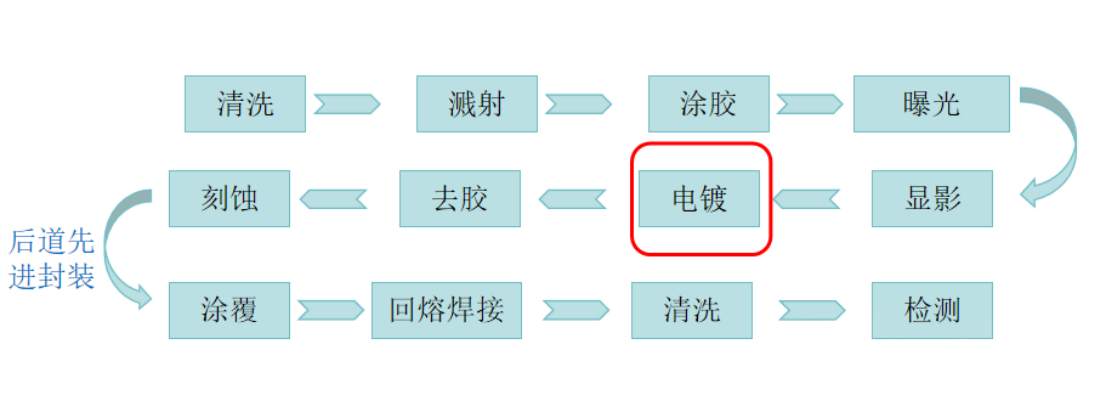

揭秘半导体电镀工艺

半导体工艺节点的主观因素和客观因素

半导体工艺节点的主观因素和客观因素

评论