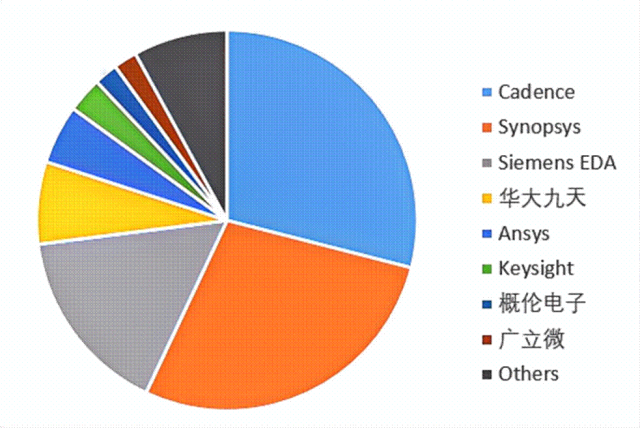

不久前,Cadence公司举办的CDNLive 2019大会将智能系统设计 (Intelligent System Design)战略设置为主题,智能系统设计的趋势涉及到芯片相关的软硬件设计,而要真正实现从芯片到系统的复杂设计和落地,EDA工具是基础,其中,面临很大挑战的是EM的3D仿真。

Cadence系统仿真事业部资深软件工程总监Jian Liu认为,对于大规模系统而言,EM的3D仿真首要解决的挑战是保证模型运算结果的精确度,此外还有仿真成本效益以及设计工具链资源的无缝对接。

Cadence多物理系统分析事业部产品总监Jerry Zhao表示,像汽车这类大规模的中心系统,不仅仅是电子场,也是多物理部件的耦合,其复杂度大大增加,并且高速并行的大规模数据传输也带来高频串扰的问题。这些都需要高速的软件工具来更精确地分析、模拟,然后优化。

一个典型的例子是112G SerDes的长距离信号传输。由于人工智能、机器学习和5G通信等应用对数据中心的以太网端口带宽提出了更高的要求,400G乃至800G以太网端口将成为主流,112G SerDes也将成为主流配置。去年底,Cadence曾发布长距离7nm 112G SerDes的IP,而目前FPGA中的顶配也都是112G SerDes。

Jian Liu表示,要保证信号在112G速率上没有误差的长距离传输——即所谓黄金标准——系统设计需要真正的整体的3D分析,但目前的3D建模工具都无法保证模型运算结果的精确度。因为目前主要的EM仿真受限于速度和处理能力制,会简化或将结构切分成更小的片段,以适应本地运行的计算资源,这种为了提高仿真效率而人为对结构进行剪切的伪3D方法会带来仿真精度降低的风险。

这实际上是一个成本效益的问题。硅基板、刚柔板和多Die堆叠的3D封装的高度复杂结构必须在3D环境精确建模,才能实现3D结构设计的优化和高速信号的稳定传输。因此,互连结构的优化必须进行数十次复杂结构的场提取和仿真,而为了满足这类工作负荷需求,传统的EM仿真程序必须运行在大型、昂贵的高性能服务器上,成本较高。

Cadence在今年4月份推出的Clarity 3D Solver解决了上述痛点。据Jian Liu介绍,作为Cadence系统分析战略的首款产品,Clarity 3D Solver的EM仿真性能比传统产品提高了10倍,提供了无限制的处理能力,改变了以往分析工具只能进行点分析的瓶颈,实现了分析与构建的集成,并且其仿真精度能够够达到黄金标准。

Clarity的这一特性为那些拥有桌面电脑、高性能计算或云计算资源的工程师提供了优化计算资源预算的选择,使得他们更容易地解决芯片、封装、PCB、接插件和电缆设计等复杂的3D结构设计中的EM挑战。Jerry Zhao表示,除了接受CloudBurst云平台——支持功能验证、电路仿真、库特性和验收工具——的支持,作为Cadence产品家族的一员,Clarity不仅可以读取所有标准芯片和IC封装平台的设计数据,也可以更容易地对接Cadence其他工具的资源,包括与Virtuoso、Cadence SiP和Allergro实现平台集成(在Allegro和Virtuoso环境下设计三维结构,在分析工具中优化后导回设计工具中,而无需重新绘制。);与Cadence Sigrity 3DWorkbench同时使用,可以将电缆和接插件等机械结构与系统设计结合,并将机电互连结构建模为单一的整体模型。

总的来看,Clarity 3D Solver体现了Cadence系统分析战略的特质,也反映出在大规模系统设计中,EDA工具作为基础设施所要解决的那些关键性问题的趋势。值得留意的是,Cadence已经成立了系统分析事业部,专门针对IC、封装、PCB和全系统设计中的问题提供解决方案,这意味着该公司的服务正在从芯片走向系统,这是一个更大的市场。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Cadence

+关注

关注

68文章

999浏览量

146203 -

eda

+关注

关注

72文章

3053浏览量

181508 -

Clarity

+关注

关注

0文章

4浏览量

9176

发布评论请先 登录

相关推荐

热点推荐

智多晶EDA工具HqFpga软件的主要重大进展

智多晶EDA工具HqFpga(简称HQ),是自主研发的一款系统级的设计套件,集成了Hqui主界面、工程界面、以及内嵌的HqInsight调试工具、IP Creator IP生成

硅芯科技:AI算力突破,新型堆叠EDA工具持续进化

电子发烧友网报道(文/黄晶晶)先进封装是突破算力危机的核心路径。2.5D/3D Chiplet异构集成可破解内存墙、功耗墙与面积墙,但面临多物理场分析、测试容错等EDA设计挑战。现有EDA

国产EDA又火了,那EDA+AI呢?国产EDA与AI融合发展现状探析

关键,AI 数据中心设计为复杂系统级工程,EDA 工具需从单芯片设计转向封装级、系统级协同优化,推动设计范式从 DTCO 升级至 STCO。 国际

开发无线通信系统所面临的设计挑战

的设计面临多种挑战。为了解决这些挑战,业界逐渐采用创新的技术解决方案,例如高效调变与编码技术、动态频谱管理、网状网络拓扑结构以及先进的加密通信协议。此外,模块化设计、可升级架构与边缘计算的结合,为

华大九天物理验证EDA工具Empyrean Argus助力芯片设计

在芯片设计的流片之路充满挑战,物理验证EDA工具无疑是这“最后一公里”关键且不可或缺的利器。它通过设计规则检查、版图与原理图一致性验证等关键流程,为IC设计契合制造需求提供坚实保障。作为签核(Signoff)环节的关键防线,物理

EDA是什么,有哪些方面

EDA(Electronic Design Automation,电子设计自动化)是一种基于计算机软件的电子系统设计技术,通过自动化工具和算法辅助完成电路设计、验证、制造等全流程。以下是EDA

发表于 06-23 07:59

九霄智能国产EDA工具的突围之路

近日,芯片行业因EDA工具「断供」事件再次被推到了舆论的风口浪尖。作为深耕数字EDA前端工具的从业者,我们亲历了行业从技术封锁初期的焦虑,到如今全产业链协同破局的蜕变。本文不聚焦短期博

各大厂商与新兴企业推出的 EDA Copilot 工具

当前EDA(电子设计自动化)领域正经历AI驱动的智能化转型,各大厂商与新兴企业推出的EDA Copilot工具通过自然语言交互、自动化设计优化等技术,显著提升芯片设计效率。以下是基于最

用一套Linux系统,撑起整个芯片设计平台?CFA团队教你如何搭好EDA智算平台的技术底座

在半导体行业,Linux 是我们再熟悉不过的操作系统。作为芯片研发者日常工作的主战场,它承载着EDA工具、AI训练环境、脚本自动化流程的运转。而随着AI和EDA算力技术的迅猛发展,我们

发表于 05-07 14:44

智慧路灯的推广面临哪些挑战?

引言 在智慧城市建设的宏伟蓝图中,叁仟智慧路灯的推广面临哪些挑战?叁仟智慧路灯作为重要的基础设施,承载着提升城市照明智能化水平、实现多功能集成服务的使命。然而,尽管叁仟智慧路灯前景广阔,在推广过程中

西门子EDA工具如何助力行业克服技术挑战

西门子EDA工具以其先进的技术和解决方案,在全球半导体设计领域扮演着举足轻重的角色。本文将从汽车IC、3D IC和EDA AI三个方向,深入探讨西门子EDA

EDA²侠客岛难题挑战·2025已正式开启

,打通EDA工具难题挑战、课题精研/学习、实验平台、领域交流论坛等多生态场景,与企业、高校等联手共享广阔资源。

2025赛题一览

赛题1:面向PPA的混合尺寸布局算法

价值阐述:

混合

发表于 03-05 21:30

芯华章持续助力EDA精英挑战赛

日前,2024中国研究生创“芯”大赛·EDA精英挑战赛(以下简称EDA竞赛)决赛在南京江北新区举办。今年EDA竞赛首次升级为国赛,在全国超过500个参赛队伍中,来自华南理工大学的"

智能系统设计 EDA工具面临新挑战

智能系统设计 EDA工具面临新挑战

评论