格芯指出,新开发出基于ARM架构的3D高密度测试芯片,是采用格芯的12纳米FinFET制程所制造,采用3D的ARM网状互连技术,允许资料更直接的传输到其他内核,极大化的降低延迟性。而这样的架构,这可以降低资料中心、边缘运算以及高端消费者应用程式的延迟,并且提升数据的传输速度。

格芯强调,新开发出基于ARM架构的3D高密度测试芯片,可以进一步在每平方公厘上达成多达100万个3D的连接,使其具有高度可扩展性,并有望延展12纳米制成的寿命。另外,3D封装解决方案(F2F)不仅为设计人员提供了异构逻辑和逻辑/存储器整合的途径,而且可以使用最佳生产节点制造,以达成更低的延迟、更高的频宽,更小芯片尺寸的目标。

格芯表示,因为当前的12纳米制程成熟稳定,因此目前在3D空间上开发芯片更加容易,而不必担心新一代7纳米制程所可能带来的问题。然而,台积电、三星和英特尔能够在比格芯小得多的节点上开发3D芯片,而且也已经相关的报告。而何时推出,就只是时间上的问题。届时,格芯是否能以较低廉的价格优势,进一步与其他晶圆生产厂商竞争,就有待后续的观察。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

463文章

54389浏览量

469054 -

3D封装

+关注

关注

9文章

149浏览量

28363 -

格芯

+关注

关注

2文章

242浏览量

27092

发布评论请先 登录

相关推荐

热点推荐

高密度配线架面板

高密度光纤配线架面板规格书一、产品概述高密度光纤配线架面板(ODF 单元 / 熔接盘)是专为数据中心、运营商机房、企业网络设计的光纤管理单元,用于实现光纤的熔接、端接、分配与保护,具备高集成度

发表于 04-17 22:29

•0次下载

深度解析3D眼镜电子电路设计难点与实践——YANTOK自主设计方案落地

进行3D眼镜电子电路自主设计时,需重点关注三大核心要点:

一是元器件选型要兼顾性能与功耗,优先选用低功耗、高稳定性的芯片与器件,避免因选型不当导致的设计失败,如YT-SG801RF的低功耗MCU

发表于 04-08 11:21

航天电器推出高密度550芯电源连接器及线缆组件

航天电器推出高密度550芯电源连接器及线缆组件,专为半导体测试机(ATE)、探针台、高性能负载板及芯片验证系统设计,提供高精度、低噪声、快速响应的供电解决方案。适用于高性能CPU/GP

MPO分支光缆:高密度光纤布线的核心组件

,同时支持高速率、低延迟的数据交互,为现代网络架构提供了高效解决方案。 技术特性:高密度与低损耗的平衡 MPO分支光缆的核心优势在于其高密度设计。以12芯MPO分支光缆为例,一端集成1

先进封装时代,芯片测试面临哪些新挑战?

架构;封装前需确保芯粒为 KGD 以避免高价值封装体报废,推高测试成本;高密度封装使测试时散热困难,易引发误判。先进封装要求

Kioxia研发核心技术,助力高密度低功耗3D DRAM的实际应用

全球存储解决方案领域的领军企业Kioxia Corporation今日宣布,已研发出具备高堆叠性的氧化物半导体沟道晶体管技术,该技术将推动高密度、低功耗3D DRAM的实际应用。这项技术已于12月

如何保证合金电阻的稳定性与精度?

保证合金电阻的稳定性与精度需从材料选择、制造工艺、结构设计、环境控制及测试验证等多维度综合施策。以下从技术原理、关键措施及实际应用三个层面展开分析: 一、材料选择:奠定稳定性基础 合金电阻的精度

台积电2纳米制程试产成功,AI、5G、汽车芯片

台积电2nm 制程试产成功 近日,晶圆代工龙头台积电(TSMC)正式宣布其2纳米制程技术试产成功,这一重大里程碑标志着全球半导体产业正式迈入全新的制程时代。随着试产工作的顺利推进,2纳米

MediaTek采用台积电2纳米制程开发芯片

MediaTek 今日宣布,MediaTek 首款采用台积电 2 纳米制程的旗舰系统单芯片(SoC)已成功完成设计流片(Tape out),成为首批采用该技术的公司之一,并预计明年底进入量产。双方

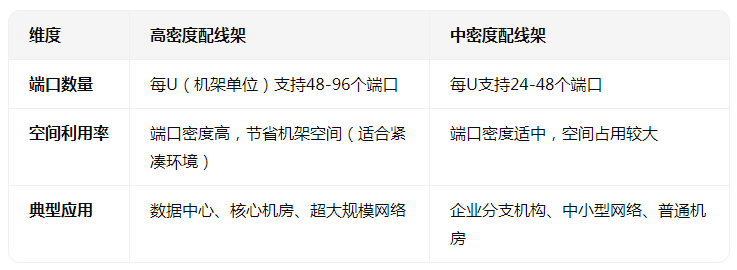

高密度配线架和中密度的区别

高度)可集成数百个光纤或铜缆端口(如MPO高密度配线架支持1U/96芯以上)。 空间利用率:通过模块化设计(如MPO连接器集成多芯光纤)和紧凑结构,显著提升机柜空间利用率,适合数据中心等对空间敏感的场景。 中

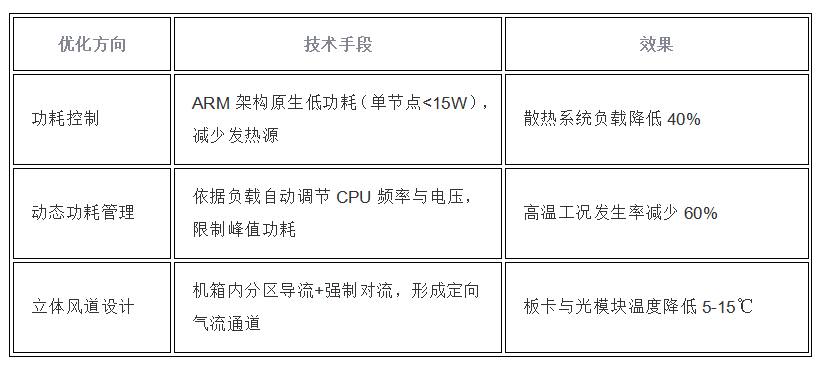

高密度ARM服务器的散热设计

高密度ARM服务器的散热设计融合了硬件创新与系统级优化技术,以应对高集成度下的散热挑战,具体方案如下: 一、核心散热技术方案 高效散热架构 液冷技术主导:冷板式液冷方案通过直接接触CPU/GPU

合金电阻稳定性优于其他材料的深度解析

合金电阻作为一种采用特殊合金材料制成的电阻器件,以其卓越的稳定性在众多应用中脱颖而出。本文将从材料特性、制造工艺以及应用场景三个方面,深入解析合金电阻稳定性优于其他材料的原因。 合金电阻的核心优势

格芯新开发出基于ARM架构的3D高密度测试芯片 成熟稳定性优于7纳米制程芯片

格芯新开发出基于ARM架构的3D高密度测试芯片 成熟稳定性优于7纳米制程芯片

评论