最新的电子产品通常需要三个独立的设计流程 - 芯片,封装和PCB - 这些产品在单个封装中使用越来越复杂的片上系统(SoC)和多个芯片。今天,这三个过程通常使用点工具执行,这些点工具需要耗时且容易出错的手动过程来链接这三个过程。但是,通过考虑每个设计决策的系统级影响,集成的3D芯片/封装/电路板协同设计环境能够以比过去更大的程度全面优化封装,电路板和IC设计。设计人员可以通过引脚分配和I/O布局优化可路由性,以最大限度地减少封装,芯片和电路板之间的层数。新方法可以在更短的时间内将更多功能性,更高性能和更便宜的产品推向市场。

限制传统的设计方法

传统的系统设计依赖于在独立环境中处理IC,封装和PCB的工具。这些流程缺乏系统级规划,可视化,设计和分析。规划中使用的设计数据库不能与用于审查和分析的数据库互操作,因此很难保证在规划期间做出的决策能够贯穿最终产品。在传统的2D组件专用设计工具中,协同设计具有挑战性,因为设计人员通常只能看到自己的组件。用于在这些环境之间交换数据的文件交换格式通常是过时的和缺陷的,缺少有用的设计数据或者是专有的并且没有广泛支持。传统流程中不存在工具来集成系统的所有组件并维护电气和机械数据库信息,从而提供可实现的协同设计环境。

过去这种方法是可以接受的,因为大多数复杂的系统都有大的外形(服务器,PC塔,大型机械),封装和基板成本在整个系统成本中可以忽略不计。随着功能的增加,成本的限制以及当今产品(便携式设备,可穿戴设备和汽车)的外形尺寸的减小,组件需要彼此紧密协调,以便针对小尺寸和最小层数基板优化引脚分配。/p>

由于缺乏工具集成,但设计要求不断增加,公司已恢复使用电子表格和通用办公生产力工具来执行规划和可行性研究以及定义工具界面和数据传输等变通方法。这些文件通常是内部开发的,必须在内部进行维护并手动操作以与流程中的工具进行交互。由于EDA工具的限制性文件输入格式,它们受到所提供信息的限制。它们会遇到诸如无法与最终设计输出数据自动关联的设计规划数据以及仅限于简单信息(如基本网络和位置信息)的引脚分配数据等问题。由于缺乏中央设计环境以及对系统数据使用手动反馈机制,引脚,I/O,布局布线的元件间优化是不可行的。

PCB产品设计供应商已开始介绍利用传统数据库来降低开发成本的工具来应对这些挑战。然而,由于传统数据库结构所施加的不灵活性,这些新工具仅限于2D环境或一个封装和一个PCB。需要在2D和3D视图之间来回切换需要在传统2D设计数据库和较新的3D查看器数据库之间进行文件转换,这会减慢设计过程,增加翻译准确度的不确定性并限制设计洞察力。

随着产品外形尺寸的缩小,需要使用机械设计的外壳检查ECAD设计尺寸,并考虑外壳进行多物理分析。随着外壳越来越多地从正交移动到更紧凑,更复杂的弯曲形状,需要3D视图,因为2D视图过于严格并且不能准确地表示系统。传统流程将ECAD和MCAD设计分开,几乎没有交叉流分析的机会。 MCAD流程中的电子行业特定设计自动化由于其通用性而难以实现。

系统级3D协同设计的出现

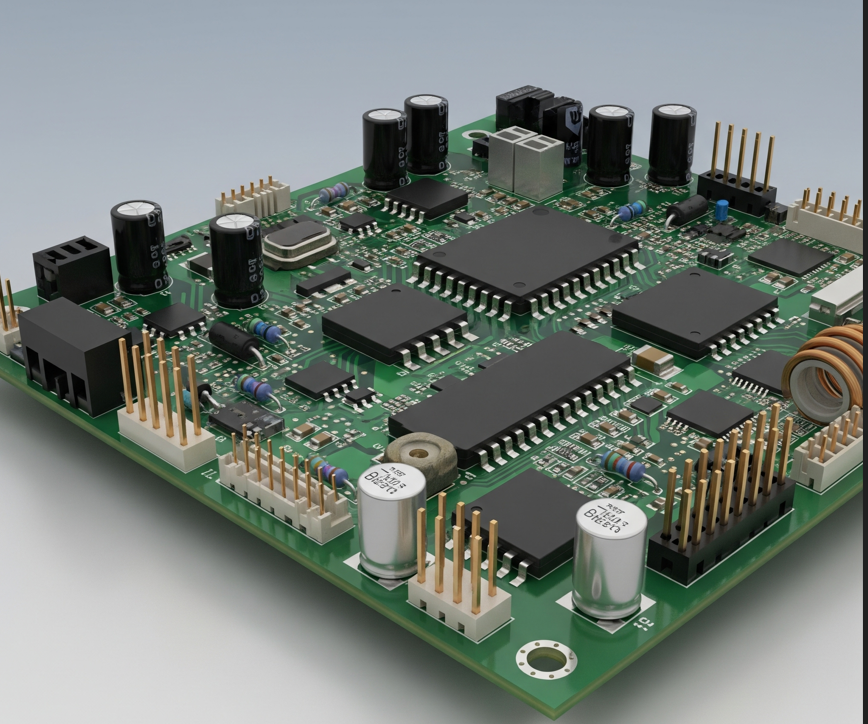

新一代系统级3D协同设计工具通过提供集成的系统设计环境来应对这些挑战系统级以及PCB,IC和机械外壳的规划和最终设计。这些数据库被放在一个视图中,因此每个参与项目的人都可以在完整产品的上下文中看到他们的谜题。工程师可以在单个用户界面中进行系统级设计,完整封装设计,完整PCB设计,插入器设计,并优化ICL设计的RDL(再分布层)布线和裸片放置。可以根据最终的ECAD外形尺寸(PCB,封装和IC)尺寸检查机械外壳设计,以确保安装和间隙。集成的制造设计工具使得可以在布局期间验证设计到供应商技术特定的制造和装配制造检查。可以自动生成文档以进行签核和制造。与多物理分析工具集成的按钮确保设计数据的高效快速传输,实现快速周转。

Co - 使用RDL和封装扇出逃生路由设计IC和封装

这种集成的协同设计环境允许在离散或有限的2D工具中无法使用独特的设计方法。例如,工程师可以在单一设计视图中考虑IC侧的RDL和PCB侧的逃逸路径,对不同数量的封装层进行可行性研究。能够对芯片和封装进行系统级协同设计,可以优化凸点和焊球布局,I/O布局和引脚分配,从而降低芯片,封装和PCB层数,即使在具有布线复杂性的非传统结构中也是如此在垂直方向上,如PoP,SiP,芯片级封装和3DIC/3D封装。芯片RDL和封装逃逸的自动布线允许快速寻路可行性,改善完成时间并允许用户优化裸片放置。其优势包括减少RDL,插入器/基板和封装层数量,同时优化信号性能并缩短出带时间。

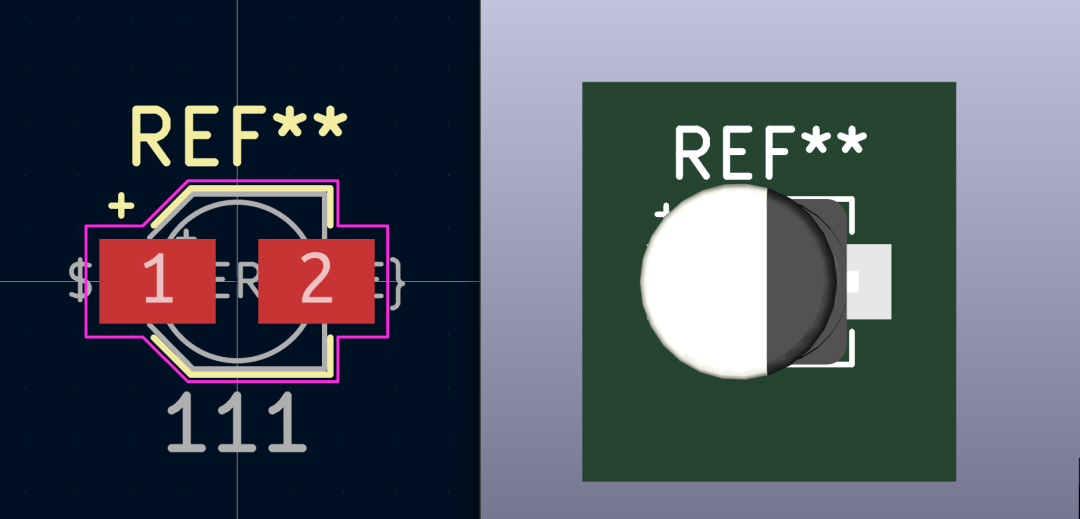

PCB设计(顶部)和封装设计(底部)之间的实时交换,以提高可布线性和性能

查看IC,封装和PCB同时在一个视图中帮助工程师优化引脚分配并避免连接错误,从而缩短设计时间。如果设计人员需要执行封装/IC凸点分配,他或她可以在PCB级别查看对鼠巢的影响。或者,如果设计人员必须在电路板级进行自动或交互式引脚交换以提高PCB布线性,他或她可以观察封装和IC级别的潜在影响。引脚交换操作在封装和PCB数据库之间自动传递,无需CSV或其他中性文件来传达更改。该工具还允许多个工程师在单个基板上工作,同时保护其他工程师的编辑。如果设计人员需要在锁定的包装设计中进行引脚交换,他或她可以发送通知,其他工程师可以接受或拒绝作为ECO。

智能PoP和SiP设计

使用该技术,可以将多个IC导入协同设计环境并连接在一起。 3D,多设计环境更智能地管理复杂包(如PoP和SiP)的路由相互依赖性。这种新方法通过实时3D设计为SiP提供重点设计规则检查,并支持堆叠LSI的复杂键合线放置。工程师可以使用共同设计环境来确保键合线在任何角度满足间距要求,并且3D键合线轮廓符合制造规范。

使用TSV管理复杂的2.5/3D IC设计

这种新方法极大地改善了基于TSV的设计(如3DIC)的布局规划和布线堆叠芯片和硅中介层。工程师可以导入现有数据库(来自OpenAccess,GDS或LEF/DEF文件)或使用设计环境生成TSV。可以使用导入或手动生成的制造和设计规则来执行自动或手动路由。预放置的TSV可以自动布线,而未放置的TSV可以放置和布线。 3D环境支持大型数据集,并允许设计人员查看复杂的转义和路由结构

通过集成信号和电源完整性分析验证信号性能

随着系统任何级别的变化,设计人员可以从信号完整性,电源完整性或散热角度查看效果。多学科,多物理分析可以使用Keysight Technologies,ANSYS,AWR,CST和Synopsys等解决方案提供商提供的一流解决方案。协同设计环境可在整个系统中实现信号可追溯性。可以检查和分析信号路径,因为它们跨越设计和组件边界,从驱动器到系统互连到接收器。智能和集成的基于原理图或布局的仿真环境支持多种设计流程。

结论

芯片/封装/电路板协同设计提供了统一的设计方法,使设计人员能够考虑每个设计决策的系统级影响,从而降低设计成本,提高性能,减少不确定性并加快进度。设计人员可以同时考虑IC/封装/PCB问题,以设计具有最佳信号性能的良好集成产品,同时减少RDL,插入器/基板和封装层数量,从而降低成本和出带时间。

-

PCB打样

+关注

关注

17文章

2982浏览量

23680 -

华强PCB

+关注

关注

8文章

1831浏览量

29330 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44715

发布评论请先 登录

深度解析3D眼镜电子电路设计难点与实践——YANTOK自主设计方案落地

3D打印机散热风扇:热管理核心与选型优化指南

2D、2.5D与3D封装技术的区别与应用解析

浅谈2D封装,2.5D封装,3D封装各有什么区别?

技术资讯 I 多板系统 3D 建模,提升设计精度和性能

技术资讯 I 图文详解 Allegro X PCB Designer 中的 3D 模型映射

【海翔科技】玻璃晶圆 TTV 厚度对 3D 集成封装可靠性的影响评估

3D封装的优势、结构类型与特点

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm

文件嵌入详解(一):在PCB封装库中嵌入3D模型

3D芯片/封装/ PCB协同设计优化系统怎样操作

3D芯片/封装/ PCB协同设计优化系统怎样操作

评论