无线RF接收器在许多应用中都会用到,包括无线安全系统、工业监控、仪表读数和家庭自动化等等。过去,半导体供应商主要使用模拟设计来构建这些接收器。如今,供应商正在转换到数字和混合信号设计,以期降低功耗和简化与其他组件的集成。

对于基于模型的设计,Semtech工程师扩展了对MathWorks工具的使用,目的是为了过渡至数字平台。多年来,工程师使用MATLAB和Filter Design HDL Coder为滤波器建模和生成HDL代码。在最近的项目中,他们使用了Simulink和HDL Coder为整个设计生成VHDL。

Semtech SX1231 无线收发器

挑战

Semtech工程师需要使用低IF架构为频移键控(FSK)和最小频移键控(MSK)解调开发数字接收器链。他们希望在工程的先期研究阶段,就针对性能、功耗和布局等性能,评估多种设计。为每个设计备选方案编写VHDL较为费时,而且限制了团队可以考虑的备选方案数量。

除了原型制作阶段外,Semtech工程师希望改善传统的产品代码开发工作流程。“对系统进行建模,确保它们符合要求之后,我们以往是在VHDL中重新实现模型,然后在新工具中重新执行仿真”,Prianon说道。“这样做随时都有可能引入错误,并且我们永远无法保证模型完全与新的VHDL代码一致。”

解决方案

Semtech使用MathWorks工具进行基于模型的设计,来快速探索和评估各种设计思想,自动生成产品级VHDL代码,改善工程师团队之间的协作,从而加快用于FSK和MSK解调的数字接收器链开发。

在先期研究阶段,Semtech工程师根据系统需求规范在Simulink中创建了浮点模型。他们使用来自Communications System Toolbox中的模块对信道中的噪音进行建模,并实现FSK和MSK解调。

借助Signal Processing Toolbox以及DSP System Toolbox,一位工程师设计并分析了级联积分梳状(CIC)和有限脉冲响应(FIR)数字滤波器,而另一位工程师则使用Simulink分析设计sigma-delta模数转换器(ADC)、锁相环路(PLL)以及整个系统的其他部分。

一旦分别完成数字接收器链的各个部分的仿真,工程师就可以相互共享Simulink模型,从而在完成系统集成之前验证自己的组件设计是否可以共同工作。

“手工编写VHDL没有任何优势可言。编写VHDL是一件非常枯燥的事情,还需要验证手写代码。利用Simulink和HDL Coder,一旦完成对模型的仿真,就可以直接自动生成VHDL,并使用FPGA进行原型验证。这样可以节省大量时间,并且生成的代码还包含一些我们未曾想到的优化。”

—— Frantz Prianon, Semtech

工程师运行仿真来验证设计,并使用Communications System Toolbox中的误码率计算模块来计算误码率。

借助Fixed-Point Designer,他们将设计从浮点转变为固定点表示形式,从而进行比特位级的仿真。

Semtech工程师使用HDL Coder从完整的接收器链的Simulink模型生成VHDL。为了验证VHDL,他们使用了HDL Verifier来通过Mentor Graphics Questa仿真器联合仿真以验证其Simulink设计与生成VHDL代码的一致性。

结果

创建原型的速度提高了50%。“在我们自行编写VHDL时,通常需要两个月才能创建FPGA原型”,Prianon说道。“借助Simulink和HDL Coder,我们无需再对每个模块进行繁琐的手动编码,只需数周便可创建原型。

验证时间从数周缩短为数天。“在之前的项目中,我们至少需要花两周时间来编写用于验证VHDL的测试用例”,Prianon回想说。“借助HDL Verifier,我们可以进行联合仿真,测试模型中的多个关键点,并验证VHDL,通常不到一天就可以完成。”

最终交付经过优化、性能更佳的设计。基于模型的设计让Semtech可以将从需求到下线的开发时间缩短 33%。“我们用节省下来的时间改善设计”,Prianon说。“MathWorks工具让我们可以探索更多备选方案和新功能,最终提供优化更好、效果更佳的设计。”

-

收发器

+关注

关注

10文章

3840浏览量

111489 -

滤波器

+关注

关注

162文章

8477浏览量

186359 -

接收器

+关注

关注

15文章

2652浏览量

77577

发布评论请先 登录

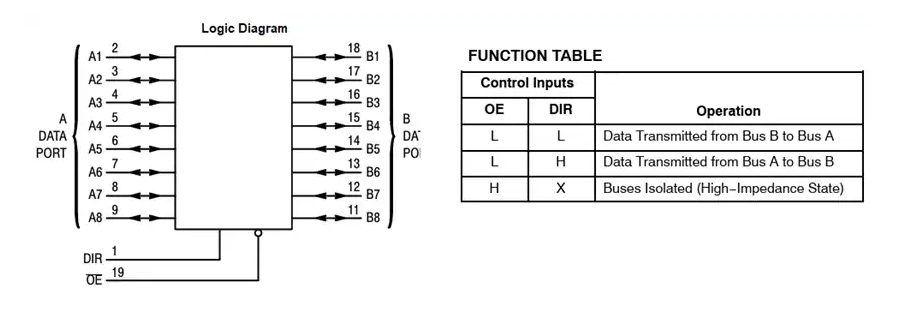

SGM4T245:4位双电源总线收发器的全面解析

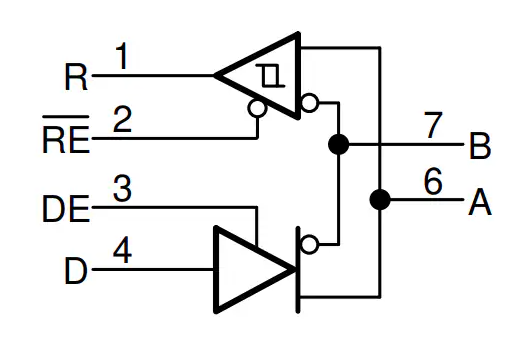

探索MAX13430E–MAX13433E RS-485收发器:低电压逻辑接口的卓越之选

PCM9211:216 - kHz数字音频接口收发器的深度解析

探索DIX9211:高性能数字音频接口收发器的技术剖析

光纤收发器品牌不同能混用吗?

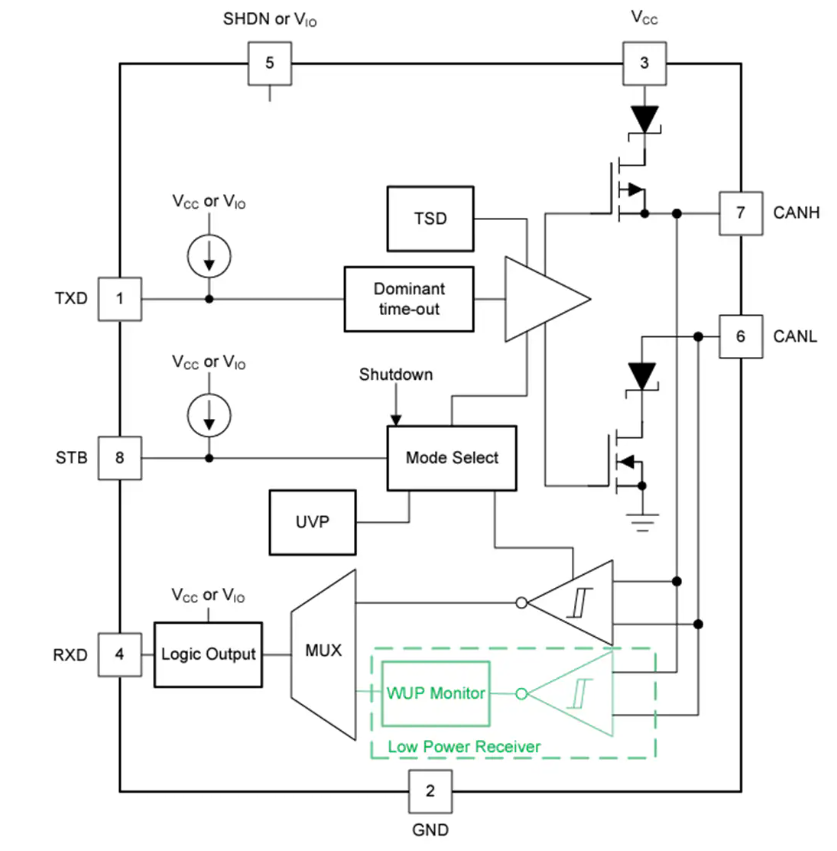

NXP TJA1051高速CAN收发器:技术解析与应用指南

光纤收发器6个指示灯含义

MC74VHC245/MC74VHCT245A 总线收发器技术解析与应用指南

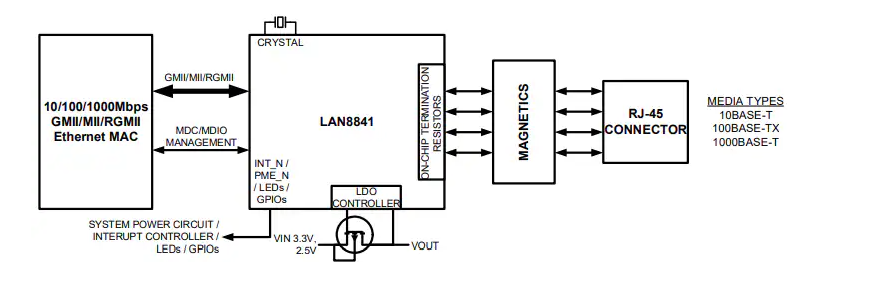

LAN8841千兆以太网收发器技术解析

TCAN341x系列3.3V CAN FD收发器技术解析与应用指南

德州仪器THVD1330高速RS-485收发器技术解析

CAN收发器:总线信号的“翻译官”

光模块与光纤收发器可以互连吗?

如何自动测量CAN收发器的延迟时间?

MATLAB基于FPGA和ASIC的数字收发器的开发和利用分析

MATLAB基于FPGA和ASIC的数字收发器的开发和利用分析

评论