制造年会如火如荼地进行,满满干货让人应接不暇。高峰论坛的演讲仿佛还在耳畔,又有两场专题演讲向大家袭来。

华虹三厂副厂长康军和华虹宏力技术研发总监杨继业为大家带来了什么精彩内容呢?一起来看看吧!

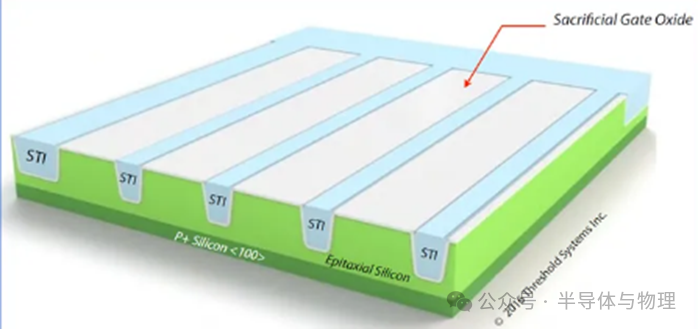

2017制造年会现场新闻速递 9月27日上午,华虹三厂副厂长康军以“高可靠性的嵌入式存储器工艺技术”为题,向各位参会嘉宾介绍了华虹宏力的当家工艺。华虹宏力拥有SONOS Flash和SuperFlash技术,以及eFlash+高压和eFlash+射频(RF)两个衍生工艺平台,技术节点涵盖0.18微米到90纳米。同时还可为客户提供高性能、高密度的标准单元库,并可根据不同需求为客户定制高速度、低功耗、超低静态功耗的嵌入式闪存IP、嵌入式电可擦可编程只读存储器(EEPROM)IP,可帮助客户减小低功耗设计难度,抢占市场先机。

康军副厂长详细介绍了华虹宏力SONOS存储模块特征参数,有力论证了其在高温下优良的耐久性和数据保持能力,以及在-40℃ ~ 85℃宽温范围内良好的写干扰性能。康军副厂长自豪地表示:“基于SONOS EEPROM平台制造的金融IC卡芯片,已通过EMVCo、CC EAL5+、万事达CQM等多项国际权威认证,证明了我们的金融IC卡芯片工艺及安全管理系统已达到国际先进水平。”SONOS存储器工艺中还可嵌入高压器件,目前,华虹宏力32V和12V/15V的HV CMOS以及14~40V的LDMOS均已处于大量出货状态。

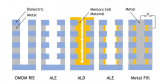

紧接着,康军副厂长指出嵌入式闪存正在向电压更低,光罩更少、存储单元更小的方向演变。华虹宏力的Floating gate(浮栅型) eFlash和SONOS eFlash在数据保持能力及耐久性上,均有优异表现,而自主开发的极具竞争力的90纳米NORD eFlash在这两方面甚至表现出了更高的可靠性。此外,华虹宏力还专为物联网打造了0.11微米eFlash超低功耗技术平台,提供整合射频、高性能闪存的同时,兼顾了低功率、低成本的优势。

华虹宏力将巩固在嵌入式非易失性存储器技术领域的世界领先地位,竭诚为客户提供优质服务。

9月27日下午,华虹宏力技术研发总监杨继业发表技术演讲“深耕卓越IGBT技术,智造绿色‘芯’未来”,与大家分享了华虹宏力功率技术现状及发展方向。

华虹宏力是全球首家、最大的功率器件8英寸代工厂,早在2001年,华虹宏力就开始了Trench MOSFET代工业务。研发人员持续攻关,于2011年成功开发了深沟槽超级结(Deep Trench Super Junction,DT-SJ)技术平台,这个革命性的突破也标志着华虹宏力成为世界第一家提供 DT-SJ解决方案的晶圆代工厂。2013年,基于沟槽结构的600V-1200V非穿通型和场截止型(Field Stop,FS)IGBT的量产也大获成功。今年年初,又推出了第三代DT-SJ 平台。

杨继业总监强调,“华虹宏力现拥有MOSFET/DT-SJ/IGBT技术,可提供从低电压至高电压应用的完整解决方案。”截止至2017年6月,华虹宏力功率器件平台累计出货量已突破500万片晶圆,其中DT-SJ出货超过25万片,IGBT超过5万片。

IGBT被誉为“功率半导体皇冠”,在绿色能源、马达驱动和新能源汽车等领域应用前景广阔。目前,华虹宏力战略性地专注于LPT(Light Punch-Through)和 FS IGBT技术,且拥有大陆最全、最先进的全套IGBT背面制程代工技术。通过设备升级、改造,华虹宏力成功配置了一整套IGBT超薄片(可生产至60微米薄片)背面工艺/测试生产线,成功实现量产。配合独特的激光退火工艺用于背面注入杂质激活,大大提高了背面注入杂质的激活率。

功率器件性能的改变不仅表现在能量变换效率的提升,而且表现在系统装置能量处理能力上——功率密度的提升,此指标平均每4年就提升1倍,被业界称为“功率电子领域的摩尔定律”。杨继业总监表示:“华虹宏力研发团队也正加速研发1700V以上超高压IGBT技术,向更高电压、更大电流等级和大功率进发,以期在新能源及工业市场一展身手。”

此外,杨继业总监还受邀参加了“IGBT先进制造-面临机遇和挑战圆桌论坛”,与多位IGBT专家展开了头脑风暴。

-

嵌入式

+关注

关注

5186文章

20156浏览量

328977 -

存储器

+关注

关注

39文章

7715浏览量

170870 -

工艺技术

+关注

关注

0文章

20浏览量

9735

发布评论请先 登录

热压键合工艺的技术原理和流程详解

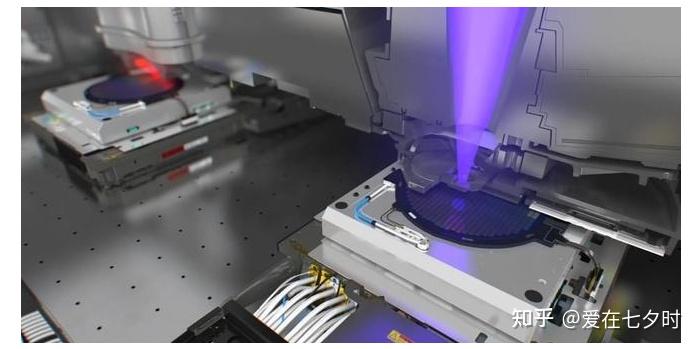

半导体“光刻(Photo)”工艺技术的详解;

芯片键合工艺技术介绍

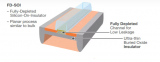

SOI工艺技术介绍

TSV技术的关键工艺和应用领域

微电机轴心的研磨生产工艺及调试技术

半导体刻蚀工艺技术-icp介绍

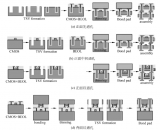

BiCMOS工艺技术解析

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测

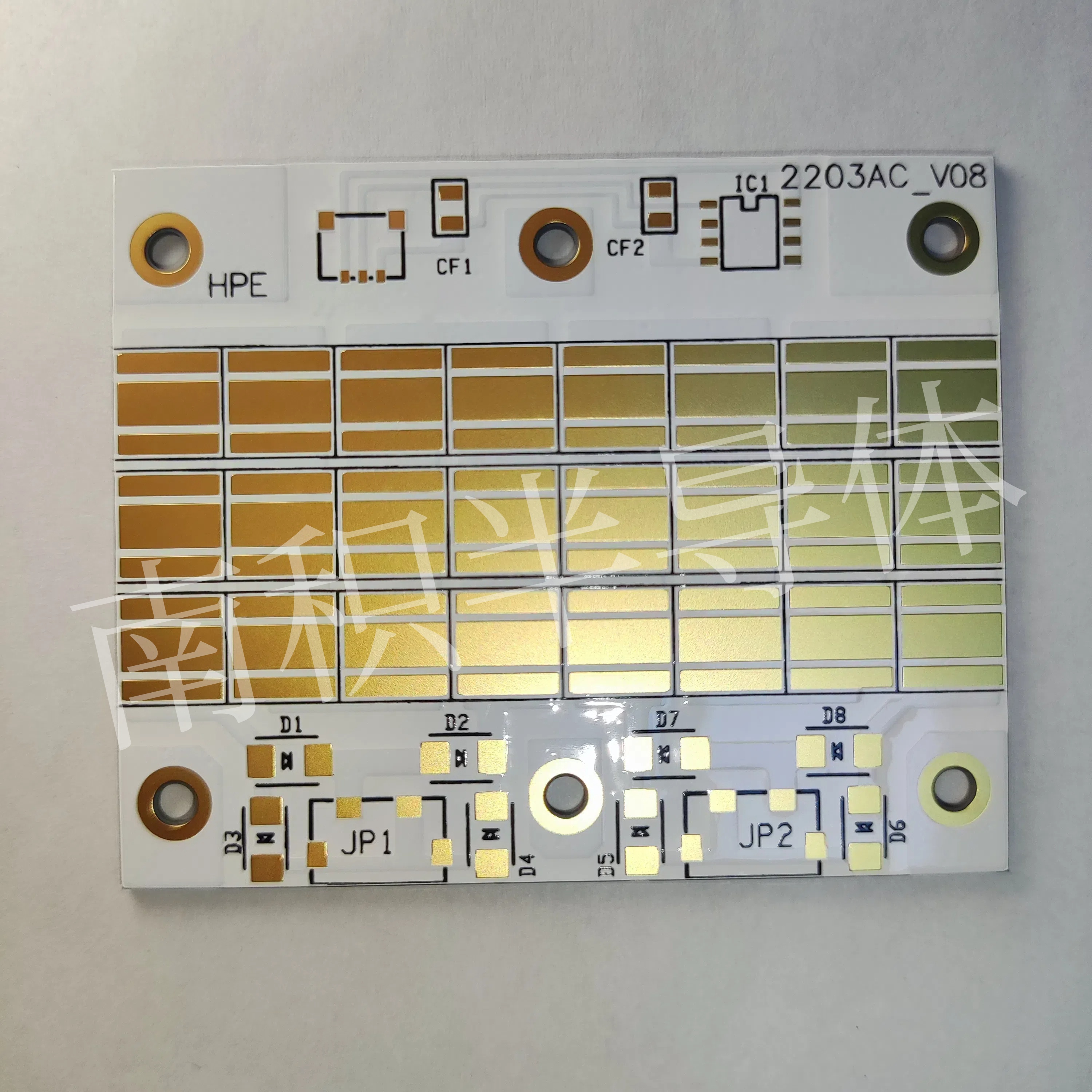

陶瓷基板五大工艺技术深度剖析:DPC、AMB、DBC、HTCC与LTCC的卓越表现

ALD和ALE核心工艺技术对比

回顾深耕核心工艺技术的内容介绍

回顾深耕核心工艺技术的内容介绍

评论