确保信号完整性的电路板设计准则信号完整性(SI)问题解决得越早,设计的效率就越高,从而可避免在电路板设计完成之后才增加端接器件。SI设计规划的工具

2009-07-04 07:49:26 2826

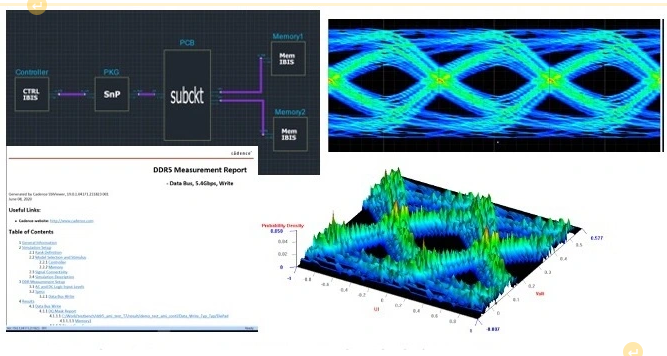

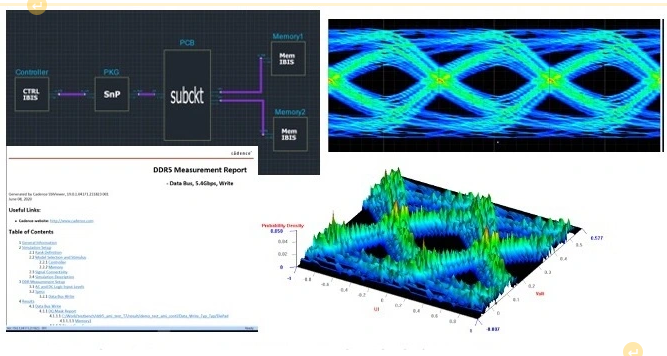

2826 本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。##时序分析。##PCB设计。

2014-07-24 11:11:21 6350

6350

伴随着设计复杂性的增加。 DDR5与前几代产品之间最显着的区别是判决反馈均衡的引入,这是串行链路系统中用于改善接收信号完整性的一项技术。 随着新技术的发展,本文将研究DDR5上下文中的一些基本信号完整性概念。第一部分介绍了眼图:确定信号完

2021-01-22 15:29:13 6930

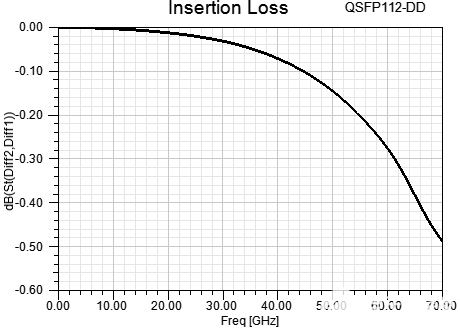

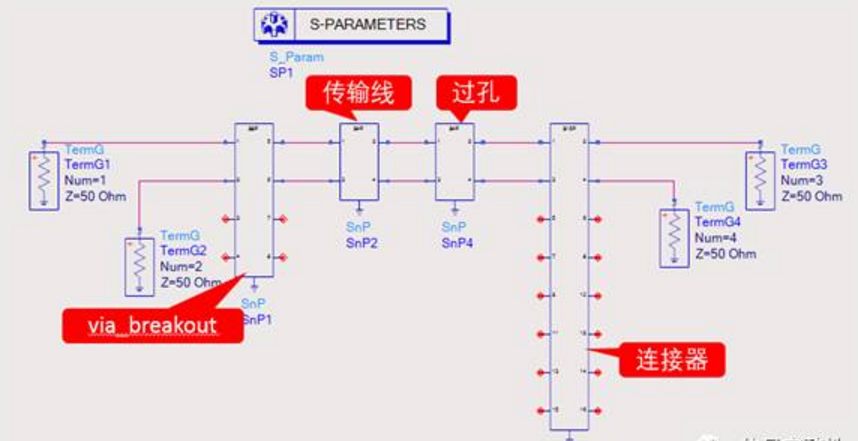

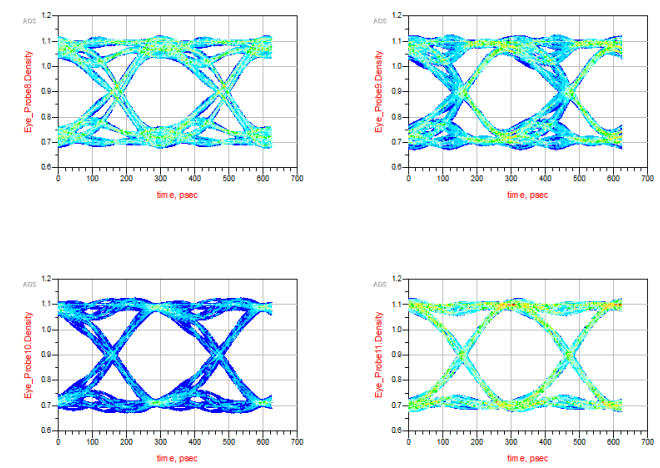

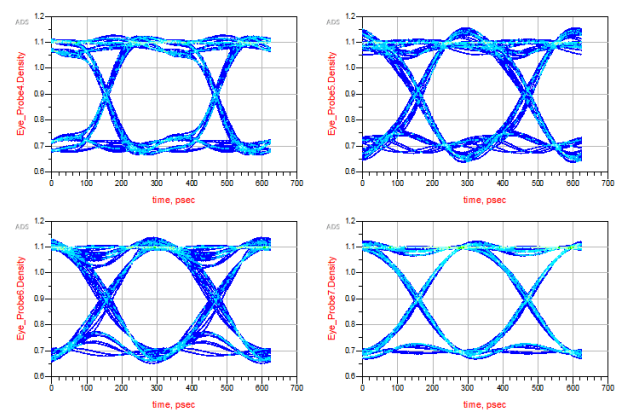

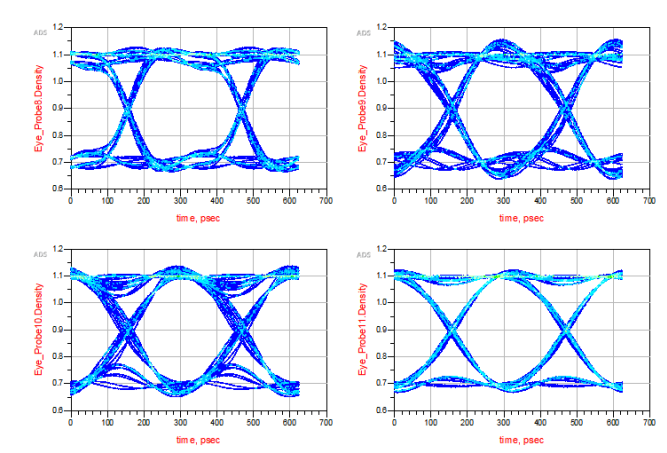

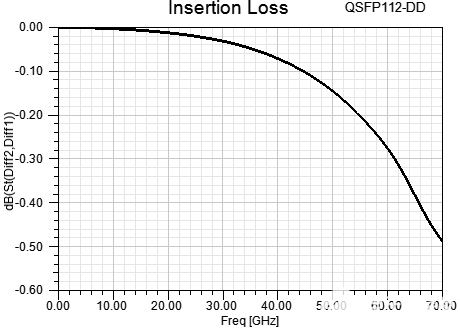

6930 越高的速率传输,意味着更快的上升沿和更高的带宽,这必然会为信号完整性带来极大的挑战。要满足所需的插损、回损、TDR和串扰等,必然要进行高速信号完整性仿真。

以800G DAC为例,高速信号

2022-07-15 16:01:02 2447

2447

信号完整性仿真重点分析有关高速信号的3个主要问题:信号质量、串扰和时序。对于信号质量,目标是获取具有明确的边缘,且没有过度过冲和下冲的信号。

2023-04-03 10:40:07 2527

2527 信号完整性(Signal Integrity,SI)是指电路系统中信号的质量,如果在要求的时间内,信号能不失真地从源端传输到接收端,我们就称该信号是完整的。

2023-09-28 11:27:47 4070

4070

DDR5已经开始商用,但是有的产品还才开始使用DDR4。本文分享一些DDR4的测试内容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以达到 3200Mb/s,这样高速的信号,对信号完整性的要求就更加严格,JESD79‐4 规范也对 DDR4 信号的测量提出了一些要求。

2024-01-08 09:18:24 4649

4649

测试结果。由于信号完整性问题经常作为间歇性错误出现,因此重视同步切换控制、仿真和封装,保证设计符合信号完整性要求,在硅片制造前解决问题。对于IC应用,可利用仿真来选择合理的端接元件和优化元器件的布局,更

2013-12-05 17:44:44

了极大的挑战。 本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性

2014-12-15 14:17:46

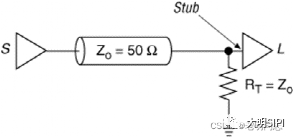

在CMD、ADD、CTRL信号为高电平时线路中就不会存在电流,可以降低功耗。DDR3和DDR4端接方式的对比如图4所示。图 4 DDR3和DDR4端接方式对比3 ACT_n信号为了避免由于容量增加

2019-11-12 12:40:17

做了电路设计有一段时间,发现信号完整性不仅需要工作经验,也需要很强的理论指导,坛友能提供一些信号完整性的视频资料么?非常感谢!

2019-02-14 14:43:52

在altium designer中想进行信号完整性的分析,可元件是自己造的,不知道仿真模型怎么建,哪些HC是啥意思也不知道

2012-11-01 21:43:04

中国电子电器可靠性工程协会关于组织召开“信号完整性仿真应用”高级研修班的邀请函各有关单位:为了帮助广大从业人员详细了解信号完整性(SI)和电源完整性(PI)的基本概念、分析方法和应用实例,帮助电子

2009-11-25 10:13:20

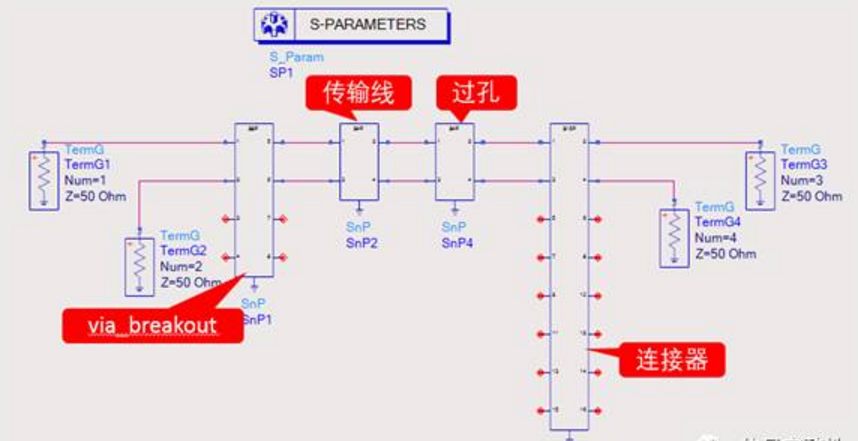

的完整性分析中,电路设计者需要考虑这些控制的实际实现方式,因为它们会影响到电路的负载特性以及波形性能。另外,还需考虑芯片上解耦电容的实现。 如图3所示的电路仿真图中包括了芯片、封装及PCB板信号线互联

2015-01-07 11:33:53

信号完整性与电源完整性的仿真分析与设计,不看肯定后悔

2021-05-12 06:40:35

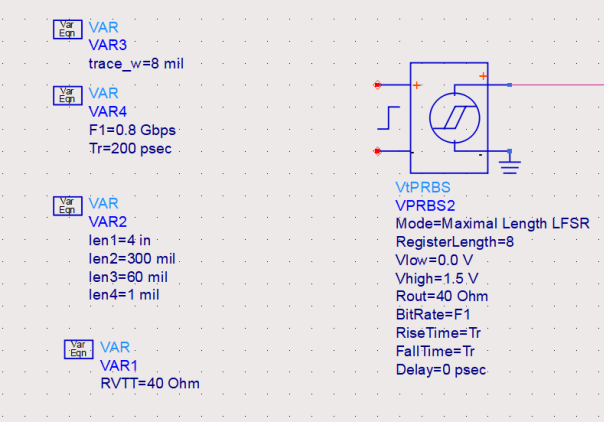

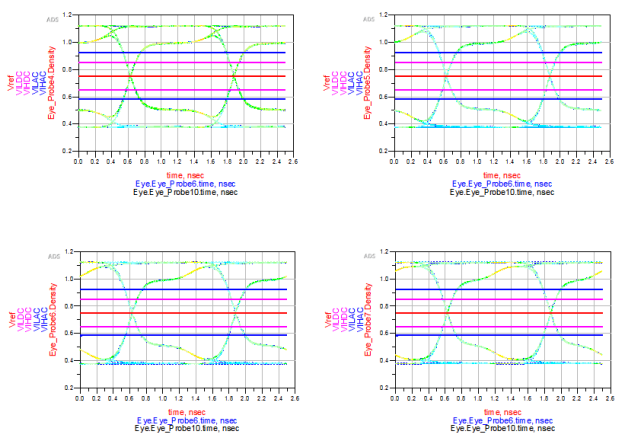

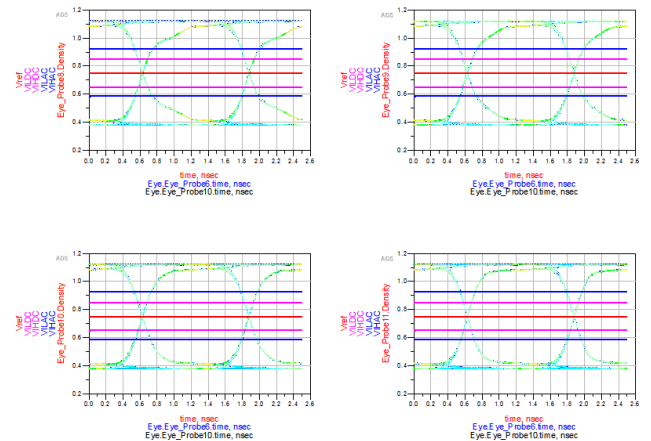

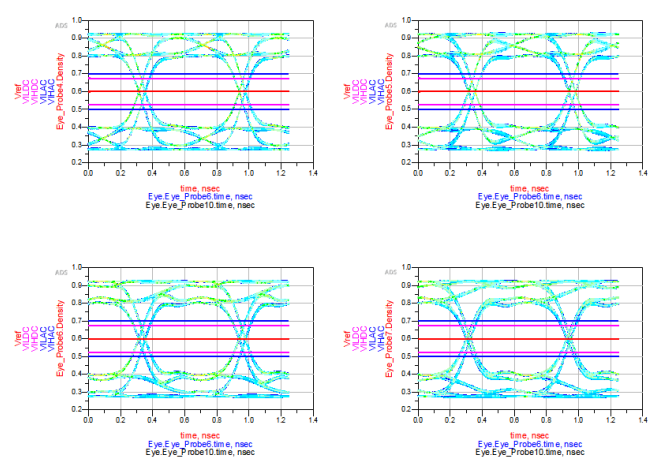

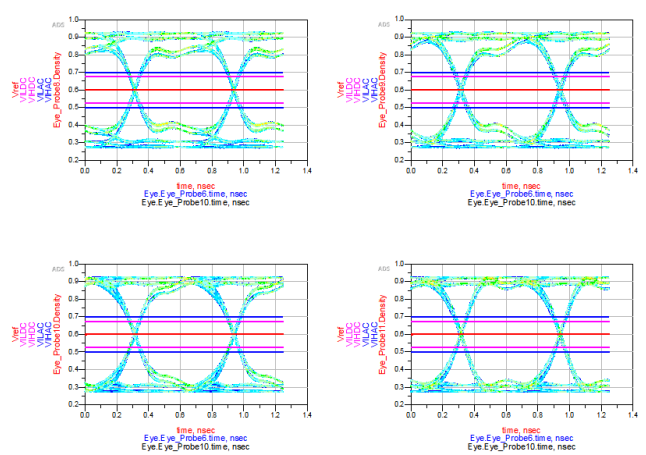

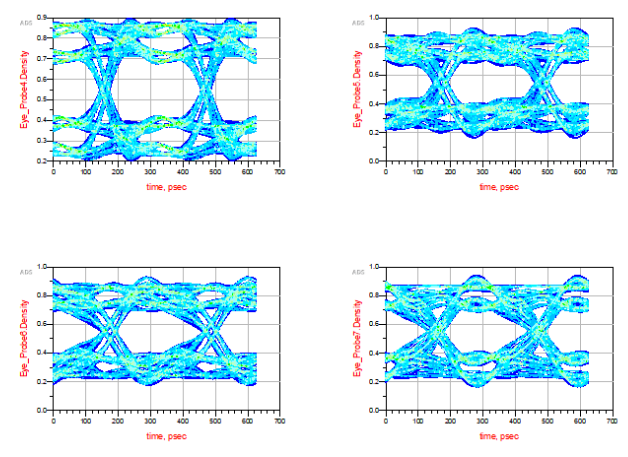

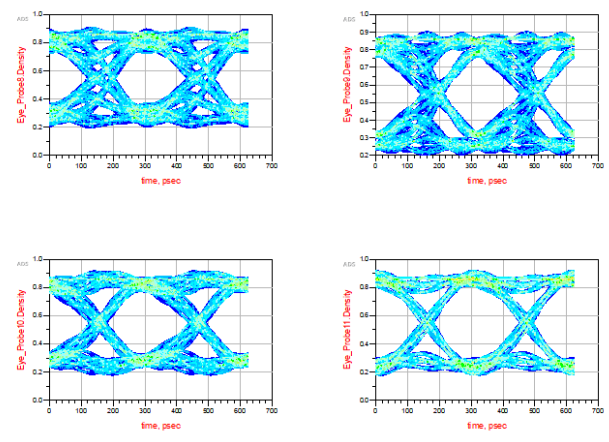

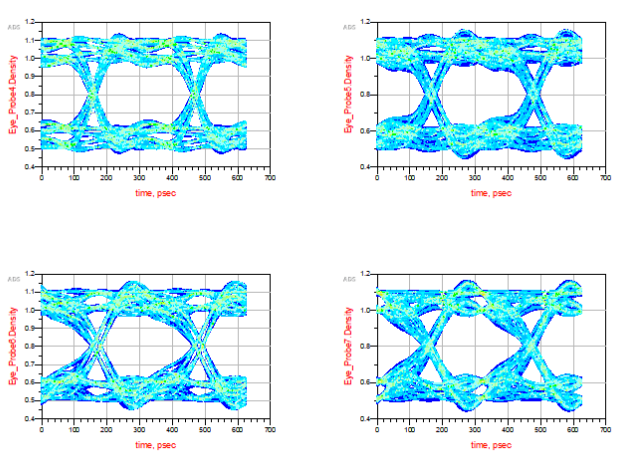

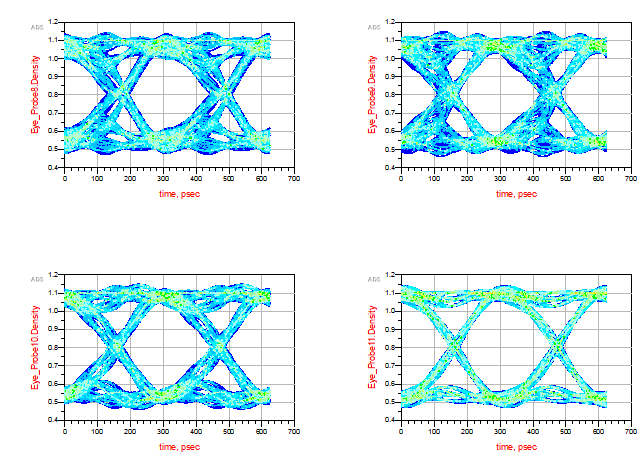

。 b、AC端接适合周期性信号,不适合非周期性信号。 c、会导致容性负载增加,RC延时增加。 d、相对于并联端接,有助于减小直流功耗。 图5、6 ADS仿真:RC端接 (4)戴维南端接:通过

2023-03-07 17:13:20

信号完整性资料

2015-09-18 17:26:36

信号完整性的定义信号完整性包含哪些内容

2021-03-04 06:09:35

扰、轨道塌陷和电磁干扰。3、随着上升边的减小或者时钟频率的提高,各种信号完整性问题变得更严重,并且更加难以解决。4、由于晶体管越来越小,它们的上升边将越来越短,信号完整性也将成为越来越大的问题,这是

2015-12-12 10:30:56

本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题?

2021-01-25 06:51:11

熟悉PCB layout设计,学习DDR3\DDR4板的布局技巧,且熟悉至少一种仿真软件,不管是Hspice,还是Ansys designer/HFSS/SIwave/,或者是Hyperlynx

2019-09-03 17:54:59

Cadenc高速電路設計SI PI 信号完整性电源完整性仿真視頻教程下載鏈接地址:链接:http://pan.baidu.com/s/1pJiPpzl密码:3yjv

2015-07-30 21:44:10

哪位同学有Hyperlynx的对PCB信号完整性仿真的相关教程分享一下???跪求!!!

2016-06-15 10:16:02

关于组织召开“信号完整性仿真应用”高级研修班的邀请函各有关单位:为了帮助广大从业人员详细了解信号完整性(SI)和电源完整性(PI)的基本概念、分析方法和应用实例,帮助电子行业

2009-11-18 17:28:42

hyperlynx Sigrity信号完整性仿真之高速理论视频教程Allegro 平板电脑DDR3 PCB设计视频教程链接:https://pan.baidu.com/s/1P1elXupWFQ8KNh-u7QhCDg 密码:fc5q

2018-08-25 15:54:28

`编辑推荐《国外电子与通信教材系列:信号完整性与电源完整性分析(第二版)》强调直觉理解、实用工具和工程素养。作者以实践专家的视角指出造成信号完整性问题的根源,并特别给出了设计阶段前期的问题解决

2017-09-19 18:21:05

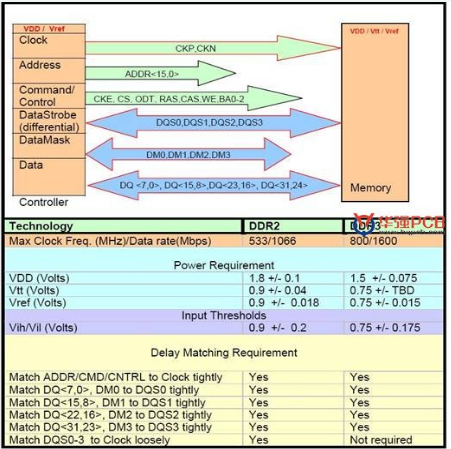

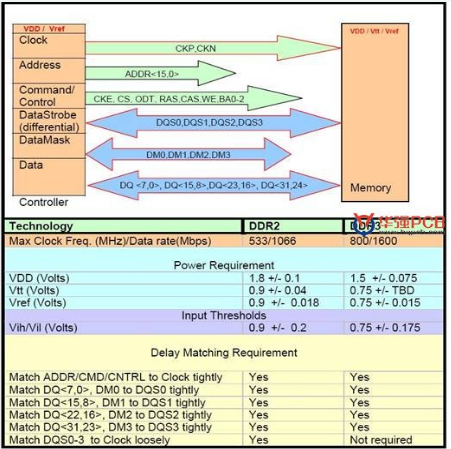

本文章主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关

2019-07-30 07:00:00

何为信号完整性:信号完整性(Signal Integrity,简称SI)是指在信号线上的信号质量。差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同引起的。当电路中信号能以要求的时序

2021-12-30 08:15:58

资深硬件工程师的高速信号完整性仿真实例操作,用的是allegro,很有价值。[hide][/hide]

2020-07-13 23:18:49

。DDR3 SDRAM在降低系统功耗的同时提高了系统性能,其利用“FlyBy”和动态片上匹配技术对于信号完整性的改善效果明显[5]。本文基于Xilinx的MIG_v1.91 IP核进行了DDR3 SDRAM

2018-08-02 09:34:58

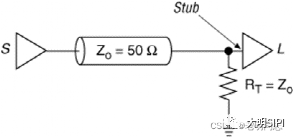

布线必须考虑的关键因素。因为时序要求严格,这种节点通常必须采用端接器件才能达到最佳SI质量。要预先确定这些节点,同时将调节元器件放置和布线所需要的时间加以计划,以便调整信号完整性设计的指针。5、技术

2018-07-31 17:12:43

何为信号完整性?信号完整性包括哪些?干扰信号完整性的因素有哪些?如何去解决?

2021-05-06 07:00:23

如何进行兼顾电源影响的DDR4信号完整性仿真

2021-01-08 07:53:31

信号完整性设计方法,是从全局上把握整个设计,所做的远远不只有仿真。《信号完整性设计中的5类典型问题》一文中,对几类问题做过简单的阐述,感兴趣的可参考阅读。在系统化信号完整性设计方法的框架下,需要仿真

2017-06-23 11:52:11

信号完整性(SI)问题解决得越早,设计的效率就越高,从而可避免在电路板设计完成之后才增加端接器件。SI设计规划的工具和资源不少,本文主要探索,究竟还有什么办法可以确保信号完整性?

2019-08-02 07:52:35

模拟DDR3的地址信号与时钟信号

2021-03-02 08:12:10

针对DDR2-800和DDR3的PCB信号完整性设计

2012-12-29 19:12:39

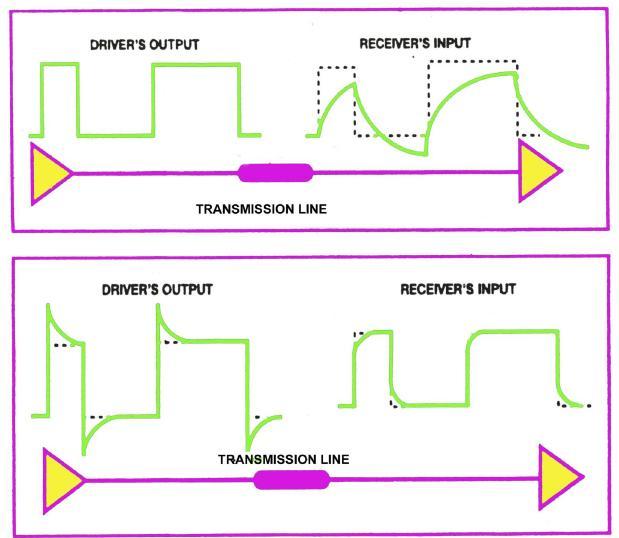

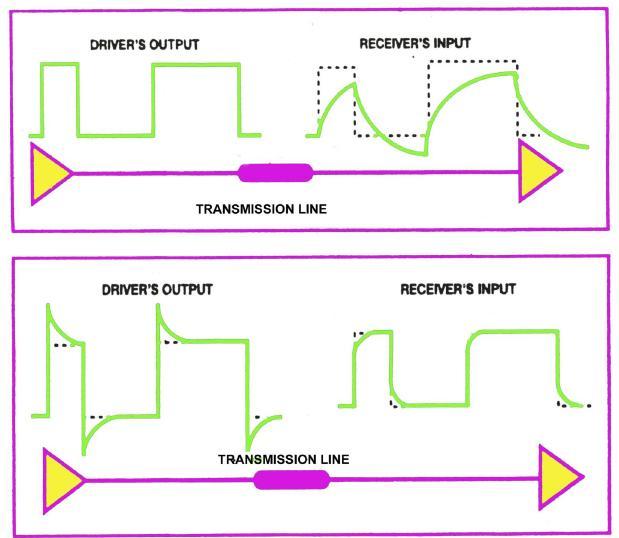

高速电路信号完整性分析与设计—信号完整性仿真仿真中有两类信号可称之为高速信号:高频率的信号(>=50M)上升时间tr很短的信号:信号上升沿从20%~80%VCC的时间,一般是ns级或

2009-09-12 10:31:31

高速电路信号完整性分析与设计—信号完整性仿真:仿真信号仿真中有两类信号可称之为高速信号:高频率的信号(>=50M)上升时间tr很短的信号:信号上

2009-10-06 11:19:50 0

0 高速数字电路信号完整性分析与设计:信号完整性概述 传输线理论 PCB阻抗控制 拓扑与端接技术 时序计算 串扰与对策

2009-10-06 11:25:17 0

0 信号完整性原理分析

什么是“信号完整性”?在传统的定义中“完整性(integrity)”指完整和末受损的意思。因此,具有良好完整性的数字信号应是干净,

2009-11-04 12:07:06 212

212 信号完整性和时序分析的模式变化:简单的接口分析经验法则在分析现代高速接口(如DDR2、PCI Express和SATA-II)时非常不合适。随着新兴标准(如DDR3 和5-10 Gbps串行接口)逐渐普及,

2010-04-27 08:25:54 70

70 目录信号完整性描述3数字技术和信息时代3逐渐增长的带宽为数字系统设计带来的挑战3 - 4信号完整性概念回顾4 - 8数字信号时序产生的问题5隔离模拟故障6眼图

2010-07-17 11:09:36 0

0 信号完整性基础根据定义, “完整性”是指“完整和无损害的”。 同样,一个具有良好的完整性的数字信号有干净、快速的上升沿;稳定和有效的逻辑电平;准确的时间位置和

2010-08-05 15:11:33 242

242 针对高速数字电路印刷电路板的板级信号完整性, 分析了IBIS 模型在板级信号完整性分析中的作用。利用ADS 仿真软件, 采用电磁仿真建模和电路瞬态仿真测试了某个实际电路版

2010-08-23 17:18:04 39

39 确保信号完整性的电路板设计准则 信号完整性(SI)问题解决得越早,设计的效率就越高,从而可避免在电路板设计完成之后才增加端接器件。SI

2009-03-25 11:44:15 550

550 什么是信号完整性

信号完整性(Signal Integrity):就是指电路系统中信号的

2009-06-30 10:23:18 5717

5717

浅谈确保信号完整性的电路板设计准则

信号完整性(SI)问题解决得越早,设计的效率就越高,从而可避免在电路板设计完成之后才增加端接器件。SI设计规划的...

2010-01-16 16:33:59 1167

1167 本文章主要涉及到对 DDR2 和DDR3 在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB 层数,特别是4 层板

2011-07-12 17:31:10 0

0 高速系统设计中, 信号完整性 重要性日益突出。在研究高速D5、P系统设计现状和信号完整性要求基础上,借助I_BIS模型和HyperI,y11x仿真软件,对基于TMS320C6416的高速视频编码系统进行了

2011-07-19 11:42:17 146

146 介绍引起信号完整性问题的主要因素, 利用。进行信号仿真的步骤, 给出了的信号仿真的时比结果, 并以该信号作为分析对象, 详细分析了为判断信号质童的优劣, 对仿真波形进行定量分析

2011-11-30 11:09:46 0

0 为了使设计人员对信号完整性与电源完整性有个全面的了解,文中对信号完整性与电源完整性的问题进行了仿真分析与设计,也从系统的角度对其进行了探讨。

2011-11-30 11:12:24 0

0 本专题详细介绍了信号完整性各部分知识,包括信号完整性的基础概述,信号完整性设计分析及仿真知识,还有具体应用中的一些小经验分享等等,充分翔实的向大家描述了信号完整性。

2011-11-30 11:44:35

本书全面论述了信号完整性问题。主要讲述了信号完整性和物理设计概论,带宽、电感和特性阻抗的实质含义,电阻、电容、电感和阻抗的相关分析,解决信号完整性问题的四个实用技术手段,物理互连设计对信号完整性

2015-11-10 17:36:24 0

0 信号完整性是指信号在通过一定距离的传输路径后在特定接收端口相对指定发

送端口信号的还原程度。在讨论信号完整性设计性能时,如指定不同的收发参考端

口,则对信号还原程度会用不同的指标来描述。

2016-02-19 16:41:51 0

0 电地完整性、信号完整性分析导论,有需要的下来看看

2016-02-22 16:18:01 71

71 针对DDR2-800和DDR3的PCB信号完整性设计

2016-02-23 11:37:23 0

0 针对DDR2-800和DDR3的PCB信号完整性设计,要认证看

2016-12-16 21:23:41 0

0 10129@52RD_信号完整性与电源完整性的仿真分析与设计

2016-12-14 21:27:39 0

0 于博士撰写的信号完整性设计中的5类问题,成功的阐述了信号完整性设计中问题的出现与解决方法。还有更多相关资料可以到于博士网站上去学习。

2017-01-22 20:49:12 0

0 所谓“万丈高楼平地起”,说的就是这个道理,想从事信号完整性工作就必须对整个信号完整性的理论基础有一个很明晰的了解。至少要熟读几本信号完整性方面的书籍,了解什么是信号完整性;了解信号完整性研究的对象和内容是什么;信号完整性与哪些因素有关系;信号完整性会影响到产品的哪一个方面;等等。

2017-08-29 15:47:22 21315

21315 信号完整性(Signal Integrity Signal Integrity,简称SI SI)是指在信号线上的信号质量。差的信号完整性不是由某一单一 因素导致的,而是板级设计中多种因素共同

2017-11-16 13:24:51 0

0 的工艺发展使得集成度越来越高,导致芯片上电流密度急速增加,使信号完整性的问题更加严重。因此非常有必要从整个系统设计开始就考虑信号完整性与电源完整性的问题。这就需要在设计前后把信号完整性和电源完整性仿真引入到设计流程中。

2017-12-04 04:59:26 34095

34095

本文章主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关技术,其中一些设计方法在以前已经成熟的使用过。

2018-02-06 18:47:57 3382

3382

高速 PCB 信号完整性仿真分析.pdf

2018-05-07 14:52:31 52

52 本文首先介绍了PCB信号完整性的问题,其次阐述了PCB信号完整性的步骤,最后介绍了如何确保PCB设计信号完整性的方法。

2018-05-23 15:08:32 11792

11792 目前,比较普遍使用中的DDR2的速度已经高达800 Mbps,甚至更高的速度,如1066 Mbps,而DDR3的速度已经高达1600 Mbps。对于如此高的速度,从PCB的设计角度来讲,要做到严格

2019-07-25 15:47:46 2502

2502

借助功能强大的Cadence公司SPEECTRAQuest仿真软件,利用IBIS模型,对高速信号进行信号完整性仿真分析是一种高效可行的分析方法,可以发现信号完整性问题,根据仿真结果在信号完整性相关问题上做出优化的设计,从而达到提高设计质量,缩短设计周期的目的。

2019-05-20 15:25:37 1542

1542

技术分享:信号完整性仿真 - 入门

2019-07-02 12:03:07 4676

4676

在Cadence信号和电源完整性三天活动的第二天,只有100多名与会者听取了会议,Robert Hanson解释了与DDR3和PCI Express 3.0相关的高速接口设计挑战。罗伯特在设计时序合规性以及如何满足多吉比特接口上的误码率规范时,揭开了神秘面纱。

2019-09-01 09:50:27 6731

6731

本文档的主要内容详细介绍的是DDR和DDR2与DDR3的设计资料总结包括了:一、DDR的布线分析与设计,二、DDR电路的信号完整性,三、DDR Layout Guide,四、DDR设计建议,六、DDR design checklist,七、DDR信号完整性

2020-05-29 08:00:00 0

0 在PCB板上的布局、高速信号线的布线等因素,都会引起信号完整性的问题,对于PCB布局来说,信号完整性需要提供不影响信号时序或电压的电路板布局,而对电路布线来说,信号完整性则要求提供端接元件、布局策略和布线信息。 PCB上信号速度高、端接元件的布局不正确或高

2022-11-17 11:46:28 1645

1645 本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题?

2021-01-20 14:22:53 2345

2345

本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题?

2021-01-23 08:45:50 28

28 本文章主要涉及到对DDR2和DDR3在PCB设计时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。 文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关技术,其中

2021-03-25 14:26:01 5336

5336

Hyperlynx信号完整性仿真性分析。

2021-04-07 13:59:10 144

144 电子发烧友网为你提供模拟DDR3的地址信号与时钟信号资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-12 08:45:05 23

23 DDR4电路板设计与信号完整性验证挑战

2021-09-29 17:50:07 14

14 信号完整性与电源完整性的仿真(5V40A开关电源技术参数)-信号完整性与电源完整性的仿真分析与设计!!!

2021-09-29 12:11:21 91

91 高速电路信号完整性分析与设计—端接与拓扑

2022-02-10 16:38:28 0

0 高速电路信号完整性分析与设计—信号完整性仿真

2022-02-10 17:29:52 0

0 传统的信号分析通常在 PDN 是“理想”的假设下运行。这是为了方便和权宜之计,而不是准确性。随着我们进入具有 6.4-Gbps 数据速率和 3.2-GHz 系统时钟的 DDR5 领域,功耗感知信号完整性问题的可能性开始变得更加显着。

2022-05-13 17:33:24 5441

5441

的工艺发展使得集成度越来越高,导致芯片上电流密度急速增加,使信号完整性的问题更加严重。因此非常有必要从整个系统设计开始就考虑信号完整性与电源完整性的问题。这就需要在设计前后把信号完整性和电源完整性仿真引入到设计流程中。

2022-08-30 09:13:44 8293

8293 定义:信号完整性(Signal Integrity,简称SI)是指在信号线上的信号质量。差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同 引起的。当电路中信号能以要求的时序、持续时间和电压幅度到达接收端时,该电路就有很好的信号完整性。当信号不能正常响应时,就出现了信号完整性问题。

2022-11-16 14:56:00 6200

6200 问题的影响变得越来越显著,在设计过程的早期解决这些问题非常关键。通过信号完整性仿真,工程师可以在电路设计早期发现问题,减少昂贵的重新设计或产品召回的风险。并且优化电路的性能,提高最终产品的总体质量和可靠性。 信号完整性问题可能来自各种因素,包括阻抗不匹配、寄生电容

2023-03-11 07:30:04 1712

1712 现有产品设计对信号完整性很重视,但对于电源完整性的重视好像不够,主要是因为,对于低频应用,开关电源的设计更多靠的是经验,或者功能级仿真来辅助即可

2023-04-10 09:16:16 3570

3570 终端端接对于信号完整性有着重要的意义,它和源端匹配一样都是解决信号完整性问题的重要手段。

2023-06-15 11:08:03 2906

2906

业界经常流行这么一句话:“有两种设计师,一种是已经遇到了信号完整性问题,另一种是即将遇到信号完整性问题”。固态硬盘作为一种高集成度的高时钟频率的硬件设备,信号完整性的重要性不言而喻。借着这句话本文主要跟大家聊下信号完整性的一些基本内容。

2023-06-27 10:43:26 3271

3271

何为信号完整性的分析信号完整性包含:波形完整性(Waveformintegrity)时序完整性(Timingintegrity)电源完整性(Powerintegrity)信号完整性分析的目的就是用

2023-08-17 09:29:30 8719

8719

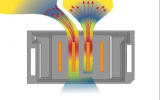

一种新的连接器系统通过改善电源完整性来提高信号完整性。优化电源完整性可提供更大的信号完整性余量,并提高电源和热效率。

2023-08-30 10:37:36 1788

1788

pcb信号完整性详解 随着电子领域技术日新月异的发展,高速电路已经成为了电路设计的重要领域之一。在高速电路中,信号完整性显得尤为重要。在设计PCB电路时,信号完整性是一个必须考虑的因素。那么

2023-09-08 11:46:58 2269

2269 内置校准: DDR3和DDR4控制器通常具有内置的校准机制,如ODT (On-Die Termination)、ZQ校准和DLL (Delay Locked Loop)。这些机制可以自动调整驱动和接收电路的特性,以优化信号完整性和时序。

2023-09-11 09:14:34 1693

1693 电子发烧友网站提供《基于PDN共振峰的最坏情况数据模式分析电源完整性对FPGA DDR4存储器接口中的信号完整性的影响.pdf》资料免费下载

2023-09-13 09:56:49 0

0 为什么电路端接电阻能改善信号完整性? 在电路设计中,信号完整性是一个极其重要的概念。信号完整性是指信号在传输、转换和处理过程中所遭受的失真、干扰或损失。这些信号可能是模拟信号或数字信号,它们的完整性

2023-10-24 10:04:52 1854

1854 PCB级的信号完整性仿真

2022-12-30 09:20:36 15

15 在现代电子通信和数据处理系统中,信号完整性(Signal Integrity, SI)是一个至关重要的概念。它涉及信号在传输过程中的质量保持,对于确保系统性能和稳定性具有决定性的影响。本文将从信号完整性的定义、影响因素、测试方法、以及在实际应用中的重要性等方面,对信号完整性进行详细的探讨。

2024-05-28 14:30:58 2970

2970 2024年12月20日14:00-16:00中星联华科技将举办“高速信号完整性分析与测试”-“码”上行动系列线上讲堂线上讲堂。本期会议我们将为大家介绍高速串行总线传输基本框架,什么是信号完整性?高速

2024-12-15 23:33:31 1135

1135

电子发烧友App

电子发烧友App

评论