在Cadence信号和电源完整性三天活动的第二天,只有100多名与会者听取了会议,Robert Hanson解释了与DDR3和PCI Express 3.0相关的高速接口设计挑战。罗伯特在设计时序合规性以及如何满足多吉比特接口上的误码率规范时,揭开了神秘面纱。

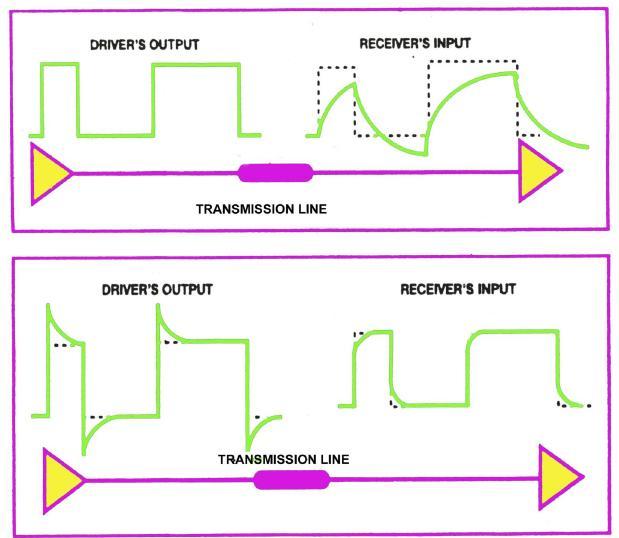

罗伯特关于多千兆位接口的材料包括关于趋肤效应,介电损耗和需要预先强调。

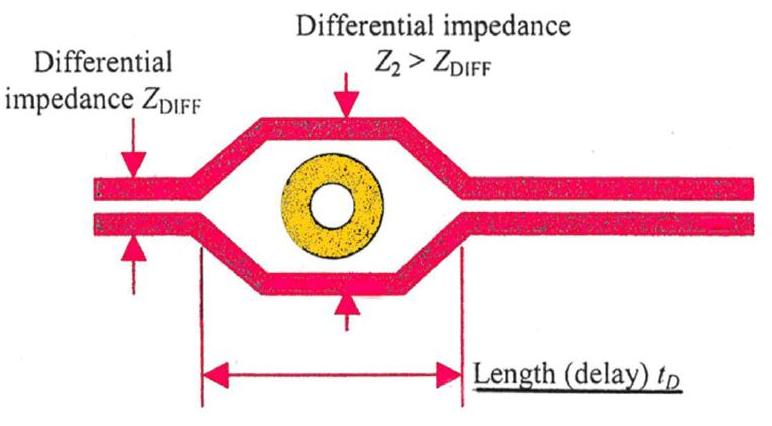

此外,由于多千兆位串行链路总是以差分对形式实现,因此罗伯特讨论了一些风险。管理差分阻抗很差。

许多与会者都能参加下午的研讨会,这些研讨会让人们可以亲身体验分析DDR3的Cadence工具。 PCB上的PCI Express互连。

此次高级信号完整性日为与会者提供了学习理论,熟悉工具,然后再使用工具的独特机会将这种经验带回他们的工作场所并立即应用于过程中的设计。第三天返回的与会者将有机会了解电力传输网络(PDN)的设计和分析,并再次有机会获得执行PDN分析的Cadence工具的实际操作经验。

-

信号完整性

+关注

关注

68文章

1473浏览量

97771 -

电源完整性

+关注

关注

9文章

223浏览量

21832

发布评论请先 登录

了解信号完整性的基本原理

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

信号完整性测试基础知识

电源完整性理论基础

是德示波器在电源完整性分析中的应用

听懂什么是信号完整性

基于Cadence的信号和电源完整性设计与分析

基于Cadence的信号和电源完整性设计与分析

评论