大规模设计需要在无线通道卡或者线路卡等现有应用中加入新功能,或者通过把两种芯片功能合并到一个器件中,减小电路板面积,或者针对新应用开发新设计。

2011-11-30 10:25:34 1117

1117

过去,每两年才能提升现场可编程闸阵列(FPGA)10%的效能,对于日新月异的网络、电信或云端基础建设来说,速度有些慢,对系统设计人员来说,设计过程中将遭遇不少挑战。

2015-06-23 09:50:17 1004

1004 引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2022-07-25 10:13:44 4067

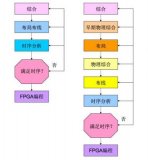

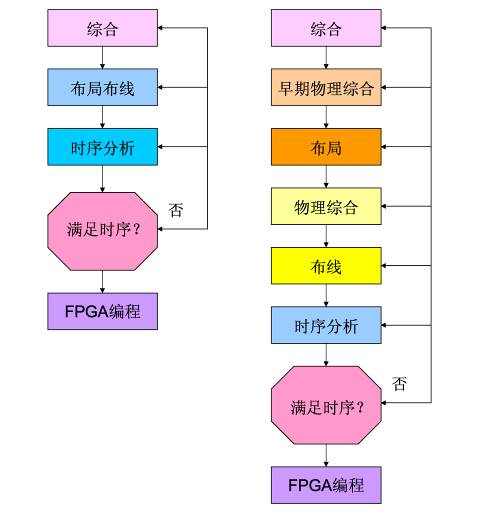

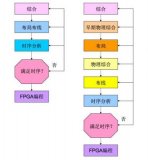

4067 综合就是把Verilog、VHDL转换成网表的过程。综合按照是否考虑物理布局信息可分为逻辑综合和物理综合。

2023-08-09 09:51:15 638

638

工艺技术的发展极大地提高了 FPGA 器件的密度。多个赛灵思® VirtexTM 系列中都包含了超过 1 百万系统门的器件。这种器件密度的提高和 300 mm 晶圆片的使用,为 FPGA 批量生产创造了条件。

2011-10-01 01:10:03 1627

1627

我国的实际情况以及国内领先的FPGA产品可以发现相关技术在未来的发展方向,对我国科技水平的全面提高具有非常重要的推动作用。^ [2]^

与传统模式的芯片设计进行对比,FPGA 芯片并非单纯局限于研究

2023-05-30 20:38:46

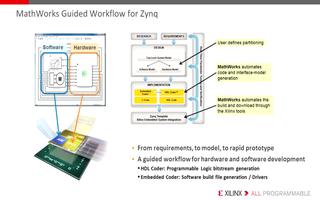

流程效率有高度的要求等。鉴于日益升温的FPGA市场,EDA业者加码布局,加速FPGA设计进程、提高验证效率,帮助广大工程师在短时间内进行准确无误的设计。 FPGA市场需求急升 Cadence频祭杀手锏

2013-04-17 11:20:14

设计,对FPGA的开发是非常重要的。充分利用了这些EDA工具的优点,能够提高开发效率和系统性能。表中列出的每种EDA工具都有自己的特点。一般由FPGA厂商提供的集成开发环境,如Altera

2017-11-22 09:37:02

本人初学者,看了些资料,说FPGA每次综合生成的电路结构貌似不一样,这会不会产生某些潜在的影响?比如某次生成的电路很健康,结果第二次综合生成的电路,虽然没错,但没有第一次好了。。。

2013-10-26 22:57:20

apex20ke_atoms.v编译到其中。2:在图形界面中的Load Design对话框中装入仿真设计时,在Verilog 标签下指定预编译库的完整路径。(见下图)逻辑综合目前可用的FPGA综合工具

2020-05-15 07:00:00

FPGA设计-提高班培训课堂

2012-08-02 23:03:17

FPGA设计提高教程Advanced FPGA Design.FPGA设计提高教程Advanced FPGA Design.

2012-08-11 16:19:12

语言的可综合子集”有如下帮助: 1. 通过仿真,可以观察HDL语言在FPGA中的逻辑行为。 2. 通过综合,可以观察HDL语言在FPGA中的物理实现形式。 3. 通过时序分析,可以分析HDL语言在

2016-08-26 09:43:58

语言的可综合子集”有如下帮助: 1. 通过仿真,可以观察HDL语言在FPGA中的逻辑行为。 2. 通过综合,可以观察HDL语言在FPGA中的物理实现形式。 3. 通过时序分析,可以分析HDL语言在

2016-09-14 11:02:13

FPGA高级时序综合教程The UCF FileUCF =用户约束文件( User Constraints File )可以用文本编辑器和XilinxConstraints Editor (GUI

2012-08-11 11:28:50

fpga高手经验谈doc文档在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理

2012-08-11 11:30:39

FPGA设计重利用方法(Design Reuse Methodology)SRAM工艺FPGA的加密技术大规模FPGA设计中的多点综合技术定点乘法器设计(中文)你的PLD是亚稳态吗_设计异步多时钟系统的综合以及描述技巧使用retiming提高FPGA性能

2014-04-30 23:57:42

提高FPGA的时钟精度的方案有哪些,哪位大神告诉一下

2015-10-13 08:22:31

随着FPGA密度的增加,系统设计人员能够开发规模更大、更复杂的设计,从而将密度优势发挥到最大。这些大规模设计基于这样的设计需求——需要在无线通道卡或者线路卡等现有应用中加入新功能,或者通过把两种芯片功能合并到一个器件中,减小电路板面积,或者针对新应用开发新设计。

2019-09-03 07:48:08

物理综合与优化的优点有哪些物理综合与优化流程看了就知道物理综合与优化示例

2021-04-08 06:18:15

):Xilinx_ISE_DS_Update_13.1_O.40e.2.1Linux平台:CentOS 5.6(RHEL 5.6克隆)运行物理综合......FATAL_ERROR:1 :: 78:1.3- 物理综合失败。流程将终止。 有关此问题的技术支持

2018-10-12 14:28:14

Arm AMBA协议集中,协议的实现是直接物理综合而成的吗?还会有其自身的固件吗?

2022-09-19 14:52:16

本视频是MiniStar FPGA开发板的配套视频课程,主要通过工程实例介绍Gowin的物理约束和时序约束,课程内容包括gowin的管脚约束及其他物理约束和时序优化,以及常用的几种时序约束。 本

2021-05-06 15:40:44

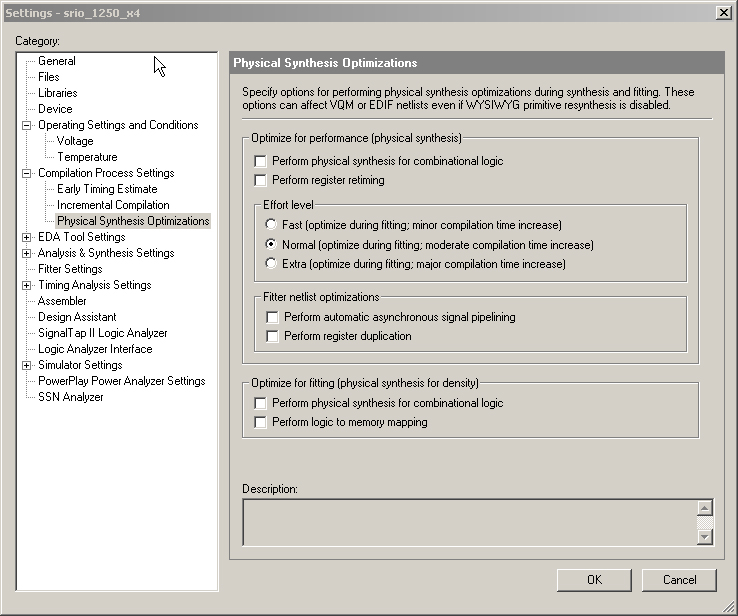

综合是将我们的设计转化为FPGA可以读懂的配置文件的第一个步骤。本文努力从0基础开始向大家说明综合的基本知识和高级技巧。话说所有的功能都有它应用的环境。在了解某个按钮选项有某个功能的时候,我们更应该

2018-08-08 10:31:27

以及可综合的代码设计风格6. SignalTap II在线逻辑分析仪使用方法7. Logic Lock逻辑锁定工具使用技巧 第四阶段:随着FPGA芯片的性能和密度不断提高, 基于FPGA的SOPC系统

2018-09-19 11:34:03

`关于MOS管一直都是电路设计的工程师热衷讨论的话题之一,而厂家更想看到的是更换MOS管能够提高产品效能的作用,而在实际工作中,各种电器设备时,遇到元器件损坏应该采用相同型号的元件进行更换。有些时候

2019-02-23 16:23:40

,降低设备或元件的性能,严重时会对内部设备造成损坏。因此,研究有空屏蔽腔对电磁干扰的电磁屏蔽效能有重要的实际意义和价值。从以往的研究看,提高屏蔽效能的方法有很多,如相同面积下,孔阵的屏蔽效能优于单孔

2019-07-24 08:18:41

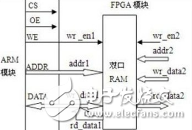

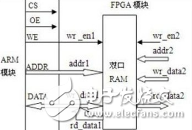

、串口通信等的交互和控制。图 2 FPGA程序设计结构层次图综合顶层模块得到如下如3所示的RTL原理图,图中5个红框对应上述五大模块。图 3 系统顶层综合RTL原理图2.3 子模块设计2.3.1 数据

2018-08-07 10:08:19

大规模FPGA设计中的多点综合技术

2012-08-17 10:27:46

通过学习opencv图像库编程,了解如何借助第三方库函数完成一个综合程序设计。

2021-12-23 08:11:05

本文基于Viitex-5 LX110验证平台的设计,探索了高性能FPGA硬件系统设计的一般性方法及流程,以提高FPGA的系统性能。

2021-04-26 06:43:55

对于设计者来说,当然希望我们设计的电路的工作频率(在这里如无特别说明,工作频率指FPGA片内的工作频率)尽量高。我们也经常听说用资源换速度,用流水的方式可以提高工作频率,这确实是一个很重要的方法

2018-08-08 11:16:37

影响FPGA设计周期生产力的最大因素是什么?如何提高FPGA设计生产力?

2021-05-06 09:26:04

随着FPGA的容量、性能以及可靠性的提高及其在消费电子、汽车电子等领域的大规模应用,FPGA设计的安全性问题越来越引起人们的关注。

2019-09-30 07:23:06

随着FPGA的容量、性能以及可靠性的提高及其在消费电子、汽车电子等领域的大规模应用,FPGA设计的安全性问题越来越引起人们的关注。

2019-10-18 07:12:32

个好的综合网表同时也可以提高后端物理实现的质量和效率。中科芯云微电子科技有限公司(青岛EDA中心)联合Synopsys、青岛集成电路人才创新培养联盟、青岛微电子创新中心将举办“Design

2021-06-23 06:59:32

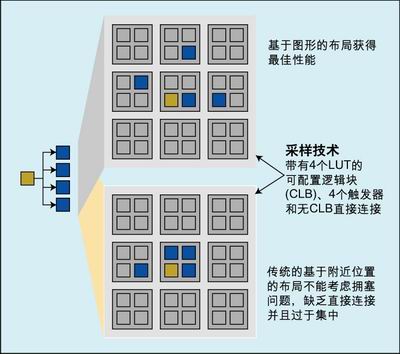

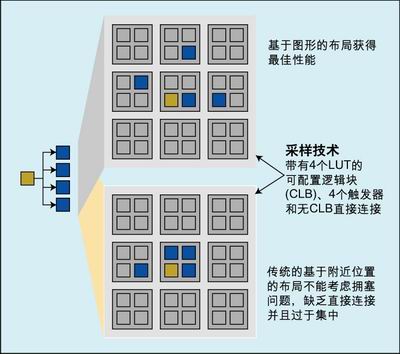

如何使用基于图形的物理综合加快FPGA设计时序收敛?

2021-05-06 09:19:08

如何去选择新MOS管来提高产品效能?选择新的MOS管要考虑哪些参数?

2021-06-08 07:09:13

如何将人工智能应用到效能评估系统软件中去解决

华盛恒辉效能评估系统是一种非常实用的管理工具,它可以帮助组织和企业掌握其运营状况,优化业务流程,提高效率和生产力。然而,随着人工智能的迅猛发展

2023-08-30 12:58:14

部分 AT32 带有非零等待区,当代码超过零等待区后,且时钟不高于 72MHz,读取Flash 的效能会降低。此时不改变外围时钟,如何快速修改程序以提高 Flash 效能?

2023-10-20 08:26:10

AT32 Performance Optimization描述了如何通过软件方法提高AT32的运行效能。

2023-10-19 07:11:47

如何采用FPGA提高广播应用的集成度?

2021-04-29 06:04:54

观察HDL语言在FPGA中的逻辑行为。 2. 通过综合,可以观察HDL语言在FPGA中的物理实现形式。 3. 通过时序分析,可以分析HDL语言在FPGA中的物理实现特性。 对于FPGA设计者来说,用好

2012-02-28 14:04:13

新型处理技术及其系统优势是还说呢么废印制电路板的物理回收及综合利用技术面临的难点是什么?

2021-04-25 06:25:17

微软(Microsoft)正探索将现场可编程闸阵列(FPGA)导入其资料中心伺服器的可能性。虽然目前这还只是一个初步的概念,但它可望缓减目前在网路效能所面临的挑战。 微软伺服器工程副总裁

2019-06-20 07:23:09

怎么借助物理综合提高FPGA设计效能?

2021-05-07 06:21:18

随着FPGA的容量、性能以及可靠性的提高及其在消费电子、汽车电子等领域的大规模应用,FPGA设计的安全性问题越来越引起人们的关注。相比其他工艺FPGA而言,处于主流地位的SRAM工艺FPGA有一些

2019-08-23 06:45:21

怎么在PLD开发中提高VHDL的综合质量?利用Quartus II软件的开发流程有哪些步骤?

2021-05-08 09:23:07

汽车制造商们坚持不懈地改进车内舒适性、安全性、便利性、工作效能和娱乐性,反过来,这些努力又推动了各种车内数字技术的应用。然而,汽车业较长的开发周期却很难跟上最新技术的发展,尤其是一直处于不断变化中

2019-07-15 08:17:56

FPGA。如果我必须操纵网表,或者我可以将GTECH综合网表和dw_foundation用于FPGA,请有人告诉我吗?如果可以的话,请与文件分享。先谢谢你。

2020-07-08 08:53:36

物理综合与优化的优点是什么?物理综合与优化有哪些流程?物理综合与优化有哪些示例?为什么要通过物理综合与优化去提升设计性能?如何通过物理综合与优化去提升设计性能?

2021-04-14 06:52:32

介绍使用现代EDA手段设计核物理实验常用仪器——定标器的原理和实现方法。新的定标器利用FPGA 技术对系统中大量电路进行集成,结合AT89C51 单片机进行控制和处理,并增加数据存

2009-05-14 16:07:06 19

19 今天每一个工程人员都把精力放在效能上面,即用最少的资源做最多的事情。Altera的PLD 开发软件平台工具Quartus II 能帮助工程人员提高效能,它是如何实现的呢?概括起来说就

2009-11-30 14:37:26 37

37 针对当前C4ISR在炮兵指挥信息系统中作用的不断提高,分析并提出了炮兵C4ISR通信分系统的效能指标体系,利用模糊综合评判方法,定性和定量分析相结合,对该分系统效能进行了静态评

2010-02-22 15:44:46 8

8 ASIC和FPGA设计中的多点综合技术

尽管在技术发展的每一个时刻做出精确的预言是困难的,但ASIC和FPGA所集成的门数仍象数年前INTEL的Gordon Monre预言的那样平均每18个月增加一倍.

2010-06-19 10:05:09 11

11 FPGA验证是基于VHDL的VLSI设计中非常重要的一个环节。用户设计的电子系统首先必须是可综合的,综合之后再通过FPGA原型验证,即可在物理层面对用户设计完成实物验证。通过FPGA验证

2010-07-12 19:13:59 28

28

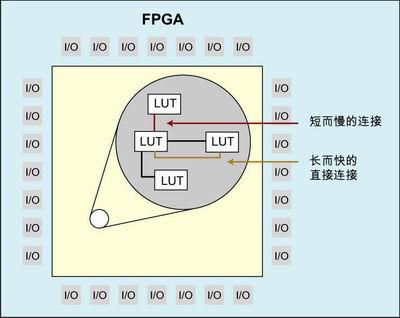

传统的综合技术越来越不能满足当今采用 90 纳米及以下工艺节点实现的非常大且复杂的 FPGA 设计的需求了。问题是

2009-06-20 10:34:53 545

545

摘要:介绍使用现代EDA手段设计核物理实验常用仪器——定标器的原理和实现方法。新的定标器利用FPGA技术对系统中大量电路进行集成,结合AT89C51单片机进行控制

2009-06-20 15:06:42 732

732

面向ASIC和FPGA设计的多点综合技术

随着设计复杂性增加,传统的综合方法面临越来越大的挑战。为此,Synplicity公司开发了同时适用于FPGA或 ASIC设计的多点综合技术,它

2009-12-26 14:34:33 563

563 无线通信系统综合抗干扰效能评估是现代通信对抗过程中的重要环节。该文对无线通信对抗双方的博弈机理进行了研究,基于层次分析法,构造了敌对电磁环境下的无线通信系统指标评

2011-03-18 14:23:03 38

38 Synplify /Synplify Pro简介 综合工具在FPGA的设计中非常重要,类似于C语言的编译器将C语言翻译成机器能执行的代码,综合工具将HDL描述的语句转换为EDA工具可以识别的格式(EDF格式),对

2011-03-30 10:15:27 163

163 本文介绍了在大规模FPGA设计中可以提高综合效率和效果的多点综合技术,本文适合大规模FPGA的设计者和Synplify pro的用户阅读。

2012-01-17 10:36:37 38

38 开放计算语言(OpenCL)编程模型与Altera的并行FPGA体系结构相结合,实现了功能强大的系统加速解决方案。面向OpenCL的Altera SDK为您提供了设计环境,工程师很容易在FPGA上实现OpenCL应用。

2012-11-06 14:56:42 1091

1091 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 基于FPGA的系统提高电机控制性能 。

2016-01-07 15:00:19 24

24 FPGA设计提高班培训课堂PPT_V1.0

2016-05-10 11:24:33 23

23 米特拉表示,“如果利用碳纳米管晶体管取代硅晶体管,效能比可提高1000倍。”

2016-08-22 14:03:54 986

986 基于FPGA的EDA综合实验系统设计_赵刚

2017-03-19 11:38:26 2

2 进行中小型批量生产,能支持非常强大的原型设计与验证技术,以实现DSP算法的实时仿真。但为FPGA和ASIC创建可移植性算法IP也面临着诸多挑战与要求。 本文将介绍如何通过ESL综合技术大幅缩短在FPGA或ASIC上实现算法所需的时间,并简化相关工作。 FPGA和ASIC之间RTL移植所面

2017-11-06 13:55:11 0

0 ,帮助设计团队集中精力做好创造性工作。下面我们就来看看FPGA工具流程的演进发展,了解一下现代FPGA团队是如何利用RTL分析、约束生成和综合导向来减少设计迭代的。

2017-11-22 08:52:51 7216

7216

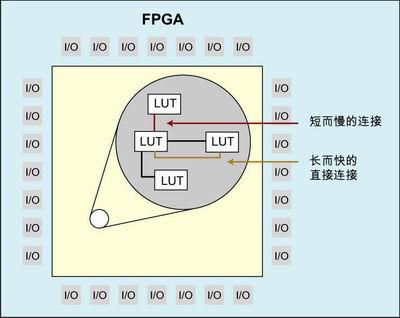

(IPO,In-place Optimization) 以及具有物理意识的综合 (physically-aware synthesis) 等。然而,这些从 ASIC 得来的综合算法并不适用于 FPGA 的常规架构和预定义的布线资源。

2018-11-28 08:12:00 1431

1431

了解使用高级综合的英特尔®FPGA上的实时图像处理。

2018-11-08 06:26:00 2811

2811 单片机是基于FLASH结构的,所以单片机上电直接从本地FLASH中运行。但SRAM 架构的FPGA是基于SRAM结构的,掉电数据就没了,所以需要借助外部电路来配置运行的数据,其实我们可以借助Vivado来学习FPGA的各种配置模式。

2018-11-05 15:12:57 7298

7298 关键词:FPGA , 设计效能 随着FPGA密度的增加,系统设计人员能够开发规模更大、更复杂的设计,从而将密度优势发挥到最大。这些大规模设计基于这样的设计需求——需要在无线通道卡或者线路卡等现有

2019-02-18 17:13:01 232

232

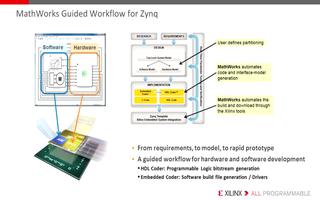

套件和参考设计, 此主题将能让您更深刻地了解如何借助Xilinx® FPGA 和MATLAB技术更轻松、更快速地开发各种机器

2019-12-25 07:08:00 2242

2242

滕旭云宣告推出FPGA云效能器,这是我国第一个高功用异构核算基础设施,以云效能的办法将FPGA扩展到更多企业,大型公司可以运用FPGA进行长时间支付。

2019-08-13 17:49:29 433

433 引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2021-04-27 10:36:59 3125

3125

综合性CPLD/FPGA软件Quartus 13.0下载

2021-09-12 09:35:13 17

17 如何借助LDO提高降压转换器的轻负载效率 – I

2022-11-04 09:52:02 0

0 如何提高电路工作频率 对于设计者来说,我们当然希望我们设计的电路的工作频率(在这里如无特别说明,工作频率指FPGA 片内的工作频率)尽量高。我们也经常听说用资源换速度,用流水的方式可以提高

2022-11-16 12:10:02 713

713 利用工具将RTL代码转化为门级网表的过程称为逻辑综合。综合一个设计的过程,从读取RTL代码开始,通过时序约束关系,映射产生一个门级网表。

2022-11-28 16:02:11 1822

1822 FPGA高级时序综合教程

2023-08-07 16:07:55 3

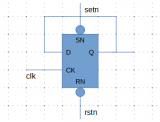

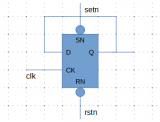

3 有朋友提问,下面的代码为什么在DC里可以综合成DFF,而在FPGA上却综合成了latch。

2024-02-20 16:12:34 166

166

电子发烧友App

电子发烧友App

评论