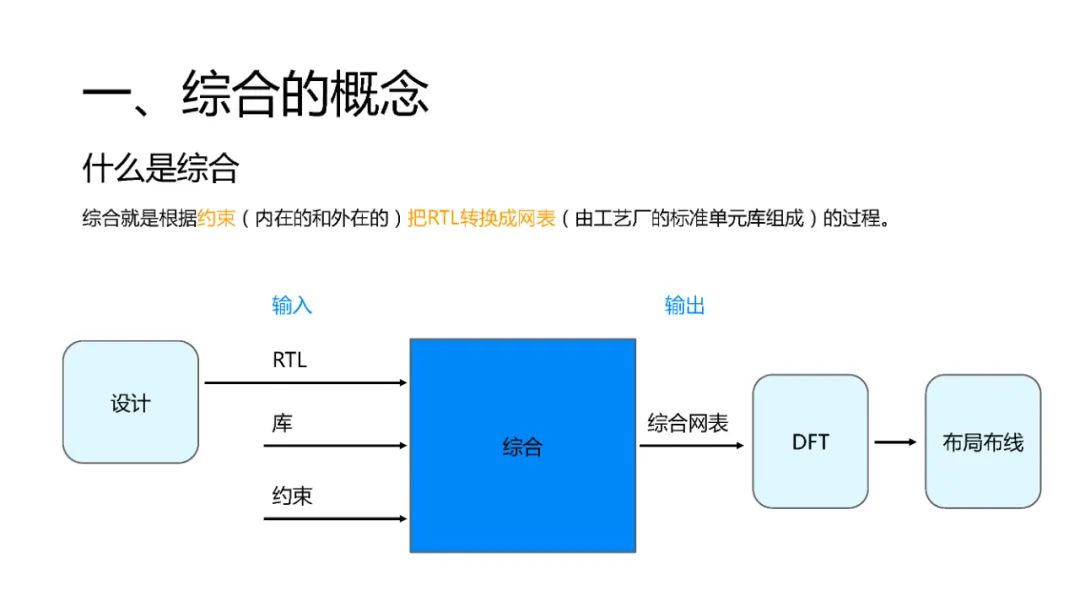

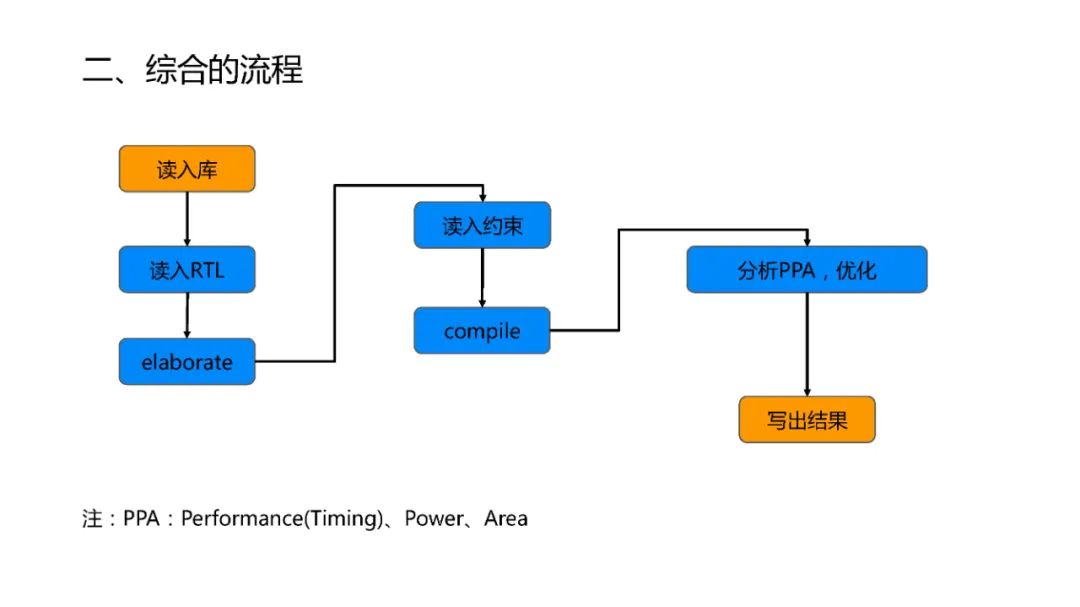

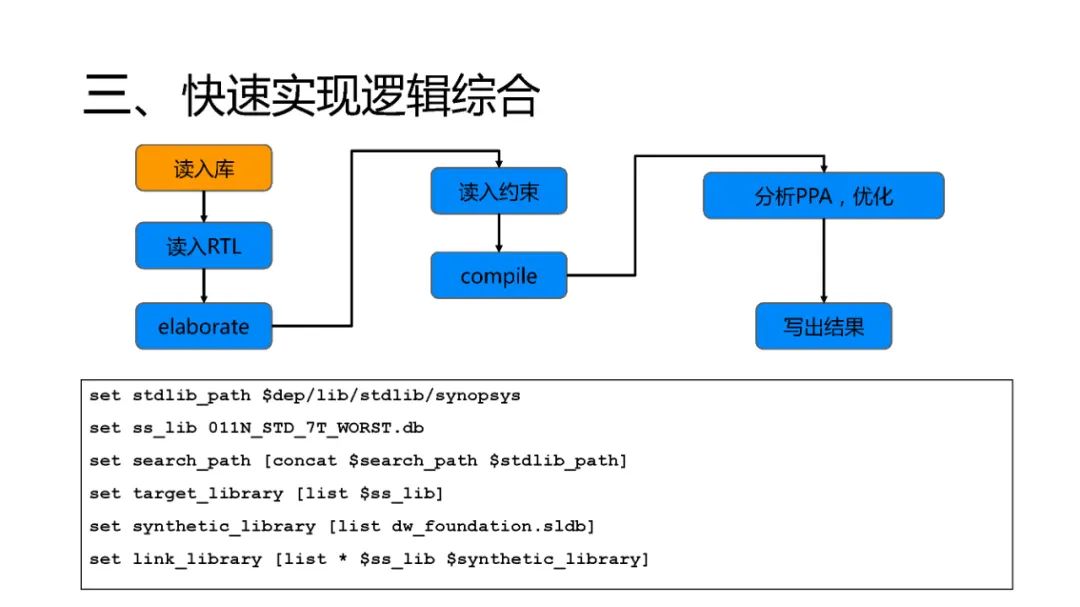

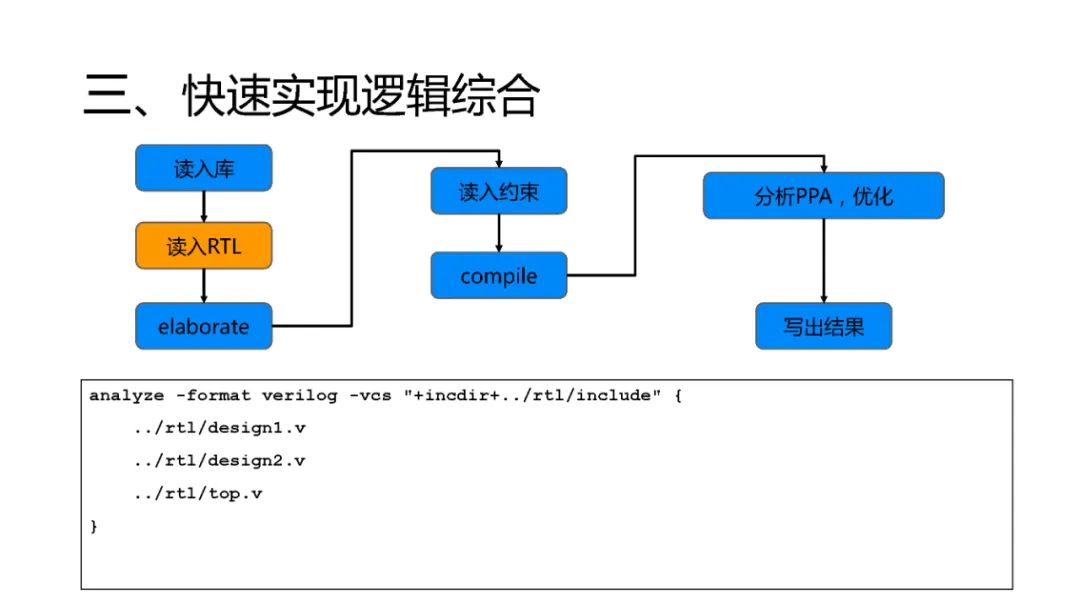

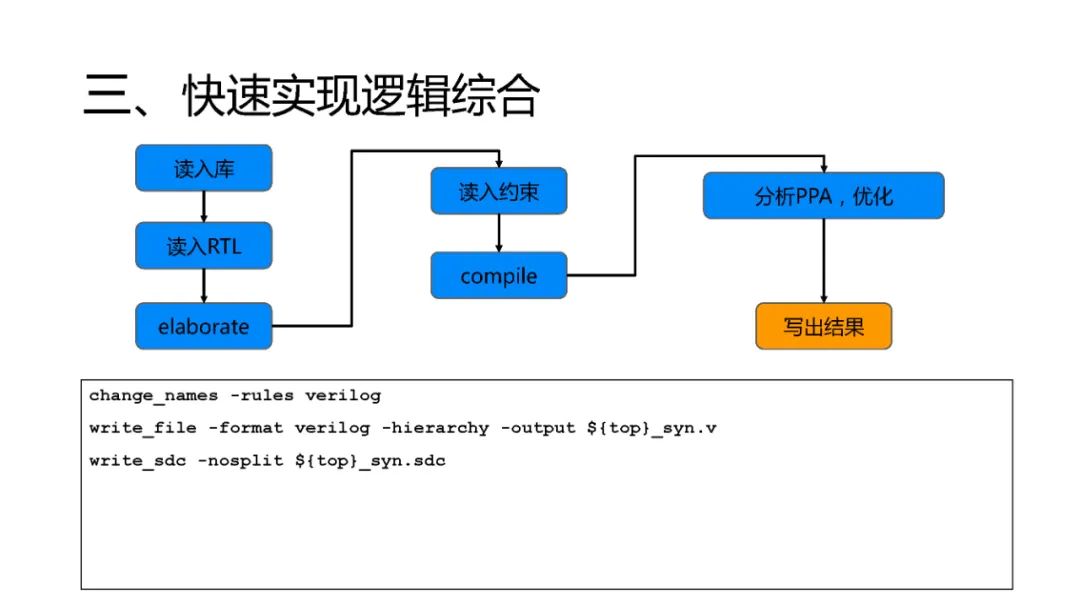

综合就是把Verilog、VHDL转换成网表的过程。综合按照是否考虑物理布局信息可分为逻辑综合和物理综合。逻辑综合通常用来做工艺较老的项目,或者较新工艺的面积和时序的评估。因此,前端设计工程师掌握逻辑综合的流程和相关EDA工具是必须的技能,可用来评估和提升设计代码的质量。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

转换器

+关注

关注

27文章

9365浏览量

155066 -

EDA工具

+关注

关注

5文章

275浏览量

33788 -

Verilog语言

+关注

关注

0文章

113浏览量

8721 -

VHDL电路

+关注

关注

0文章

4浏览量

1483

原文标题:逻辑综合的流程和命令

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

基于ATM理念的UTRAN传输架构简析

基于ATM理念的UTRAN传输架构简析:UTRAN(UMTS无线接入网)系统传输网承载其内部业务传送及至CN(核心网)侧的业务汇聚功能,考虑3G网络内,话音、媒体流及Internet等数据业务的多样

发表于 10-22 10:49

•15次下载

EPON技术简析

EPON技术简析

EPON是一个新技术,用于保证提供一个高品质与高带宽利用率的应用。

EPON在日本、韩国、中国大陆、中国台湾及其它以以太网络为基础的地区都

发表于 01-22 10:43

•1110次阅读

简析BGA封装技术与质量控制

简析BGA封装技术与质量控制

SMT(Surface Mount Technology)表面安装技术顺应了电子产品小型化、轻型化的潮流趋势,为实现电子

发表于 03-30 16:49

•1776次阅读

DC逻辑综合

芯片综合的过程:芯片的规格说明,芯片设计的划分,预布局,RTL 逻辑单元的综合,各逻辑单元的集成,测试,布局规划,布局布线,最终验证等步骤。设计流程

发表于 12-29 16:28

•25次下载

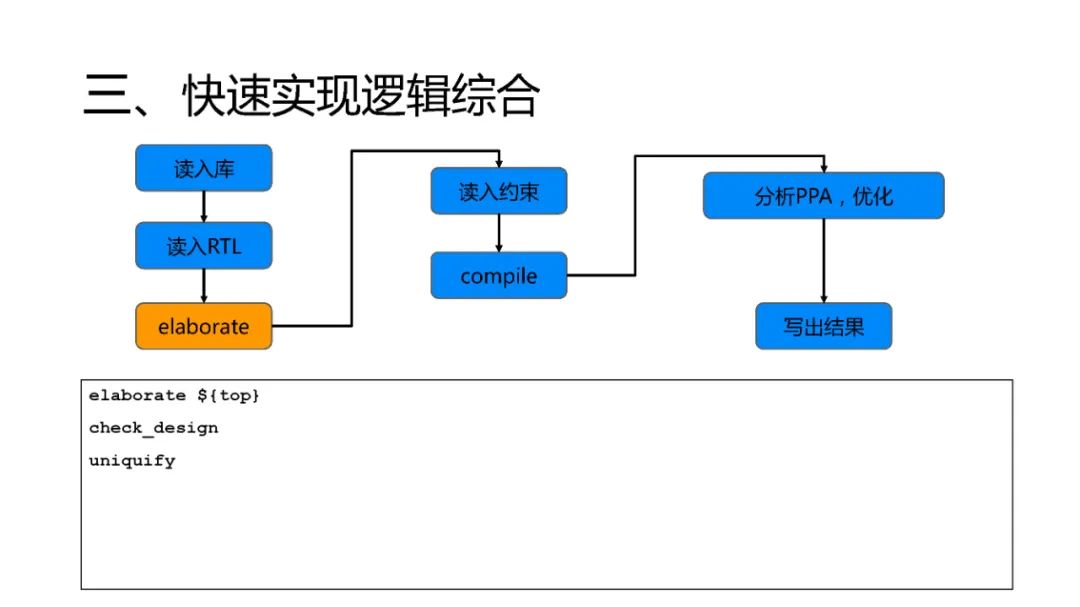

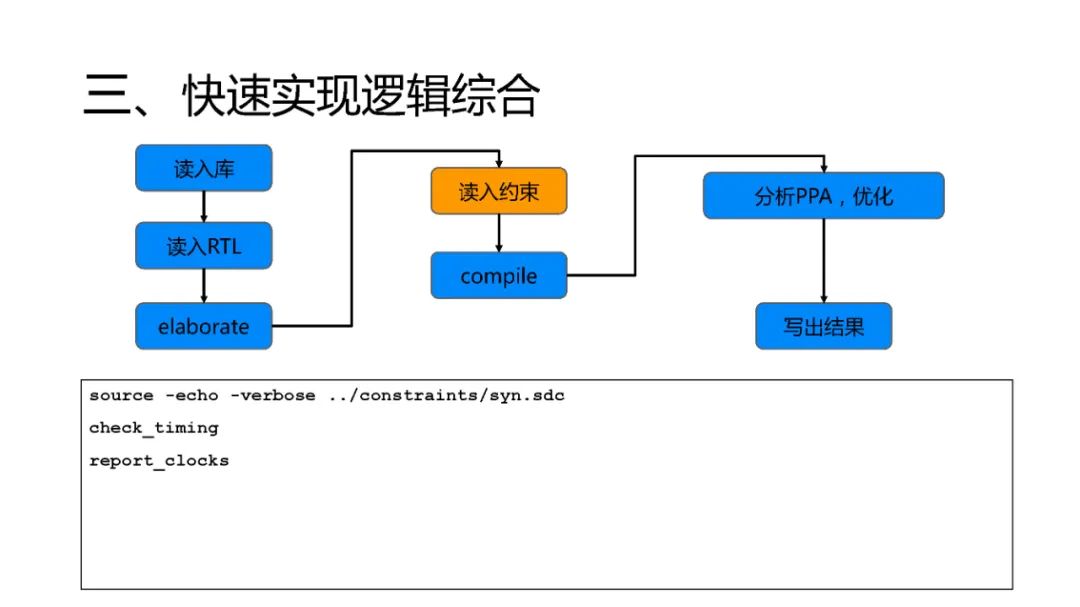

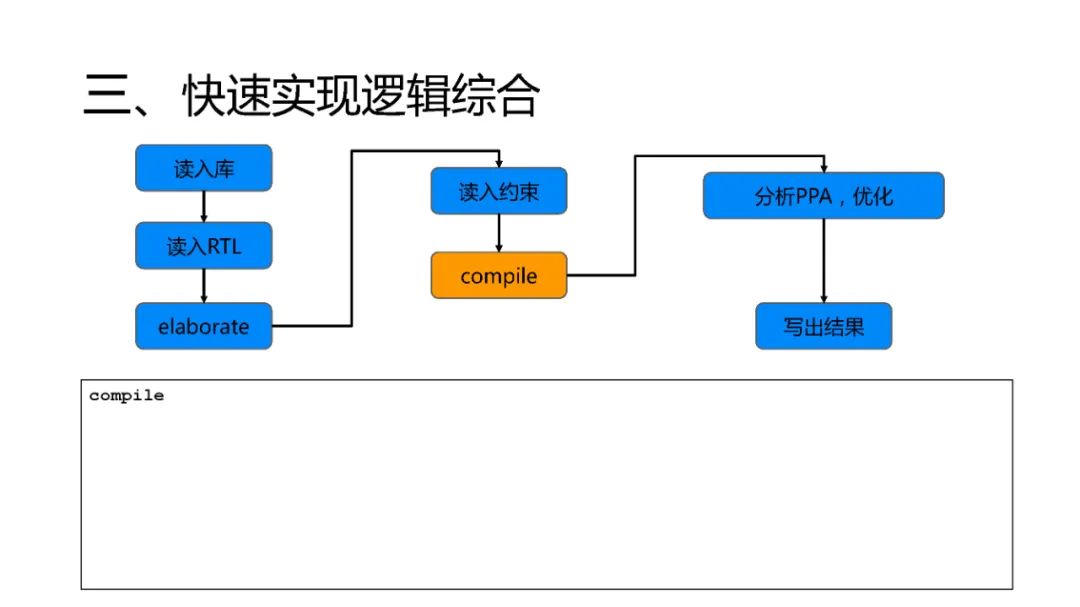

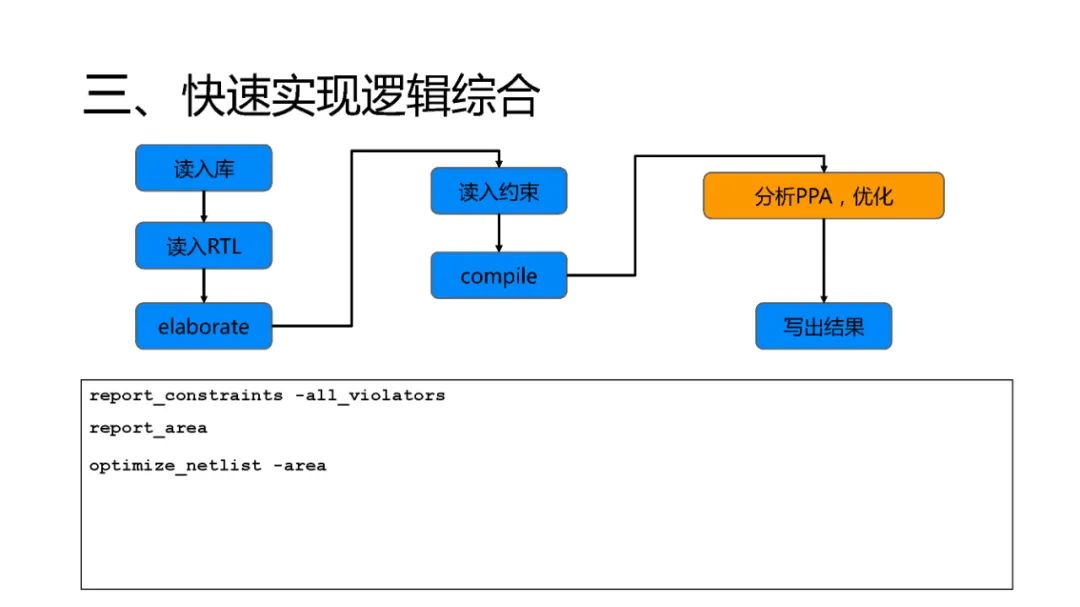

逻辑综合的流程和命令简析

逻辑综合的流程和命令简析

评论