作者:Mculover666 1.实验目的 通过例程探索Vivado HLS设计流 用图形用户界面和TCL脚本两种方式创建Vivado HLS项目 用各种HLS指令综合接口 优化Vivado HLS

2020-12-21 16:27:21 3153

3153 样例方便大家熟悉其开发流程。另外关于HLS的使用介绍,Xilinx官方提供了2个重要开发文档ug871 和 ug902。里面详细介绍了包括怎么建立HLS 工程

2020-10-14 15:17:19 2881

2881

HLS任务级编程第一篇文章可看这里: HLS之任务级并行编程 HLS的任务级并行性(Task-level Parallelism)分为两种:一种是控制驱动型;一种是数据驱动型。对于控制驱动

2023-07-27 09:22:10 732

732

HLS的任务级并行性(Task-level Parallelism)分为两种:一种是控制驱动型;一种是数据驱动型。

2023-07-27 09:21:40 579

579

该项目通过一个示例演示了 HLS 中组合电路对设计的影响。

2023-11-03 09:04:09 360

360

HLS-15R - TAK-TY CONTINUOUS 15FT, ROLL HLS SERIES - PANDUIT CORP.

2022-11-04 17:22:44

请教一下,我在HLS里面要将以下程序生成IP核,C Synthesis已经做好了,但是在export RTL的时候一直在运行

int sum_single(int A int B

2023-09-28 06:03:53

HLS高阶综合(highlevelsynthesis)在被广泛使用之前,作为商业技术其实已经存在了20多年。设计团队对于这项技术可以说呈现出两极化的态度:要么坚信它是先进技术之翘楚,要么对其持谨慎

2021-07-10 08:00:00

流水线指令

pragma HLS pipeline

通过流水线提高性能是计算机架构设计的8个伟大思想之一,不管是硬件设计还是软件设计,流水线设计(pipeline)都能够用更多的资源来实现高速

2023-12-31 21:20:08

1、HLS最全知识库介绍高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。对于AMD Xilinx而言

2022-09-07 15:21:54

文件。 把上述2个技术性很强的概念表述翻译下。就是说H5是一种HTML的新标准,这种新标准支持原生的video标签和video控件。因为video控件标签又支持HLS协议播放。 所以得以实现在手机移动

2017-06-01 14:48:07

, Mat 类型的关系和VivadoHLS中图像hls::Mat类型介绍OpenCv中常见的与图像操作有关的数据容器有Mat,cvMat和IplImage,这三种类型都可以代表和显示图像,但是,Mat类型

2021-07-08 08:30:00

我在Vivado HLS中有以下错误的合成。我试图更新许可证文件但没有成功。请给我一个建议。@E [HLS-72]许可证签出不成功。确保可以访问许可证或通过环境变量指定适当的许可证。 执行

2020-05-20 09:13:21

1.实验目的通过例程探索Vivado HLS设计流用图形用户界面和TCL脚本两种方式创建Vivado HLS项目用各种HLS指令综合接口优化Vivado HLS设计来满足各种约束用不用的指令来探索

2021-11-11 07:09:49

vivado可以正常使用,但是HLS总是出现图片中的错误。请问该如何解决?谢谢!

2020-08-12 01:36:19

你好!如果我想使用vivado hls来合成具有axi流接口的代码,是否有必须遵循的标准编码风格?

2020-04-21 10:23:47

HLS高阶综合(highlevelsynthesis)在被广泛使用之前,作为商业技术其实已经存在了20多年。设计团队对于这项技术可以说呈现出两极化的态度:要么坚信它是先进技术之翘楚,要么对其持谨慎

2021-07-06 08:00:00

,大大减少了使用传统RTL描述进行FPGA开发所需的时间。本章包括以下几个部分:1.1高层综合简介1.2HLS设计流程1.3接口综合1.4算法综合1.5HLS库1.1高层综合简介在介绍HLS之前,我们

2020-10-10 16:44:42

)对正点原子FPGA感兴趣的同学可以加群讨论:8767449005)关注正点原子公众号,获取最新资料第四章呼吸灯实验在前面两个实验中我们学习了如何通过Vivado HLS工具来生成带有一个

2020-10-10 17:01:29

【资料分享】Vivado HLS学习资料

2013-11-02 11:21:14

HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。LUT 或 SICELUT 或 SICE是构成了 FPGA 的区域。它的数量有限,当它用完时,意味着您的设计太大了!BRAM 或

2022-09-09 16:45:27

我们不允许在公司使用linux环境。我们期待windows bug补丁。任何人都可以告诉HLS 18.1 Pro for Windows的发布时间表吗?以上来自于谷歌翻译以下为原文We

2018-10-11 14:19:49

模拟过程完成没有0错误,但在合成期间显示错误。我无法找到错误。我在合成期间在HLS工具中收到这样的错误“在E中包含的文件:/thaus / fact_L / facoriall

2020-05-21 13:58:09

嗨,大家好,我有一个问题,在VIVADO HLS 2017.1中运行C \ RTL协同仿真。我已成功运行2014和2016版本的代码。任何人都可以告诉我为什么报告NA仅用于间隔

2020-05-22 15:59:30

FPGA的HLS案例开发|基于Kintex-7、Zynq-7045_7100开发板前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx

2021-02-19 18:36:48

你好,我使用Vivado HLS生成了一个IP。从HLS测量的执行和测量的执行时间实际上显着不同。由HLS计算的执行非常小(0.14 ms),但是当我使用AXI计时器在真实场景中测量它时,显示3.20 ms。为什么会有这么多差异? HLS没有告诉实际执行时间?等待回复。问候

2020-05-05 08:01:29

嗨〜 如何在HLS 14.3中编写pow功能? HLS 14.3不支持exp和pow功能。我在我的代码中写了“#include math.h”。但是,它不起作用。 另外,我想知道C代码中

2019-03-05 13:40:09

编译与仿真 253.3 IP 核测试 27前 言本文主要介绍 HLS 案例的使用说明,适用开发环境: Windows 7/10 64bit、Xilinx Vivado2017.4 、Xilinx

2023-01-01 23:51:35

目 录前 言 31 HLS 开发流程说明 51.1 HLS 工程导入 51.2 编译与仿真 61.3 综合 81.4 IP 核封装 101.5 IP 核测试 14

前 言本文主要介绍 HLS

2023-08-24 14:40:42

目 录前 言 31 HLS 开发流程说明 51.1 HLS 工程导入 51.2 编译与仿真 61.3 综合 81.4 IP 核封装 101.5 IP 核测试 14前 言本文主要介绍 HLS

2023-01-01 23:52:54

目 录5 sobel_demo 案例 395.1 HLS 工程说明 405.2 编译与仿真 435.3 IP 核测试 45

前 言本文主要介绍 HLS 案例的使用说明,适用开发环境: Windows

2023-08-24 14:54:01

目 录5 sobel_demo 案例 395.1 HLS 工程说明 405.2 编译与仿真 435.3 IP 核测试 45前 言本文主要介绍 HLS 案例的使用说明,适用开发环境: Windows

2023-01-01 23:46:20

前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx

2021-11-11 09:38:32

的经验几乎为0,因此我想就如何解决这个问题提出建议。这就是我的想法:1 - 首先,用Vivado HLS转换VHDL中的C代码(我现在有一些经验)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

我照着xapp1167文档,用HLS实现fast_corners的opencv算法,并生成IP。然后想把这个算法塞到第三季的CH05_AXI_DMA_OV5640_HDMI上,这个demo里

2017-01-16 09:22:25

您好我有一个关于vivado hls的问题。RTL是否来自xivix FPGA的vivado hls onyl?我们可以在Design Compiler上使用它进行综合吗?谢谢

2020-04-13 09:12:32

`在直播软件开发过程中,我们可能会遇到一些困惑。像是对于流媒体协议的选择,如HTTP-FLV、WebRTC,RTMP,HLS及其它私有协议等,到底哪个比较合适?哪种协议可以用在PC平台上?哪种协议在

2019-08-21 14:34:39

你好,我有一个与switch语句的合成有关的问题。我开始使用Vivado HLS并且我已经创建了一个小的file.cpp,仅用于学习,但是当Vivado HLS合成文件时,我没有得到任何开关语句

2019-11-05 08:21:53

请问Vivado HLS出现这种情况是什么原因呢

2021-06-23 06:13:13

Vivado HLS设计流程是怎样的?

2021-06-17 10:33:59

嗨伙计,在我的PC Vivado设计套件2015.2和SDK 2015.2工作,但只有vivado HLS 2015.2没有打开,这就是为什么我想重新安装Vivado HLS 2015.2。如何下载

2018-12-27 10:57:49

描述 HLS系列霍尔效应液位传感器(HLS)是用于连续液位监测的定制设计解决方案,适用温度范围宽广,可校准定制编程输出以适应各种几何形状的液位储存箱。HLS系列是一款智能传感器,带有板载

2021-07-14 14:08:24

Synopsys天宣布推出其Synphony HLS (High Level Synthesis)解决方案

新思科技公司,今天宣布推出其Synphony HLS (High Level Synthesis)解决方案。该解决方案集成了M语言和基于模型的综合

2009-11-04 16:55:53 962

962 介绍如何设计HLS IP,并且在IP Integrator中使用它来作一个设计——这里生成两个HLS blocks的IP,并且在一个FFT(Xilinx IP)的设计中使用他们,最终使用RTL

2017-02-07 17:59:29 4179

4179

高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

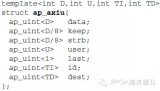

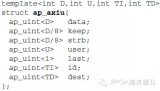

Interface:内存访问型的端口协议 接下来的几章,我们重点介绍下AXI接口类型如何在HLS中实现,首先看Lite端口: AXI-Lite端口的实现 使用Vivado HLS的AXI-Lite端口,可以实现: 把多个port打包到一组AXI-

2017-02-08 03:27:11 475

475

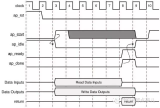

在之前HLS的基本概念1里有提及,HLS会把c的参数映射成rtl的端口实现。本章开始总结下HLS端口综合的一些知识。 1.HLS综合后的rtl端口大体可以分成2类: Clock Reset端口

2017-02-08 03:29:11 544

544

在上一章HLS提到了axi lite端口的综合方式,以及directive的一些语法规则。这一章里面,介绍一下axi-stream和full axi端口的综合实现问题。 1. AXI-Stream

2017-02-08 03:31:04 414

414

在上一章HLS提到了axi lite端口的综合方式,以及directive的一些语法规则。这一章里面,介绍一下axi-stream和full axi端口的综合实现问题。 AXI FULL端口的实现

2017-02-08 03:35:34 776

776

个总结回顾,看看HLS支持的端口类型分类: 下面详细介绍下BlockLevel Interface ap_ctrl_hs: 是默认的端口类型,它综合出来的端口会有额外的4个系统控制信号,如下所示: 其端口

2017-02-08 03:39:11 354

354

相信通过前面5篇fir滤波器的实现和优化过程,大家对HLS已经有了基本的认识。是时候提炼一些HLS的基本概念了。 HLS支持C,C++,和SystemC作为输入,输出为Verilog(2001

2017-02-08 05:23:11 674

674

1. HLS仅支持一个主时钟和复位 因此,目前还没有办法完全用HLS做出一个多时钟域的设计。 2. 对于同一个参数,HLS可以综合出各种各样的端口类型 这也需要额外的约束去进行设置 3. 虽然

2017-02-08 05:24:31 271

271

HLS工具 以个人的理解,xilinx将HLS(高层次综合)定位于更方便的将复杂算法转化为硬件语言,通过添加某些配置条件HLS工具可以把可并行化的C/C++的代码转化为vhdl或verilog,相比于纯人工使用vhdl实现图像算法,该工具综合出的代码的硬件资源占用可能较多。

2019-10-12 17:34:00 1961

1961

是来自新西兰的Mike Field,他是一个硬件Hacker,还建立了自己的网站( ),他详细总结了Vivado HLS的使用步骤,他认为这个很有趣,

2017-02-08 20:01:59 550

550

本实验练习使用的设计是实验1并对它进行优化。 步骤1:创建新项目 1.打开Vivado HLS 命令提示符 a.在windows系统中,采用Start>All Programs>Xilinx

2017-02-09 05:07:11 411

411

标准化的企业设计流程。本白皮书将探讨这种全新的 HLS/HLV 流程能够为 Qualcomm 这类公司带来诸多优势的一些原因,概括说明该流程及其优点,并介绍其在不久的

2017-09-11 11:37:38 9

9 1 Vivado HLS简介 2创建一个Vivado-HLS工程 2.1打开Vivado HLS GUI 2.2创建新工程 在 Welcome Page, 选择Create New Project

2017-12-04 10:07:17 0

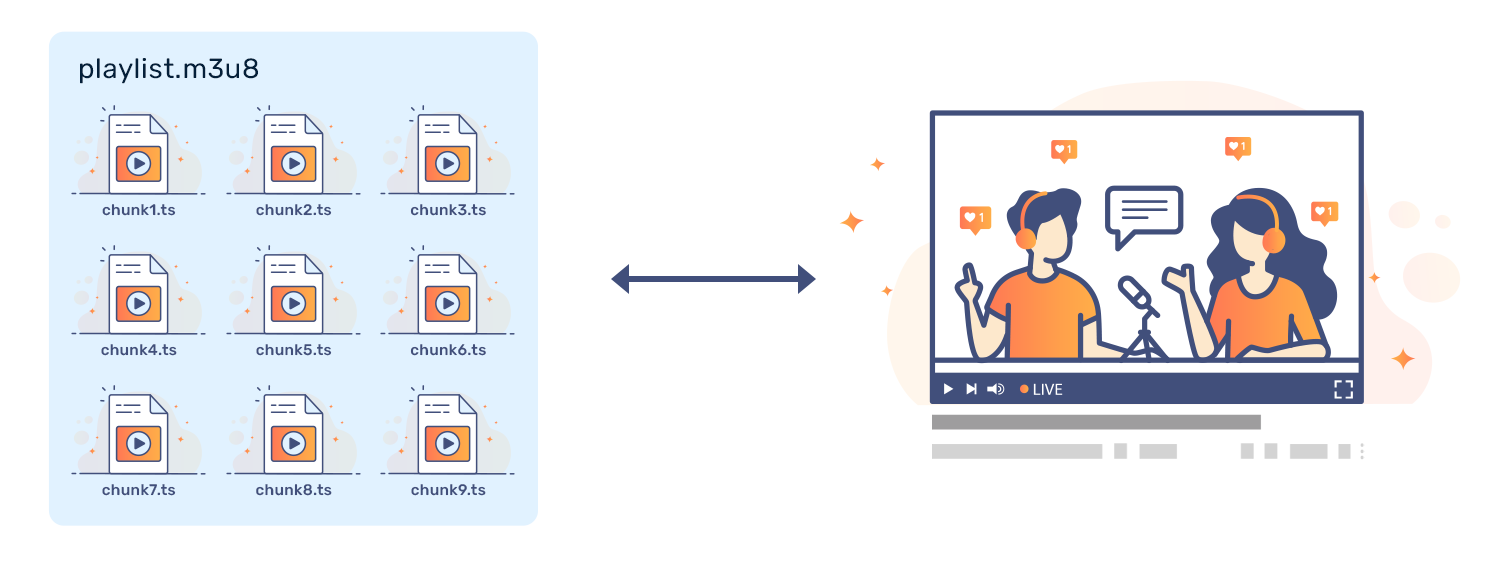

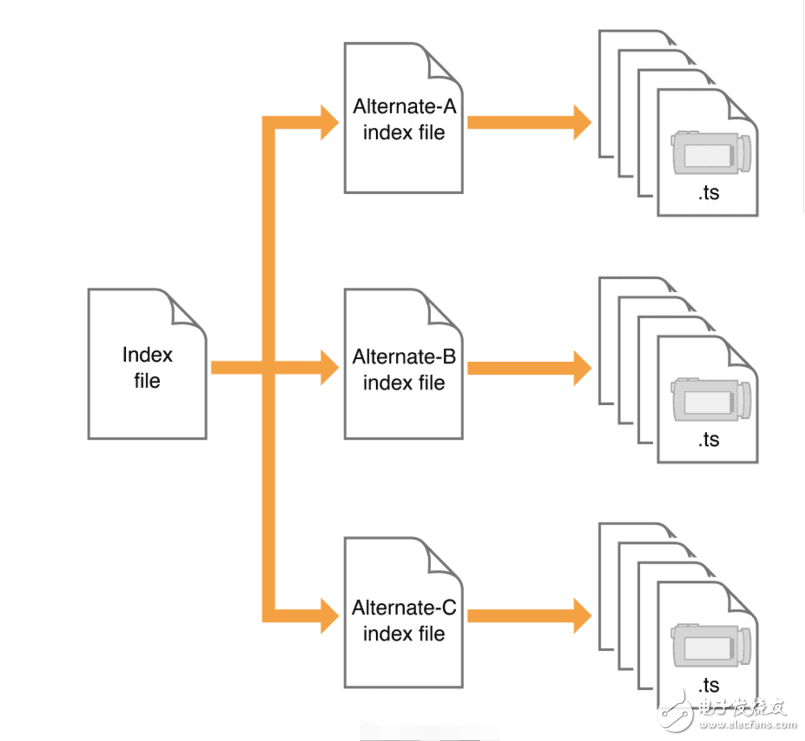

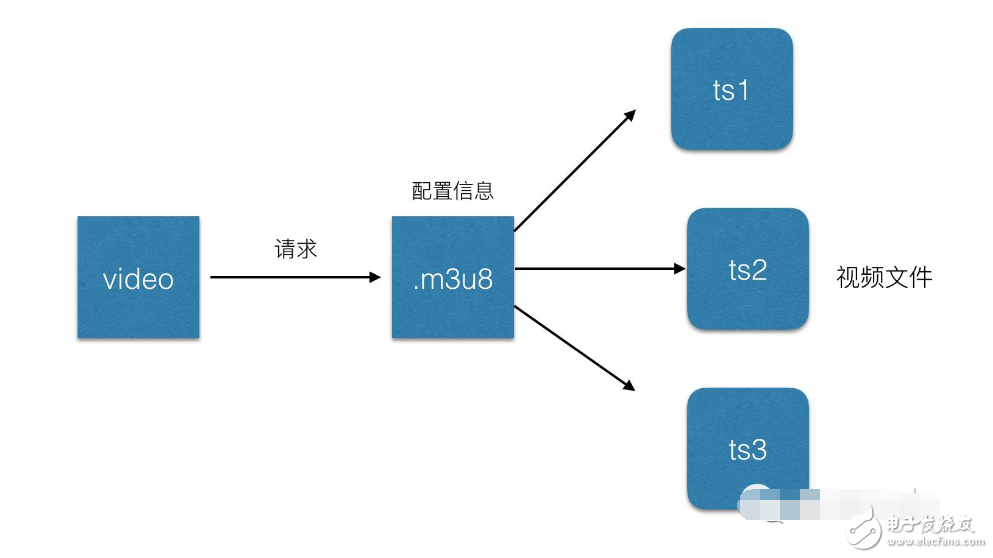

0 摘要:HTTP Live Streaming(缩写是HLS)是一个由苹果公司提出的基于HTTP的流媒体网络传输协议。今天主要以HLS协议为中心讲述它的一些原理。

2017-12-10 09:25:37 54719

54719 在实际工程中,如何利用好这一工具仍值得考究。本文将介绍使用Vivado HLS时的几个误区。

2018-01-10 14:33:02 19813

19813

本文内容介绍了基于用Vivado-HLS为软件提速,供参考

2018-03-26 16:09:10 7

7 作为集成电路设计领域现场可编程门阵列 (FPGA) 技术的创造者之一,赛灵思一直积极推广高层次综合 (HLS) 技术,通过这种能够解读所需行为的自动化设计流程打造出可实现此类行为的硬件。赛灵思刚刚推出了一本专著,清晰介绍了如何使用 HLS 技术来创建优化的硬件设计。

2018-11-10 11:01:05 2750

2750 了解如何使用GUI界面创建Vivado HLS项目,编译和执行C,C ++或SystemC算法,将C设计合成到RTL实现,查看报告并了解输出文件。

2018-11-20 06:09:00 3651

3651 了解如何使用Tcl命令语言以批处理模式运行Vivado HLS并提高工作效率。

该视频演示了如何从现有的Vivado HLS设计轻松创建新的Tcl批处理脚本。

2018-11-20 06:06:00 2888

2888 流媒体传输协议也是直播开发过程中的必备“项目”之一,直播中常用的流媒体协议主要有RTP、RTCP、RTSP、RTMP、HLS。其中的每一种传输协议都有各自的优缺点,适用于不同的直播环境和需求。云豹

2019-01-08 09:59:36 185

185 接着开始正文。据观察,HLS的发展呈现愈演愈烈的趋势,随着Xilinx Vivado HLS的推出,intel也快马加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入门门槛(不用编写

2019-07-31 09:45:17 6232

6232

Vivado HLS 2020.1将是Vivado HLS的最后一个版本,取而代之的是VitisHLS。那么两者之间有什么区别呢? Default User Control Settings

2020-11-05 17:43:16 37067

37067 本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

2022-07-25 17:45:48 3058

3058

<!--<img src="ams"-->HLS442_HLS440P_HPS100 (issued 2017-Apr)

2021-02-04 07:06:06 8

8 随着光纤入户的普及和电脑性能的不断提升,观众对直播的需求越来越高。常用的流媒体协议HLS虽已被广泛用于PC和手机终端的音视频服务,但在使用中仍然存在一些不足。我们邀请到哔哩哔哩弹幕视频网直播技术部

2021-07-09 08:52:08 2647

2647 HLS (HTTP Live Streaming)是Apple的动态码率自适应技术。主要用于PC和Apple终端的音视频服务。

相较于实时传输协议(RTP),HLS可以穿过任何允许HTTP数据通过的防火墙或者代理服务器,它也很容易使用内容分发网络来传输媒体流,因而得到了广泛的应用。

2022-04-08 11:24:09 2

2 gitee-monitor-rtsp-hls.zip

2022-05-07 11:06:57 4

4 Vitis HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis HLS 可在Vitis 应用加速开发流程中实现硬件

2022-05-25 09:43:36 1930

1930 HLS导出的.xo文件如何导入到Vitis里面?需要把.xo文件解压,然后把文件夹导入到Vitis Kernel/src文件夹下吗?

2022-08-03 11:20:26 2663

2663

Vitis HLS 工具能够将 C++ 和 OpenCL 功能部署到器件的逻辑结构和 RAM/DSP 块上。在 GitHub 上提供 Vitis HLS 前端为研究人员、开发人员和编译器爱好者开启了无限可能的新世界,使他们可以利用 Vitis HLS 技术并根据其应用的特定需求进行修改。

2022-08-03 09:53:58 713

713 对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2022-09-02 09:06:23 2858

2858 vivado本身集成了opencv库以及hls视频库了,opencv不能被综合导出为RTL电路,hls视频库的功能有所欠缺,因此引入xfopencv作为既可以被综合导出为RTL电路,也能够实现opencv丰富的功能。

2022-09-09 15:07:05 998

998 这里向大家介绍使用HLS封装的缩放IP来实现视频图像缩放功能。将HLS封装的缩放IP加入到OV5640图像传输系统,验证图像放大和缩小功能。

2022-10-11 14:21:50 1518

1518 1、HLS简介 HLS(High-Level Synthesis)高层综合,就是将 C/C++的功能用 RTL 来实现,将 FPGA 的组件在一个软件环境中来开发,这个模块的功能验证在软件环境

2022-12-02 12:30:02 2571

2571 对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2023-01-15 11:27:49 1317

1317 HLS (high-level synthesis)称为高级综合, 它的主要功能是用 C/C++为 FPGA开发 算法。这将提升FPGA 算法开发的生产力。 Xilinx 最新的HLS

2023-01-15 12:10:04 2968

2968 HLS,Http Live Streaming 是由Apple公司定义的用于实时流传输的协议,HLS基于HTTP协议实现,传输内容包括两部分,一是M3U8描述文件,二是TS媒体文件。

2023-04-06 09:29:50 428

428 AMD Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado Design Suite(用于综合、布置和布线)及 Vitis 统一软件平台(用于所有异构系统设计和应用)高度集成。

2023-04-23 10:41:01 652

652

在HLS中用C语言实现8192点FFT,经过测试,实验结果正确,但是时序约束不到100M的时钟,应该是设计上的延时之类的比较大,暂时放弃这个方案

2023-07-07 09:08:14 934

934

本文介绍VVAS框架所支持调用的H/W(HLS)内核

2023-07-14 15:55:24 406

406

Xilinx平台的Vivado HLS 和 Vitis HLS 使用的 export_ip 命令会无法导出 IP

2023-07-07 14:14:57 338

338

在HLS中用C语言实现8192点FFT,经过测试,实验结果正确,但是时序约束不到100M的时钟,应该是设计上的延时之类的比较大,暂时放弃这个方案,调用HLS中自带的FFT库(hls:fft

2023-07-11 10:05:35 580

580

本篇博客介绍 VVAS 框架所支持调用的 H/W(HLS) 内核。 H/W 内核指的是使用 HLS 工具生成的在 FPGA 部分执行的硬件功能模块。

2023-08-04 11:00:43 335

335

Vitis™ HLS 2023.1 支持新的 L1 库向导,本文将讲解如何下载 L1 库、查看所有可用功能以及如何在 Vitis HLS GUI 中使用库函数。

2023-08-16 10:26:16 546

546

电子发烧友网站提供《UltraFast Vivado HLS方法指南.pdf》资料免费下载

2023-09-13 11:23:19 0

0 电子发烧友网站提供《Vitis HLS移植指南.pdf》资料免费下载

2023-09-13 09:21:12 0

0 电子发烧友网站提供《将VIVADO HLS设计移植到CATAPULT HLS平台.pdf》资料免费下载

2023-09-13 09:12:46 2

2 -自适应流- HTTP) HLS(HTTP- Live-流) 两种协议的工作方式相似——数据被编码(分割)成块并发送到客户端进行查看。 一、HLS(HTTP直播) HLS(即HTTP Live

2023-10-09 17:16:54 485

485

电子发烧友App

电子发烧友App

评论