Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。

2022-09-14 09:09:56 1526

1526 双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 403

403

许可证管理器以获取有关确定系统许可的功能和设备的帮助。有关详细信息,请参阅Tcl控制台或消息。我尝试了重新安装和许可证,相同的结果....这是在webpack中禁用????约翰以上来自于谷歌翻译以下

2018-12-12 10:55:17

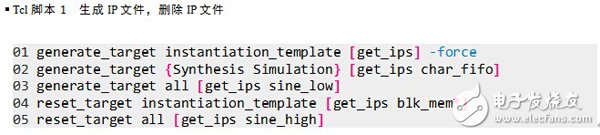

/ 134第5章 IP的管理 / 1355.1 定制IP / 1355.1.1 在Vivado工程中定制IP / 1355.1.2 在Manage IP中定制IP / 1395.2 IP的两种生成文件形式

2020-10-21 18:24:48

嗨,我正在使用Vivado 13.2在Zynq 7000上实现嵌入式设计。这是我的设计流程1)创建了一个新项目my_ip,其中包含1个ngc文件和2个从Xilinx Fifo Generator生成

2020-04-15 10:22:15

我在两台64位Windows机器上安装了2013.1,并且两者都崩溃了。 Vivado 2013.1窗口在崩溃之前会短暂出现。如果我从命令行运行,我会看到:****** Vivado v2013.1

2018-11-27 14:30:08

在模拟模型方面,Vivado提供的IP似乎有一些根本性的变化。在将工作设计从ISE 14.4转换为Vivado 2013.2之后,然后按照建议的方式升级大部分Xilinx IP,例如基本乘法器,除法

2019-02-26 10:42:23

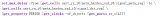

按钮是灰色的 情况) 在 Tcl console中 执行如下一条命令即可: upgrade_ip [get_ips] 以上两种方法均不能解决时,使用第三种方法。 3 工程另存为 至此IP解封。

2021-01-08 17:12:52

嗨,在我的Vivado实现tcl脚本中,以下行导致错误:设置SRC_PATH ./input.............#Input the netlistread_edif $ SRC_PATH

2018-10-18 14:26:39

你好我使用免费的ISE Webpack许可证安装了Vivado 2015.2。虽然我可以在许可证管理器中查看许可证,但Vivado软件似乎在模拟时不会检测到它。以下是显示的两个错误:1.错误

2020-04-07 13:29:03

是对新建IP core和编辑已封装的IP core;Open HardwareManager:打开硬件管理器,硬件管理器主要功能是连接硬件板卡,进行烧录和调试;Xilinx TCL Store

2019-07-18 15:40:33

是对新建IP core和编辑已封装的IP core;Open HardwareManager:打开硬件管理器,硬件管理器主要功能是连接硬件板卡,进行烧录和调试;Xilinx TCL Store

2023-09-06 17:55:44

嗨,我需要为Vivado 2016.3运行tcl来运行多个测试平台。如果我使用下一个:launch_simulationrun -allwait_on_run [current_run

2020-05-20 15:53:34

时,有这些信息就可以轻松实现。 在工程路径下,产生了一个新创建的at7.tcl文件,这时只需要保留.srcs文件夹和.tcl文件,其它文件或文件夹可以删除。此时,最后剩下的备份工程源码只有14.5MB

2020-08-17 08:41:25

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

请教一下,vivado怎么把带ip核的工程进行封装,保证代码不可见,可以通过端口调用。我尝试了以下方法,ippackage,如果要在另一个程序里调用,也要提供源代码;另一个方法是将网表文件edf文件与端口声明结合,这种方法只能实现不带ip核的封装

2017-07-14 09:18:30

本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

2021-03-02 07:22:13

嗨,在Vivado 2015.4和ISE 14.7中实现的相同设计之间的资源利用率是否会有任何差异?考虑到这样的事实,IP在Artix-7 FPGA中重新生成FIFO(版本9.3到13.1)时钟向导

2019-04-24 09:12:08

设计(加法器代表一下哈),当其他人想使用我这个adder IP时我不想交付给对方源代码,那么我应该如何做呢?交付DCP!何为DCP在Vivado的设计流程各个阶段里,采用统一的数据模型:DCP(design

2022-07-18 16:01:04

。Xilinx公司从ISE工具的后期开始,在工具中引入了对tcl语言的支持。在目前广泛使用的设计工具Vivado中,更是集成了tcl解释器,实现了对tcl很好的支持,同时也大大提高了编译及布局布线效率

2022-06-17 14:52:14

大家好,我是Vivado的新手。我想提取已实现设计的LUT名称,但我没有找到合适的tcl命令。以上来自于谷歌翻译以下为原文Hi every body,I am new with Vivado. I

2018-11-02 11:09:53

在工程项目中常常使用xilinx的IP时常会遇到一些加密的verilog和vhdl,打开后是以Xlx开始的十六进制文件,某些IP中的tcl和ttcl也是用这种方式保存的十六进制文件。vivado中使用这些文件都没有什么问题,就想知道这些文件是如何产生出来的?

2021-06-20 17:50:58

。使用Tcl能快速生成Vivado工程及编译工程,生成工程所需要的PL端bit文件。生成工程之后,根据自己的需要,可手动创建Block Design,或者在脚本添加IP、实现自动连接等功能。使用脚本可以快速

2020-06-07 13:59:52

我正在使用Vivado 2017.1并且我使用create_project.tcl获取以下错误以获取在Digilent网站中使用Artty Artix 7的ARTY基础系统设计入门。错误:[BD

2020-08-18 09:50:01

SPI4-P2接口形式可直接采用Altera公司的IP Core实现。Altera的主流FPGA均实现了硬件DPA功能,以Stratix II器件为例,在使能DPA的情况下使用SPI4-P2 IP Core可实现

2012-11-09 18:43:41

大家好!我正在研究ZC702板,在实施流程中我收到了一些关键警告,其中采用了模式以太网MAC IP的示例设计。所有这些都与.xdc文件有关。关于我的情况,我没有在互联网上找到任何解决方案。以下是批评

2019-09-20 08:33:44

问候,因此,我在创建IP外设并在VIVADO中使用ZYBO板单击“使用AXI4 BFM仿真接口验证外设IP”选项时收到此错误消息。我只想看到AXI接口的模拟我甚至没有它的逻辑,我创建了一个虚拟项目

2019-04-12 15:17:23

我对Vivado内部的IP检查点有疑问。当我在Vivado中启用IP内核的检查点时,我可以在Design Runs窗口中看到此IP的“synth”和“impl”。对于IP的“合成”,我可以理解这是

2019-03-08 13:30:52

请问有哪位大神,可以帮忙破解一个vivado的IP核。不胜感激,联系QQ397679468

2017-11-24 09:30:30

今天给大侠带来基于 FPGA Vivado 信号发生器设计,开发板实现使用的是Digilent basys 3。话不多说,上货。

需要源工程可以在以下资料获取里获取。

资料汇总|FPGA软件安装包

2023-08-15 19:57:56

:Vivado使用‘/’);

3) 在Tcl命令框中,输入命令:source ./ Oscilloscope.tcl。输入完毕按回车,运行Tcl;

4) 等待Tcl综合、实现、生成比特流文件;

5) 在

2023-08-17 19:31:54

and Package,点击‘Package IP’完成对74LS00 IP的封装。6.4完成后,系统提示封装成功。4.基于Tcl的封装流程:1)打开Vivado 2017.2,在底部Tcl

2017-12-20 10:23:11

:Vivado使用‘/’)3)在Tcl命令框中,输入命令:source ./ Oscilloscope.tcl。输入完毕按回车,运行Tcl4)等待Tcl综合、实现、生成比特流文件5)在Flow

2017-12-22 20:28:24

对你所有的人来说,我已经阅读了有关IP Block Designs的手册和培训材料,并成功地生成了AXI LITE BRAM IP设计,以及之前在USER社区中为您提供的一些帮助。我所坚持

2020-03-20 08:52:30

如何使用FPGA和IP Core实现定制缓冲管理?

2021-04-29 06:01:33

请问如何在CPLD管理下实现高效多串口中断源?

2021-04-13 06:10:26

大家好,有谁知道如何更改Vivado TCL控制台窗口中的字体/字体大小?我有一个2016.1的安装,我将字体从Courier更改为Consolas并稍微缩小尺寸以增加线路上的信息密度,但我最近安装

2019-04-22 15:11:29

嗨,大家好,我是vivado工具的新手,我需要为MIG或QSFP导出.xlsx报告文件我可以使用Tcl命令自动保存报告文件吗?

2020-05-12 08:31:50

小区或停车场的安防管理更加人性化、信息化、智能化、高效化。基于射频识别技术的特点,提出了射频识别技术在门禁系统中的应用模型,并重点介绍了软件和硬件两方面的实现。该系统具有识别准确率高、抗干扰能力强

2019-05-29 08:16:07

你好,有没有办法在Vivado 2016.1中关闭特定的DRC违规或警告?其次是AR#63997的方向,我试过:set_property严重性警告[get_drc_checks RTSTAT-2

2018-10-26 15:03:13

我的目标是实现一个给定的C算法是一个FPGA。所以,我最近得到了一个Zedboard,目标是实现该算法是PL部分(理想情况下PS中的顶级内容)。我在FPGA领域和编写VHDL / Verilog方面

2020-03-24 08:37:03

你好我正在尝试在vivado HLS中创建一个IP,然后在vivado中使用它每次我运行Export RTL我收到了这个警告警告:[Common 17-204]您的XILINX环境变量未定义。您将

2020-04-03 08:48:23

所有: 我正在尝试编写一个TCL脚本来重命名带有修订号的.bit文件。我需要一种方法让Vivado告诉我活动实现的名称。例如,如果我的活动实现是impl_5,我需要知道这一点,以便找到正确的.bit

2018-11-12 14:23:34

请问怎样利用热处理去实现高效能LED?

2021-04-23 06:28:02

Vivado GUI中打开一个项目,将.edf和.xdc文件作为源文件包含到项目中并运行一个只有下面这些行的tcl脚本,这样设计就是OOC,然后在GUI中运行实现,然后我就是面临很多错误

2018-10-23 10:30:35

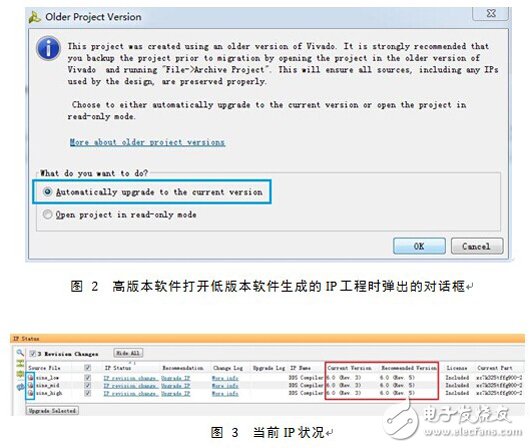

你好是否可以在不升级IP内核的情况下,通过较新版本的Vivado打开旧版Vivado?最好的祝福以上来自于谷歌翻译以下为原文HiIs it possible to open the older

2018-12-28 10:30:06

你好,有没有办法在新的vivado IDE中使用时钟向导(v3.5)实现“旧”生成的IP?特别是我遇到了问题,当我自动升级时,有一些输出缺失。例如,是否在较新版本的时钟向导(v5.1)中实现了一个输出,它具有与向导生成的CLK_VALID输出相同的功能(v3.5)?谢谢!

2020-07-29 10:52:20

://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw提取码:ld9c1概述Vivado标准IP核的移植可谓简单至极。简单3步,拷贝IP文件夹到当前工程目录下;在Vivado的IP Sources中

2019-09-04 10:06:45

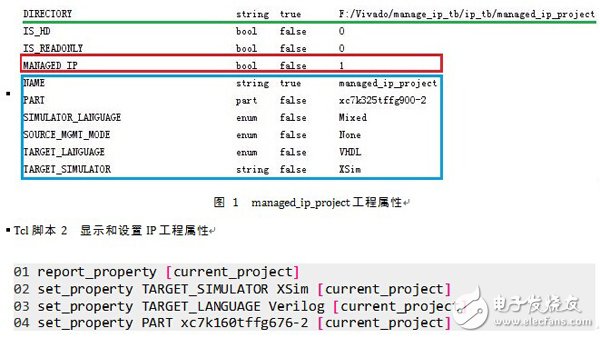

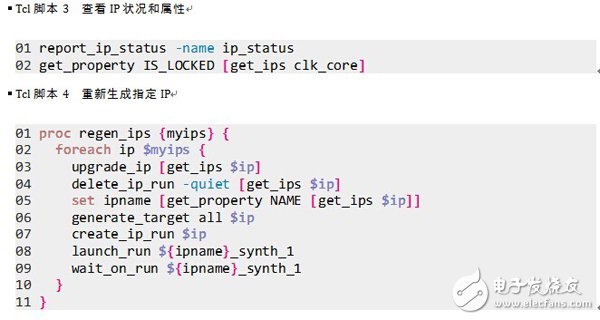

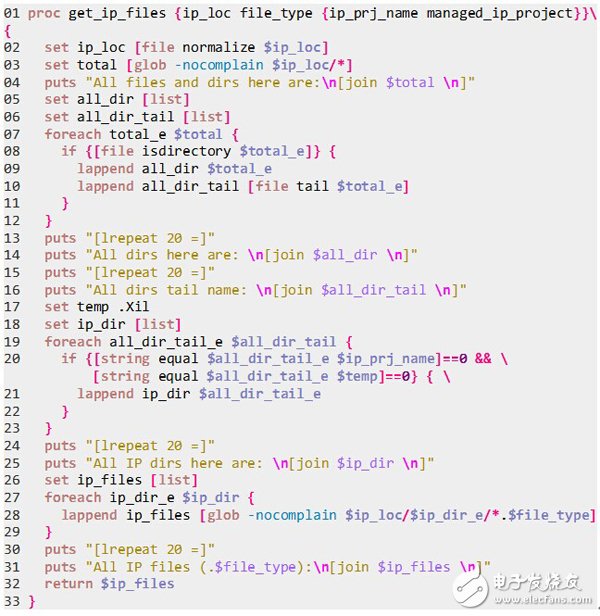

在 Vivado 中定位目标。其实 Tcl 在 Vivado 中还有很多延展应用, 接下来我们就来讨论如何利用 Tcl 语言的灵活性和可扩展性,在 Vivado 中 实现定制化的 FPGA 设计流程

2023-06-28 19:34:58

我已获得Xilinx HDMI IP内核的评估许可证,并已将其加载到许可证管理器中。我的IP经理似乎缺少实际的IP本身。我已经检查了计算机上的Xilinx文件夹,但找不到任何文件。我找到了名为

2019-01-02 15:02:41

Vivado中运行脚本,然后在Vivado中打开设计。通过运行“Tools => Report => Report IP Status ...”升级设计,然后运行write_bd_tcl以创建

2019-10-18 09:36:13

本文基于xilinx 的IP核设计,源于音频下采样这一需求。 创建vivado工程 1. 首先打开vivado,创建一个新的project(勾选create project subdirectory

2017-02-08 02:25:09 3716

3716

有关FPGA——VIVADO15.4开发中IP 的建立

2017-02-28 21:04:35 15

15 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言

2017-11-15 11:19:14 8390

8390 使用Xilinx Vivado HLS(Vivado 高层次综合)工具实现浮点复数QRD矩阵分解并提升开发效率。使用VivadoHLS可以快速、高效地基于FPGA实现各种矩阵分解算法,降低开发者

2017-11-17 17:47:43 3293

3293

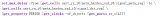

其实Tcl在Vivado中还有很多延展应用,接下来我们就来讨论如何利用Tcl语言的灵活性和可扩展性,在Vivado中实现定制化的FPGA设计流程。 基本的FPGA设计实现流程 FPGA的设计流程简单来讲,就是从源代码到比特流文件的实现过程。大体上跟IC设计流程类似,可以分为前端设计和后端设计。

2017-11-18 01:48:01 3295

3295

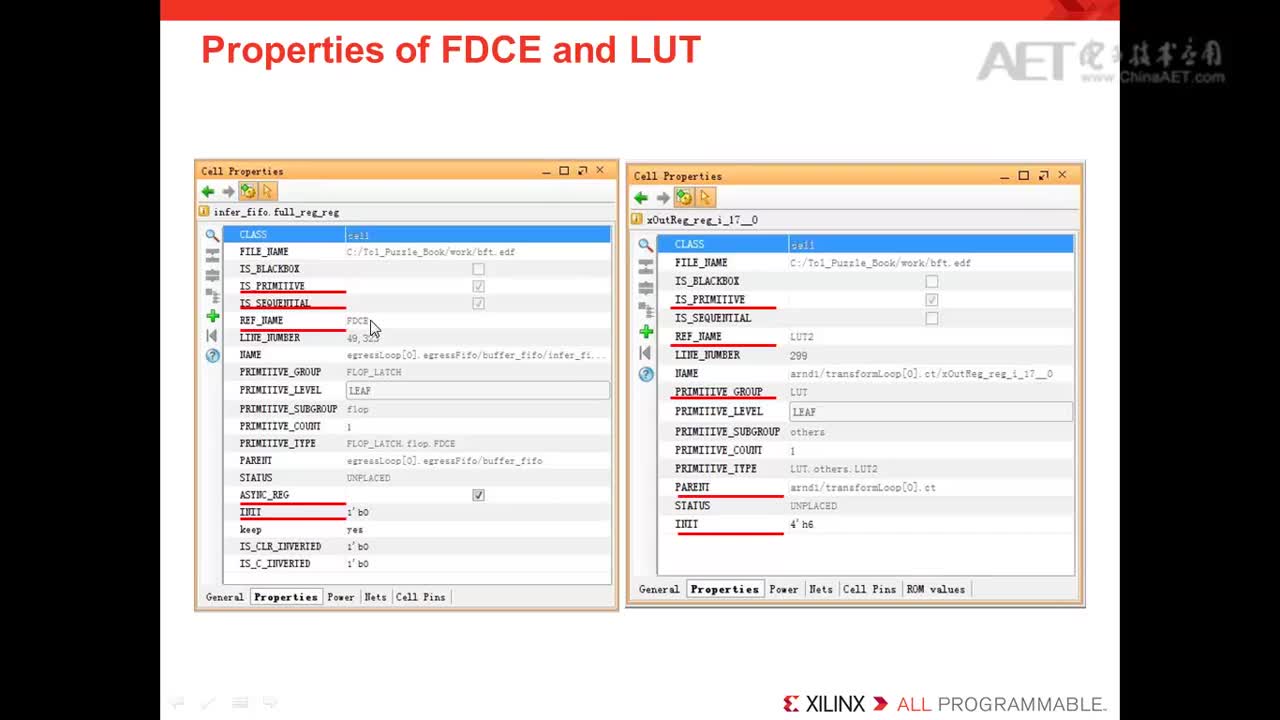

在ISE下,对综合后的网表进行编辑几乎是不可能的事情,但在Vivado下成为可能。Vivado对Tcl的支持,使得Tcl脚本在FPGA设计中有了用武之地。本文通过一个实例演示如何在Vivado下利用Tcl脚本对综合后的网表进行编辑。

2017-11-18 03:16:01 6899

6899

Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握

2017-11-18 03:52:01 4675

4675

关于Tcl在Vivado中的应用文章从Tcl的基本语法和在Vivado中的应用展开,介绍了如何扩展甚至是定制FPGA设计实现流程后,引出了一个更细节的应用场景:如何利用Tcl在已完成布局布线

2017-11-18 18:26:46 4987

4987

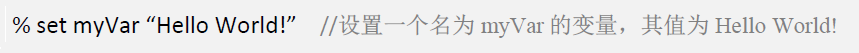

TCL脚本语言 Tcl(Tool Command Language)是一种很通用的脚本语言,它几乎在所有的平台上都可以解释运行,而且VIVADO也提供了TCL命令行。最近发现TCL脚本貌似比GUI下操作VIVADO效率高一些,方便一些。

2018-04-11 12:09:00 9154

9154 大家好,又到了每日学习的时间了,今天咱们来聊一聊vivado 调用IP核。 首先咱们来了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 36234

36234 工具命令语言(TCL)是集成在VIVADO环境中的脚本语言。TCL是半导体工业中用于应用程序编程接口的标准语言,并由SyoSype®设计约束(SDC)使用。

2018-08-09 08:00:00 38

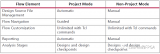

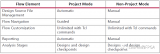

38 观看视频,学习如何将 Vivado IP 和第三方综合工具配合使用。 此视频将通过一个设计实例引导您完成创建自定义 IP 的步骤;用第三方综合工具IP黑盒子来审查所需 IP 输出;整合 Vivado IP 网表和第三方综合工具网表的两个方法,即 “网表项目模式” 和 “非项目 Tcl 脚本模式”。

2018-11-21 06:34:00 4811

4811 此视频概述了Vivado Design Suite中的IP加密。

它涵盖了IP加密工具流程,如何准备加密IP以及如何在Vivado中运行加密工具。

2018-11-20 06:34:00 5948

5948 了解如何使用Tcl命令语言以批处理模式运行Vivado HLS并提高工作效率。

该视频演示了如何从现有的Vivado HLS设计轻松创建新的Tcl批处理脚本。

2018-11-20 06:06:00 2887

2887 了解Vivado中的Logic Debug功能,如何将逻辑调试IP添加到设计中,以及如何使用Vivado Logic Analyzer与逻辑调试IP进行交互。

2018-11-30 06:22:00 3107

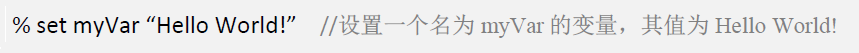

3107 实际上Tcl的功能可以很强大,用其编写的程序也可以很复杂,但要在Vivado或大部分其它EDA工具中使用,则只需掌握其中最基本的几个部分

2019-07-24 16:52:00 3179

3179

Tcl介绍 Vivado是Xilinx最新的FPGA设计工具,支持7系列以后的FPGA及Zynq 7000的开发。与之前的ISE设计套件相比,Vivado可以说是全新设计的。无论从界面、设置、算法

2020-11-17 17:32:26 2112

2112 Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP

2020-12-29 15:59:39 9496

9496 Vivado有两种工作模式:project模式和non-project模式。这两种模式都可以借助VivadoIDE或Tcl命令来运行。相比之下,VivadoIDE给project模式提供了更多的好处,而Tcl命令使得non-project模式运行起来更简单。

2020-10-21 10:58:07 3294

3294

前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案,发表之后经过一年多操作上也有

2021-03-22 10:31:16 3409

3409 Vivado提供了三种封装IP的方式:(1)将当前工程封装为IP;(2)将当前工程中的BD(IPI 设计)封装为IP;(3)将指定的文件目录封装为IP。 IP Packager支持的输入文件HDL

2021-08-10 18:09:29 5567

5567

XDC约束可以用一个或多个XDC文件,也可以用Tcl脚本实现;XDC文件或Tcl脚本都要加入到工程的某个约束集(set)中;虽然一个约束集可以同时添加两种类型约束,但是Tcl脚本不受Vivado工具管理,因此无法修改其中的约束;

2022-06-30 11:27:23 2848

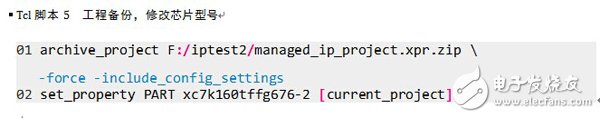

2848 一个完整的vivado工程往往需要占用较多的磁盘资源,少说几百M,多的甚至可能达到上G,为节省硬盘资源,可以使用Tcl命令对vivado工程进行备份,然后删除不必要的工程文件,需要时再恢复即可。

2022-08-02 15:01:06 3696

3696 前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案,发表之后经过一年多操作上也有些许改进,所以写这篇文章补充下。

2022-08-29 14:41:55 1549

1549 Vivado是Xilinx推出的可编程逻辑设备(FPGA)软件开发工具套件,提供了许多TCL命令来简化流程和自动化开发。本文将介绍在Vivado中常用的TCL命令,并对其进行详细说明,并提供相应的操作示例。

2023-04-13 10:20:23 1551

1551 Xilinx的新一代设计套件Vivado相比上一代产品 ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为

2023-04-15 09:43:09 958

958 今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

2023-05-05 09:44:46 674

674

关于 Tcl 在 Vivado中的应用文章从 Tcl 的基本语法和在 Vivado 中的 应用展开,继上篇《用 Tcl 定制 Vivado 设计实现流程》介绍了如何扩展甚 至是定制 FPGA

2023-05-05 15:34:52 1612

1612

在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 1240

1240

在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。

2023-06-20 14:23:57 622

622

Vivado IP核提供了强大的FIFO生成器,可以通过图形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1628

1628

FPGA开发中使用频率非常高的两个IP就是FIFO和BRAM,上一篇文章中已经详细介绍了Vivado FIFO IP,今天我们来聊一聊BRAM IP。

2023-08-29 16:41:49 2605

2605

在给Vivado中的一些IP核进行配置的时候,发现有Shared Logic这一项,这里以Tri Mode Ethernet MAC IP核为例,如图1所示。

2023-09-06 17:05:12 529

529

电子发烧友网站提供《Vivado设计套件Tcl命令参考指南.pdf》资料免费下载

2023-09-14 10:23:05 1

1 电子发烧友网站提供《Vivado设计套件用户指南:使用Tcl脚本.pdf》资料免费下载

2023-09-14 14:59:39 0

0 电子发烧友网站提供《Vivado Design Suite用户指南:使用Tcl脚本.pdf》资料免费下载

2023-09-13 15:26:43 0

0 Vivado是Xilinx公司2012年推出的新一代集成开发环境,它强调系统级的设计思想及以IP为核心的设计理念,突出IP核在数字系统设计中的作用。

2023-09-17 15:37:31 1060

1060

文章是基于Vivado的 2017.1的版本,其他版本都大同小异。 首先在Vivado界面的右侧选择IP Catalog 选项。

2023-12-05 15:05:02 317

317

电子发烧友App

电子发烧友App

评论