声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1797浏览量

133132 -

IP

+关注

关注

5文章

1849浏览量

154889 -

Vivado

+关注

关注

19文章

846浏览量

70454

发布评论请先 登录

相关推荐

热点推荐

利用vivado实现对e200_opensource 蜂鸟E203一代的仿真

最后,点击run simulation进行 行为级仿真

得到最后的仿真结果如图所示

本文参考论坛内另外两篇文章:

[1] 在Windows环境下用Vivado调试E203作者:leon

[2

发表于 10-31 06:14

vivado时序分析相关经验

-logic_level_distribution -logic_level_dist_paths 5000 -name design_analysis_prePlace”此tcl命令可以对设计中的逻辑级数分布

发表于 10-30 06:58

vcs和vivado联合仿真

我们在做参赛课题的过程中发现,上FPGA开发板跑系统时,有时需要添加vivado的ip核。但是vivado仿真比较慢,vcs也不能直接对添加了vivado

发表于 10-24 07:28

Vivado浮点数IP核的握手信号

Vivado浮点数IP核的握手信号

我们的设计方案中,FPU计算单元将收到的三条数据和使能信号同步发给20多个模块,同时只有一个模块被时钟使能,进行计算,但结果都会保留,发给数选。计算单元还需接受

发表于 10-24 07:01

Vivado浮点数IP核的一些设置注意点

Vivado浮点数IP核的一些设置注意点

我们在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定义其计算种类及多模式选择。有时多种计算可以用同一

发表于 10-24 06:25

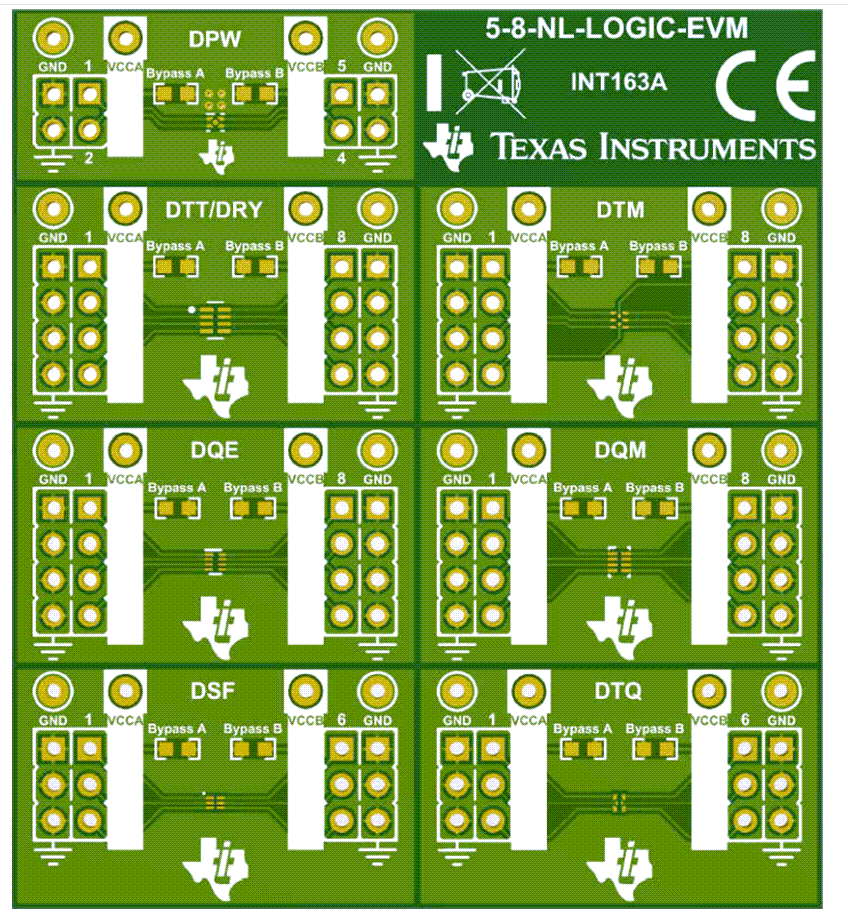

Texas Instruments 5-8-NL-LOGIC-EVM逻辑转换评估模块技术解析

Texas Instruments 5-8-NL-LOGIC-EVM逻辑和转换评估模块 (EVM) 设计用于支持任何逻辑或转换器件。它支持DTT (X1QFN-8)、DRY (USON-6)、DPW

AMD Vivado ChipScope助力硬件调试

许多硬件问题只有在整个集成系统实时运行的过程中才会显现出来。AMD Vivado ChipScope 提供了一套完整的调试流程,可在系统运行期间最大限度提升对可编程逻辑的观测能力,助力设计调试

FPGA调试方式之VIO/ILA的使用

在Vivado中,VIO(Virtual Input/Output)是一种用于调试和测试FPGA设计的IP核,它允许设计者通过JTAG接口实时读取和写入FPGA内部的寄存器,从而检查设计的运行状态并修改其行为。VIO

SDRAM控制器设计之signaltap调试

Signal Tap Logic Analyzer是Intel Quartus Prime设计软件中自带的新一代系统级调试工具,它可以在FPGA设计中采集和显示实时的信号行为。当设计在FPGA上全速运行时,无需额外的I/O引脚即

Vivado FIR IP核实现

Xilinx的FIR IP核属于收费IP,但是不需要像 Quartus那样通过修改license文件来破解。如果是个人学习,现在网络上流传的license破解文件在破解Vivado的同时也破解

Vivado Design Suite用户指南:逻辑仿真

电子发烧友网站提供《Vivado Design Suite用户指南:逻辑仿真.pdf》资料免费下载

发表于 01-15 15:25

•0次下载

PADS逻辑教程

易用性和效率。PADS Logic旨在满足高级用户的需求,同时牢记初学者。PADS Logics界面和交互与其他Windows™应用程序相似。您可以使用键盘、菜单、工具栏和快捷菜单与PADS Logic

发表于 12-16 14:33

•1次下载

如何使用Vivado Logic Analyzer与逻辑调试IP进行交互

如何使用Vivado Logic Analyzer与逻辑调试IP进行交互

评论