分频器是数字系统设计中的基本电路,根据不同设计的需要,我们会遇到偶数分频、奇数分频、半整数分频等,有时要求等占空比,有时要求非等占空比。在同一个设计中有

2010-09-03 17:04:20 2442

2442

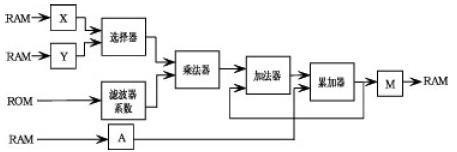

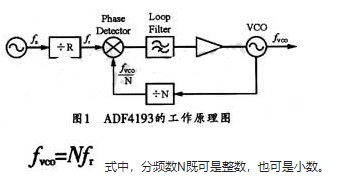

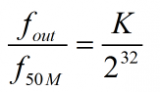

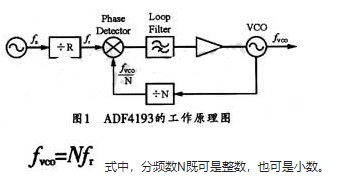

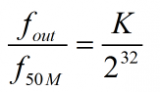

在大部分的教科书中,都会提到如何分频,包括奇数分频,偶数分频,小数分频等。 1、DDS相位累加器 (1)DDS合成流程 首先讲述DSS(直接频率合成法)的原理。 DDS是重要的频率合成方法,在波形

2020-11-29 10:19:00 4144

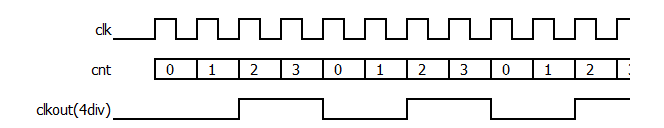

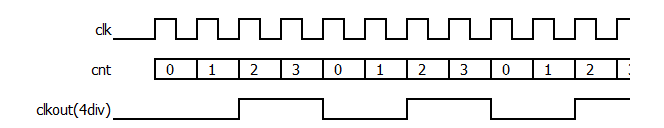

4144 前言: 偶数分频容易得到:N倍偶数分频,可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去

2020-12-28 15:49:20 2620

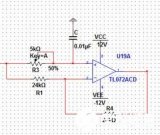

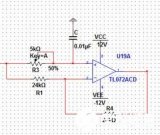

2620 。计数器进行奇数次分频,触发器进行二分频。电路占空比为50% 1.3 滤波电路 由运放TL072和无源元件RC组成二阶有源带通滤波电路。该电路既可以滤除直流和高次谐波分量,又可以放大电压 1.4 移相电路 如图-1所示,RC等幅移相电路。电路可调相范围为0~90,幅度恒定。 图-1 1.5 加法

2020-11-18 10:41:01 9065

9065

在进行数字电路设计的过程中,分频器是设计中使用频率较高的一种基本设计之一

2023-11-07 17:29:11 745

745

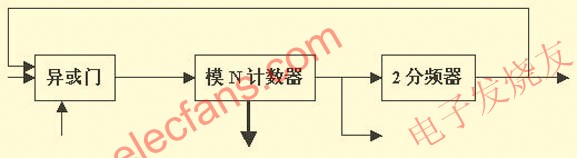

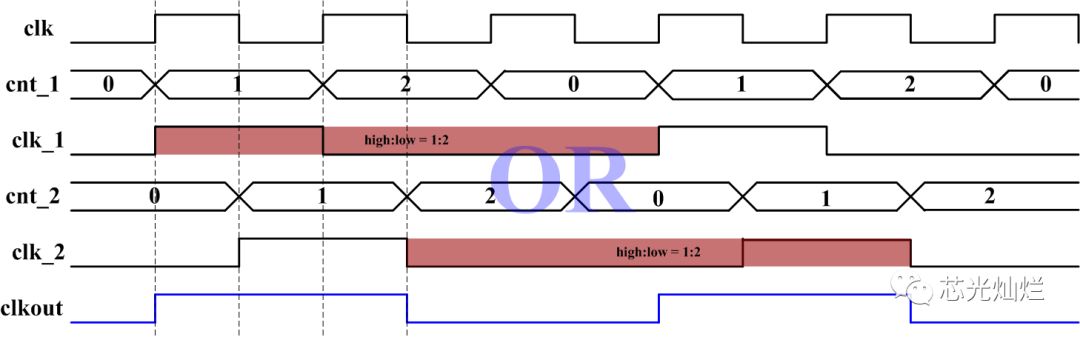

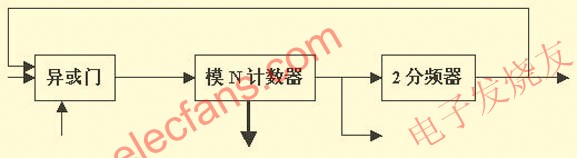

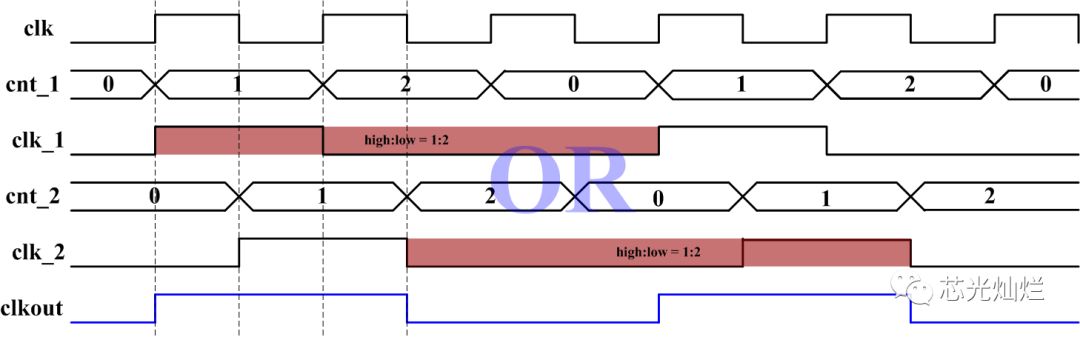

的OCC。像是拔牙操作一类的分频我们今天不讨论。今天讨论的任意分频器在许多的数字IC设计与FPGA面试笔试题中都有考察,所以在实(tou)现(xue)了以后做本次学习记录,供大家参考。1. 先入为主 我们来宏观的看本次分频器的内容,会比较容易理解。关键功能点的电路如图1所示:...

2022-02-09 07:34:15

计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去。这种方法可以实现任意的偶数分频。module div_6(inputi_clk,inputi_rst_n,output reg o_clk); // log2(6) = 2.5850

2013-05-01 08:44:05

D触发器组成的_2N_1_2分频电路,几种奇数分频电路设计

2012-05-23 19:34:41

`基于FPGA+的任意小数分频器的设计基于FPGA的多种分频设计与实现基于FPGA的小数分频器的实用Verilog 实现基于FPGA 的通用分频用Verilog+HDL实现基于FPGA的通用分频

2012-02-03 15:02:31

等等奇数类分频,那应该怎么办呢?在这里,梦翼师兄为大家介绍一种可以实现任意整数分频的方法。实现原理这种方法同样也是利用了计数器来实现,当然我们是使用状态机来实现的。我们首先定义分频时钟高电平的个数

2019-12-11 10:15:33

半个CLK时钟周期。通过这两个时钟信号进行逻辑运算我们可以巧妙地得到50%占空比的时钟。

总结如下:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟

2023-12-24 18:10:59

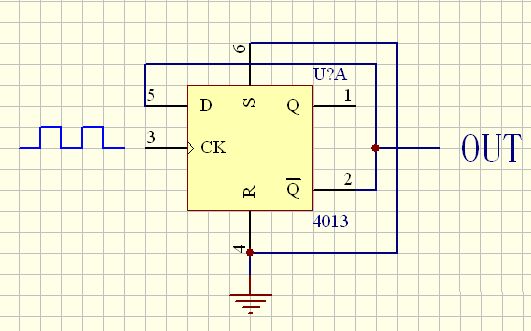

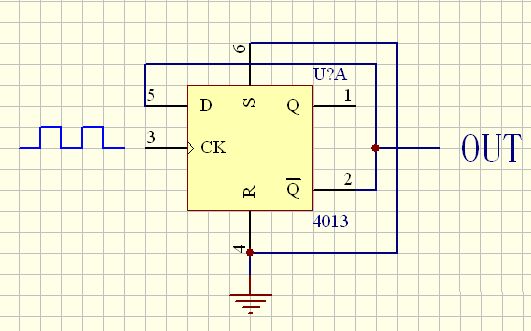

对于分频相信大家都不陌生了但是对于分频的原理可能大家还不是非常清楚我在这里就谈谈自己的感受吧常见的我们使用的就是74hc74,也就是d触发器来做分频。特别是对于偶数分频一般容易使用。但是对于奇数相对来说就比较复杂一些了下面附上我常用的的2,4分频的电路

2009-08-04 12:10:10

观察输出波形并加以记录。电路有用到:74ls90 pdf .三分频电路d触发器构成2分频电路用多级2进计数器的分频电路脉冲分频电路双稳态分频电路图任意分频电路图1/60分频电路用VHDL语言实现3分频电路SN7474N构成简单的分频电路[此贴子已经被作者于2009-6-22 8:04:20编辑过]

2009-06-22 08:02:10

通用的可以输出输入信号的2分频信号,4分频信号,8分频信号,现在我想产生3分频信号,5分频信号,如何实现?求指教?给个思路就行!~~

2013-11-06 23:23:05

从零开始计数。以此循环下去。这种方法可以实现任意的偶数分频。第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:首先,完全可以通过计数器来实现,如进行三分频,通过待分频时钟

2019-06-14 06:30:00

利用变体队列实现任意复杂数据集合传递(很方便),大家可以看看。原创是来自@zhihuizhou 【labview我来告诉你】实现任何LabVIEW数据类型集合的简洁方式。我在此基础上加了一些,方便大家理解这样的好处。

2020-02-11 15:39:21

如题,设置任意参数可变的整数分频,分频系数由DSP发送给CPLD,在调试的过程中发现由2分频调到3分频的时候,占空比不为50%,但是从新启动后的3分频的占空比为50%,猜测应该是计数器cnt1

2017-03-13 16:57:17

【摘要】:介绍了基于FPGA的任意分频系数的分频器的设计,该分频器能实现分频系数和占空比均可以调节的3类分频:整数分频、小数分频和分数分频。所有分频均通过VHDL语言进行了编译并且给出了仿真图。本

2010-04-26 16:09:01

双模前置小数分频原理是什么?如何对小数分频器进行仿真测试?

2021-04-29 07:29:41

液晶屏汉字显示的原理是什么?如何实现任意汉字的显示?有哪些步骤?

2022-01-19 07:17:06

如何实现任意波形频域变换器设计?

2022-02-15 06:30:36

如何利用DDS去实现任意信号波形的产生?怎样设计信号源硬件电路?

2021-04-07 06:16:32

从零开始计数。以此循环下去。这种方法可以实现任意的偶数分频。第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:首先,完全可以通过计数器来实现,如进行三分频,通过待分频时钟

2019-07-09 09:11:47

请问如何采用CPLD和单片机实现任意波形发生器的设计?

2021-04-22 06:29:10

要设计小数分频PLL,基本架构已经确定:使用基于MASH111的DSM,双模预分频器+PScounter实现。现在遇到的问题是,不知道怎么把小数分频控制字经过DSM后的输出与整数分频控制字结合起来去控制(双模分频器+PScounter)可编程分频器此前没做过小数分频PLL,求助大佬们点拨一二

2021-06-24 07:20:38

学校要求的课程设计基于VHDL实现任意小数分频

2014-04-24 09:09:31

各种数字电路。包括时钟信号产生电路、波形整形及变换电路、定时与延时电路、计数分频及倍频电路、键盘编码及信号输入电路、译码显示电路、通信及数据传输电路、数据运算电路、微处理器电路、存储器电路···

2011-08-22 14:25:01

用verilog_hdl实现任意八位序列检测

2012-08-18 10:46:48

计数器一个复位信号,以使下一个时钟从零开始计数。以此循环,就可以实现任意的偶数分频。 1.2 奇数倍分频 奇数倍分频有两种实现方法,其中之一完全可以通过计数器来实现,如进行三分频,就可通过待分频

2018-10-12 16:52:21

ad9518-4,改芯片用过好多次,这次应用不同需要输出800MHz。发现如下问题:将VCO的分频设置0x1e0到偶数分频(2、4)都不能锁定。其他设置不变,设置成奇数分频就没有锁不定的问题;观察

2018-08-19 07:53:25

. 数字电平可能容易,但是如果想实现模拟电平,可以吗?

下次使用的时候,希望能够通过编程修改这种对应关系,同时想问问,如果FPGA可以实现,那么还有别的元器件可以实现吗?

请问CPLD或者FPGA能够实现任意的IO口对联吗?数字方式的可以话,那么模拟方式的也可以吗?

2023-04-23 14:19:12

目录1、中断向量表配置2、中断引脚配置3、中断处理函数EXTI0 至 EXTI15 用于 GPIO,通过编程控制可以实现任意一个 GPIO作为 EXTI的输入源。由表 18-1 可知, EXTI0

2021-08-13 07:26:52

本帖最后由 haozix521 于 2013-10-4 20:42 编辑

想做一个占空比50%的奇数分频器,但是不是很了解这其中的意思。网上的资料都是这样讲的“对于实现占空比为50%的N倍奇数分频

2013-10-04 20:35:11

任意分频系数小数分频器相关文档及源代码

2009-08-03 09:49:30 75

75 在复杂数字逻辑电路设计中,经常会用到多个不同的时钟信号。介绍一种通用的分频器,可实现2~256 之间的任意奇数、偶数、半整数分频。首先简要介绍了FPGA 器件的特点和应用范

2009-11-01 14:39:19 78

78 该文提出采用信号流图实现任意阶FTFN-RC 通用滤波器的方法。通过对网络函数的直接分析,导出了任意阶传输函数的FTFN-RC 实现电路。该滤波电路仅包含n 个有源器件,n 个接地电容和

2010-02-09 15:10:30 27

27 基于FPGA 的等占空比任意整数分频器的设计

给出了一种基于FPGA 的等占空比任意整数分频电路的设计方法。首先简要介绍了FPGA 器件的特点和应用范围, 接着讨论了一

2010-02-22 14:22:32 39

39 提出了一种通用的可编程双模分频器,电路主要由3 部分组成: 9/8 预分频器,8 位可编程计数器和ΣΔ调制器构成。通过打开或者关断ΣΔ 调制器的输出来实现分数和整数分频两种工作

2010-04-23 08:39:35 30

30 议程PLL介绍及小数分频锁相环的优点小数分频锁相环的错误使用小数分频锁相环详解参考杂散及如何减少杂散总结

2010-05-28 14:58:36 0

0 用VHDL语言实现3分频电路

标签/分类:

众所周知,分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相

2007-08-21 15:28:16 5527

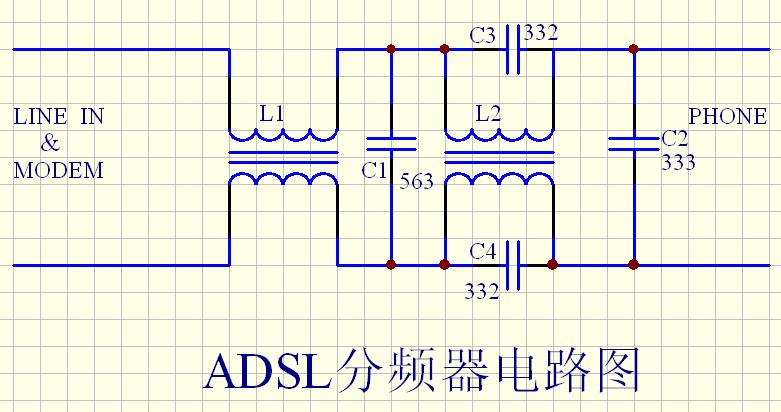

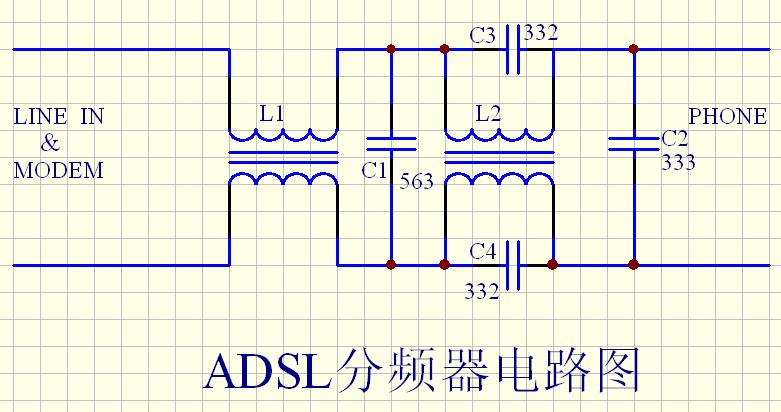

5527 ADSL分频器电路图从电路上可以看出,该分频器的作用只是针对电话座机,而非针对MODEM。在一般

2007-09-30 19:53:24 2148

2148

IIR数字滤波器设计-在FPGA上实现任意阶IIR数字滤波器

摘 要:本文介绍了一种采用级联结构在FPGA上实现任意阶IIR数字滤波器的方法。此

2008-01-16 09:45:39 2276

2276

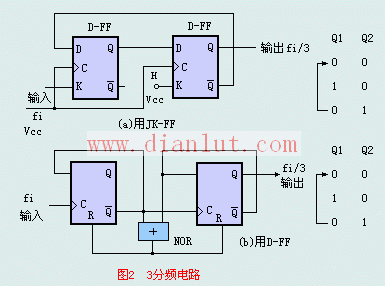

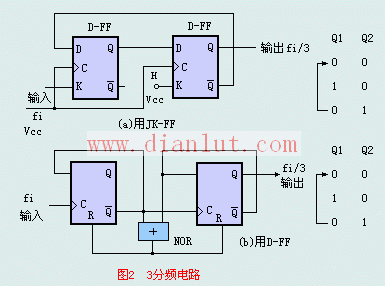

下图是 用于N=二-四分频比的电路,常用双D-FF或双JK-FF器件来构成,分频比n>4的电路,则常采用计数器(如可预置计数器)来实现更为方便,一般无需再用单个FF来组合。

2008-06-29 23:31:06 22462

22462

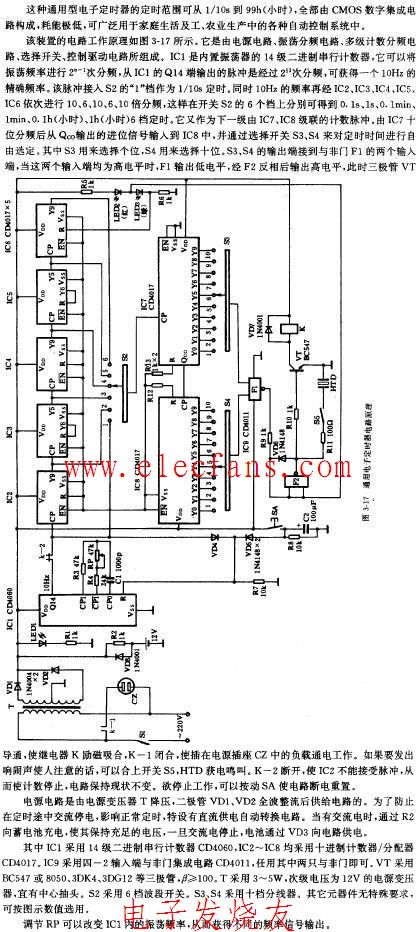

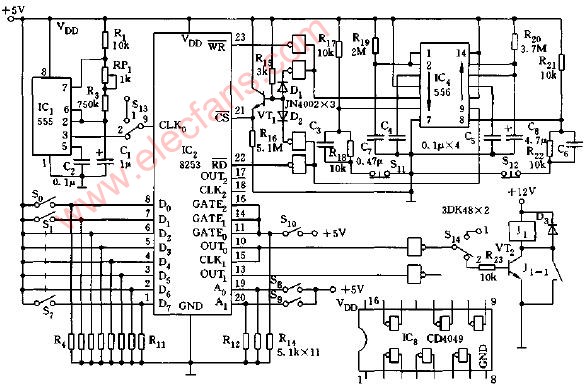

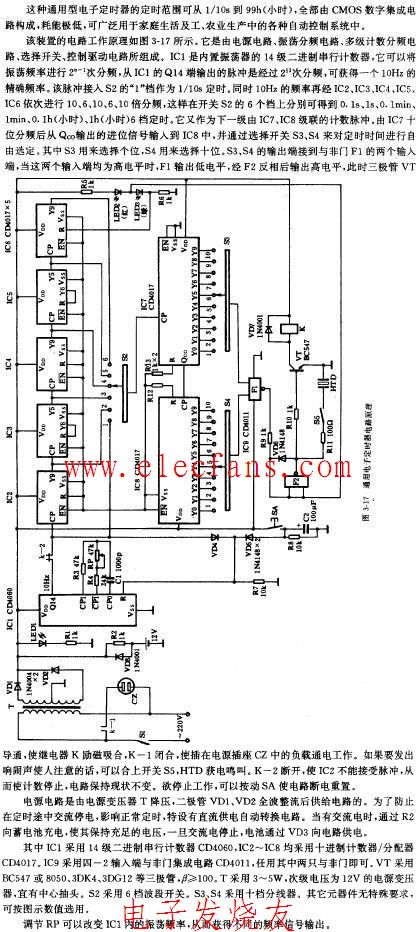

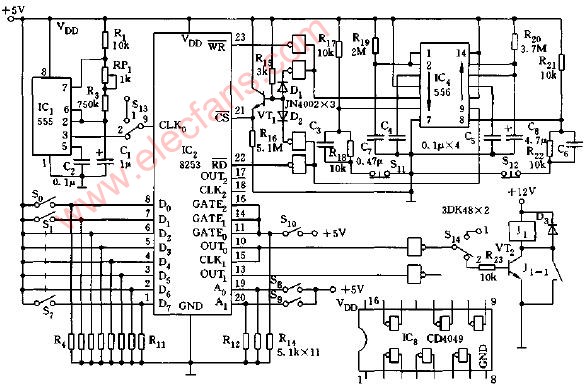

通用电子定时器电路图

2008-08-11 08:26:07 5094

5094

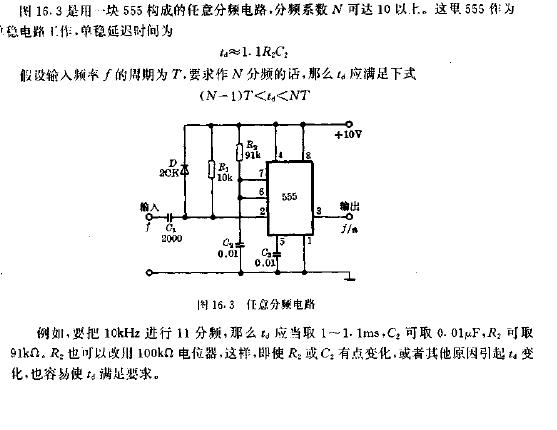

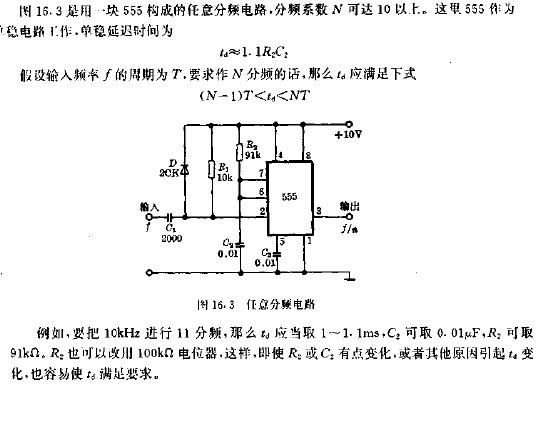

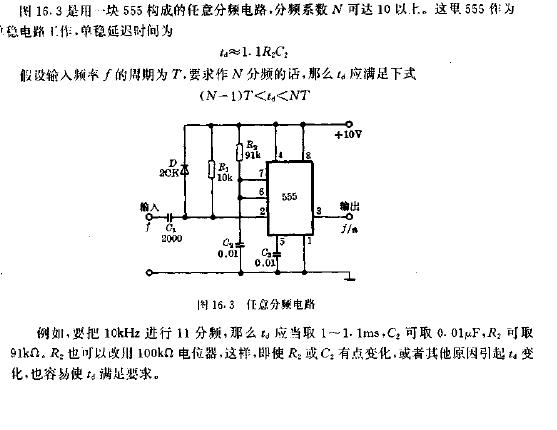

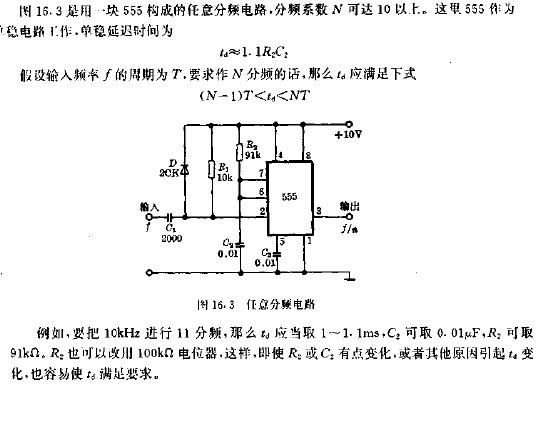

任意分频电路图

2009-04-09 12:02:35 2758

2758

可编程定时、分频两用电路图

2009-05-30 15:57:39 485

485

D触发器实现二分频电路(D触发器构成的2分频电路)&

2009-06-12 13:58:56 75438

75438

分频电路

在一个扬声器系统里,人们把箱体、分频电路、扬声器单元称为扬声器系统的三大件,而分频电路对扬声器系统能否高质量地还原电声信号起着

2009-06-12 14:35:10 6578

6578

摘 要: 本文通过在QuartursⅡ开发平台下,一种能够实现等占空比、非等占空比整数分频及半整数分频的通用分频器的FPGA设计与实现,介绍了利用VHDL硬件描

2009-06-20 12:43:07 562

562

图2是3分频电路,用JK-FF实现3分频很方便,不需要附加任何逻辑电路就能实现同步计数分频。但用D-FF实现3分频时,必须附加译码反馈电路,如图2所示的译码复位电路,强制计数状态

2009-06-22 07:41:00 12116

12116

什么是分频电路

2009-06-22 07:51:22 5386

5386

10分频电路

任意分频电路图

2009-06-22 08:04:33 15654

15654

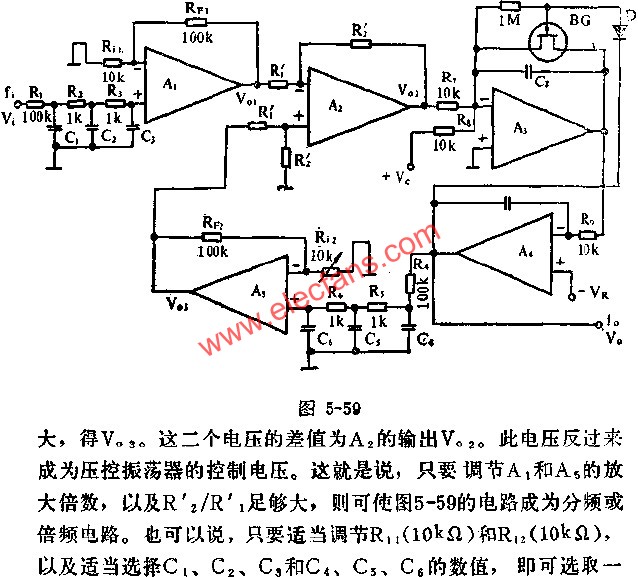

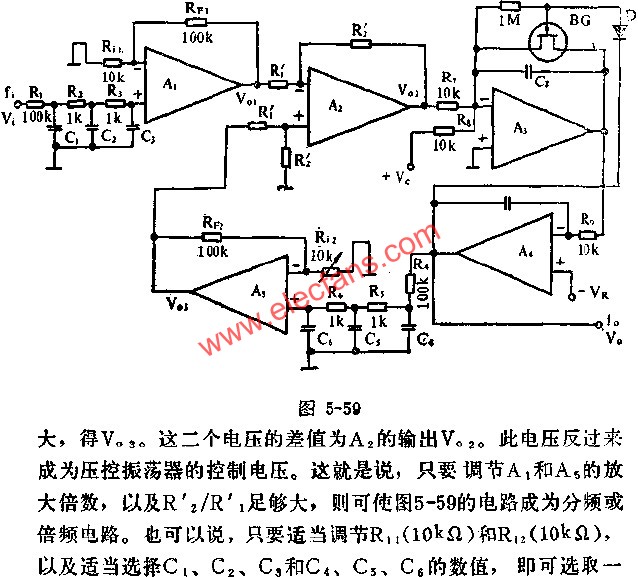

图中所示是用运算放大器通用I型组成的分频和倍频电路.能在10HZ~10KHZ频段内工作.图示线路是分频与倍频的基本

2010-10-08 12:12:21 10528

10528

给出了一种小数分频技术的实现方法, 并在实验的基础上进一步证实了小数分频的可行性该法通过微机控制,

2011-02-22 14:58:54 45

45 在电子技术中,N/2(N为奇数)分频电路有着重要的应用.对一个特定输入频率,要经N/2分频后才能得到所需要的输出,这就要求电路具有N/2的非整数倍的分频功能。CD4013是双D触发器,在以CIM013为主组成的若干个二分频电路的基础上,加上异或门等反馈控{6I,即

2011-03-11 17:05:45 338

338 提出了一种基于FPGA的小数分频实现方法,介绍了现有分频方法的局限性,提出一种新的基于两级计数器的分频实现方法,给出了该设计方法的设计原理以及实现框图

2011-11-09 09:36:22 121

121 给出了一种基于FPGA的分频电路的设计方法.根据FPGA器件的特点和应用范围,提出了基于Verilog的分频方法.该方法时于在FPGA硬件平台上设计常用的任意偶数分频、奇数分频、半整数分频

2011-11-09 09:49:33 355

355 介绍了一种基于FPGA的双模前置小数分频器的分频原理及电路设计,并用VHDL编程实现分频器的仿真.

2011-11-29 16:43:06 48

48 Delphi教程之在DBGrid中实现任意方向查找,学习Delphi的必备资料。

2016-03-31 11:29:41 3

3 用 Verilog实现基于FPGA 的通用分频器的设计时钟分频包括奇数和偶数分频

2016-07-14 11:32:47 45

45 原文出自:分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。在许多电子设备中如电子钟、频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种频率成分,分频器是一种主要变换手段。

2017-02-11 04:04:11 14086

14086

受外部周期信号激励的震荡,其频率恰为激励信号频率的纯分数,都叫做分频。实现分频的电路或装置称为“分频器”。(纯分数:只有分数部分,即小于1的分数,如3/4就是,而一又五分之四(1+4/5)就不是。)

2017-11-02 10:53:02 35807

35807 三分频,五分频,七分频等等奇数类分频,那究竟怎么办呢?在这里,让我介绍一个可以实现任意整数分频的方法,这个办法也是同样利用了计数器来计算,当是跟偶数分频不一样的地方是任意整数分频利用了两个计数器来实现。 设计原理 : 本

2018-06-13 11:21:48 12390

12390

三分频电路,在电路图中,在一般的利用常规计数器对数字脉冲进行奇数分频时,即使输入是对称信号, 输出也得不到占空比为50%的分频输出,其原因是内部触发器采用的是统一的上升沿(或下降沿)进行触发。

2018-08-13 11:08:34 110927

110927

小数分频是频率合成中的一项新技术。这种技术的特点是使单环锁相频率合成器的平均分频比变为小数。通过使分频比变为小数,可获得任意小的频率间隔,实现高频率分辨力的频率合成,利用小数分频技术完成的小数分频频率合成器,不仅频率分辨力高,而且频率转换速度快,还可使频谱改善、线路简化、体积缩小、程控方便、集成容易。

2019-05-24 08:05:00 1639

1639

关键词:74LS109 , 74LS113 , 分频电路 如图所示为对称输出的三分频电路。在一般的利用常规计数器对数字脉冲进行奇数分频时.即使输入是对称信号,输出也得不到占空比为50%的分频输出

2018-09-28 09:47:01 1726

1726 需要进行调整。输入脉冲是一束一束断续的。经过第一级二分频电路后,虽然对束内的脉冲进行了分频,但在束与柬脉冲的间隙期间既可能处于低电平(如果束内脉冲为偶数个),也可能处于高电平(如果束内脉冲为奇数个),所以在后面加了单稳态电路

2018-10-03 18:12:06 1354

1354 关键词:MC4018 , 分频器 如图所示为数控分频电路。 图(a)为数控分频器原理图。它可以做到任意分频系数且输出为对称方波。对于任意一个偶数N,可以写成N=2M,而对于任意一个奇数N,则可

2018-10-03 18:23:01 526

526 分频器主要分为偶数分频、奇数分频、半整数分频和小数分频,如果在设计过程中采用参数化设计,就可以随时改变参量以得到不同的分频需要。

2019-02-01 01:28:00 15719

15719

分频器是一种基本电路,通常用来对某个给定频率进行分频,得到所需的频率。整数分频器的实现非常简单,可采用标准的计数器,也可以采用可编逻辑器件设计实现。但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。

2019-11-20 07:05:00 6652

6652 论文分析了双模前置小数分频器的分频原理和电路实现。结合脉冲删除技术,提出了一种适于硬件电路实现的任意小数分频的设计方案 ,用 VerilogHDL语 言编程 ,在 QuartusII下对 此方案进 行 了仿 真 ,并用 Cyclone 系 列 的 EP1C12Q240C8芯 片来 实 现 。

2019-08-02 08:00:00 5

5 在数字系统设计中,根据不同的设计需要,经常会遇到偶数分频、奇数分频、半整数分频等,有的还要求等占空比。在基于cpld(复杂可编程逻辑器件)的数字系统设计中,很容易实现由计数器或其级联构成各种形式的偶数分频及非等占空比的奇数分频,但对等占空比的奇数分频及半整数分频的实现较为困难。

2020-06-26 09:36:00 825

825

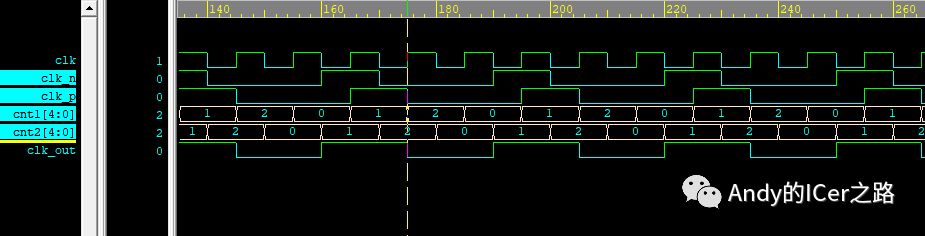

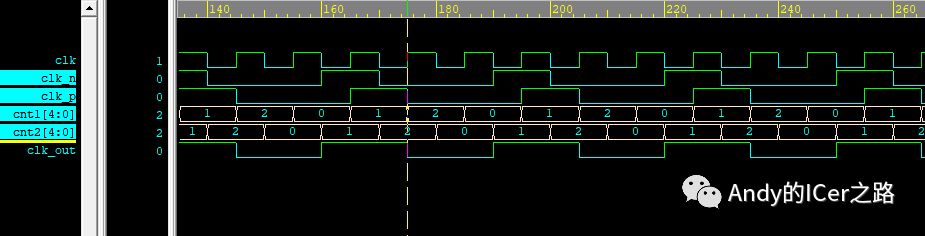

时间段就变成了0.5个周期,就不能通过clk的计数直接实现了。 然而,时钟信号的上升沿和下降沿之间正好相差0.5个周期,利用这个就可以实现奇数分频啦 第一步:分别使用原时钟上升沿和下降沿产生两个计数器(基于上升沿计数的cnt1和基于下降沿计数的cnt2),计数器在

2021-03-12 15:44:54 5614

5614

一种新型的采用电流转向电荷泵的快速锁定小数分频锁相环介绍。

2021-05-08 10:55:08 5

5 分频器是用的最广的一种FPGA电路了,我最初使用的是crazybingo的一个任意分频器,可以实现高精度任意分频的一个通用模块,他的思想在于首先指定计数器的位宽比如32位,那么这个计数器的最大值就是

2021-06-13 17:11:00 4513

4513

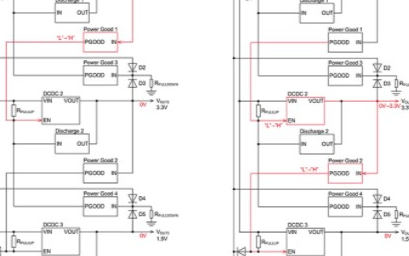

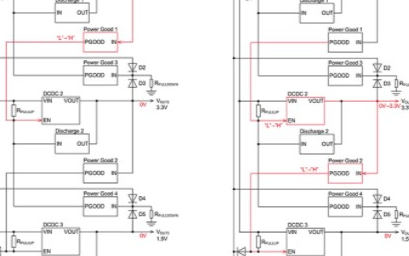

上一篇文章中介绍了使用通用电源IC实现电源时序控制电路的“电源时序规格①”的控制电路。本文先介绍使用通用电源IC实现电源时序控制电路中,电源导通时的时序工作。

2022-01-18 14:50:21 4422

4422

有关小数分频的资料,用于时钟芯片设计,十分经典。

2022-10-24 11:48:44 0

0 在verilog程序设计中,我们往往要对一个频率进行任意分频,而且占空比也有一定的要求这样的话,对于程序有一定的要求,现在我在前人经验的基础上做一个简单的总结,实现对一个频率的任意占空比的任意分频。

2023-01-05 09:33:41 1606

1606 “使用通用电源IC实现电源时序控制的电路”系列文章已经发表了11篇,本文是使用通用电源IC实现电源时序控制的电路的最后一篇。

2023-02-23 10:40:58 900

900 所谓“分频”,就是把输入信号的频率变成成倍数地低于输入频率的输出信号。数字电路中的分频器主要是分为两种:整数分频和小数分频。其中整数分频又分为偶分频和奇分频,首先从偶分频开始吧,入门先从简单的开始!

2023-03-23 15:06:22 948

948

上一篇文章介绍了偶分频,今天来介绍一下奇数分频器的设计。

2023-03-23 15:06:49 692

692

前面分别介绍了偶数和奇数分频(即整数分频),接下来本文介绍小数分频。

2023-03-23 15:08:04 658

658

初学 Verilog 时许多模块都是通过计数与分频完成设计,例如 PWM 脉宽调制、频率计等。而分频逻辑往往通过计数逻辑完成。本节主要对偶数分频、奇数分频、半整数分频以及小数分频进行简单的总结。

2023-03-29 11:38:40 3108

3108

时钟分频电路(分频器)在IC设计中经常会用到,其目的是产生不同频率的时钟,满足系统的需要。 比如一个系统,常规操作都是在1GHz时钟下完成,突然要执行一个操作涉及到模拟电路,所需时间是us量级的,显然用1GHz(周期是1ns)的时钟进行操作是不合适的。

2023-04-25 14:46:25 5332

5332

上一篇文章时钟分频系列——偶数分频/奇数分频/分数分频,IC君介绍了各种分频器的设计原理,其中分数分频器较为复杂,这一篇文章IC君再跟大家聊聊分数分频的具体设计实现。

2023-04-25 14:47:44 1028

1028

入门从简单开始,先来个三分频分析一下。三分频其实就是把输入时钟的三个周期当作一个周期,具体波形如图所示。

2023-06-05 16:57:23 753

753

对于要求相位以及占空比严格的小数分频,建议采用模拟电路实现。而使用数字电路实现只能保证尽量均匀,在长时间内进行分频。

2023-06-05 17:20:51 969

969

是用于满足设计的需求。 分频:产生比板载时钟小的时钟。 倍频:产生比板载时钟大的时钟。 二:分频器的种类 对于分频电路来说,可以分为整数分频和小数分频。 整数分频:偶数分频和奇数分频。 小数分频:半整数分频和非半整数分频。 三:分频器的思想 采用计数器的思想实

2023-11-03 15:55:02 471

471

其实这个分频时钟切换很简单,根本不需要额外的切换电路。一个共用的计数器,加一点控制逻辑,就可以了,而且可以实现2到16任意整数分频率之间的无缝切换。

2023-12-14 15:28:56 257

257

锁相环整数分频和小数分频的区别是什么? 锁相环(PLL)是一种常用的电子电路,用于将输入的时钟信号与参考信号进行同步,并生成输出信号的一种技术。在PLL中,分频器模块起到关键作用,可以实现整数分频

2024-01-31 15:24:48 312

312

电子发烧友App

电子发烧友App

评论