【设计要求】

实现占空比为50%的奇数分频器(示例以三分频为例).

【原理分析】

在进行数字电路设计的过程中,分频器是设计中使用频率较高的一种基本设计之一,虽然很多厂家都提供特定的电路模块对时钟进行分频、倍频以及特定相移等,但是对于时钟要求不高的逻辑,特别是在仿真过程中,使用硬件描述语言实现分频还是较为方便快捷的,同时通过硬件描述语言实现的时钟分频器对于巩固和加深对于硬件描述语言理解不无裨益.

常用的分频器有偶数分频和奇数分频,因为偶数分频相较奇数分频实现较为方便,此处路过不进行赘述.而奇数分频又有占空比(占空比是指在一个脉冲循环内,高电平持续时间在所在整个周期中占据的比例)为50%和不为50%的情况,为了加深理解,本文仅以占空比为50%的奇数分频为例进行说明.

占空比为50%的奇数分频器:当需要进行(2N+1)分频时,偶数分频所使用的的方法已经不适用了,这是因为2N+1的一半是N+0.5,单独对一个时钟计数是得不到0.5个时钟,因为一个计数器只能在时钟的上升沿或者下降沿被采样,所以一个周期之内只能计数一次,无法得到0.5个计数.但是需要注意的是在一个时钟周期内时钟上升沿和下降沿之间刚好相差0.5个时钟周期.

那么结合上升沿和下降沿相差的0.5个时钟周期,就可以得到设计奇数分频器的思路:采用两个完全一样的时钟,其中一个计数器通过上升沿计数,一个计数器通过下降沿计数,然后利用两个计数器的计数值结合偶数分频的方法分别得到两个中间时钟(两个中间时钟的相差为原时钟周期的奇数倍),因为要获取的最终的奇数分频后的时钟的半周期为原时钟周期半周期的奇数倍,所以通过两个中间时钟进行逻辑操作,即可衍生出奇数倍个原时钟的半周期,从而获取到最终的时钟.

即奇数分频器的分频出时钟的特点是:时钟周期的半周期为原时钟周期半周期的奇数倍。

【源代码】

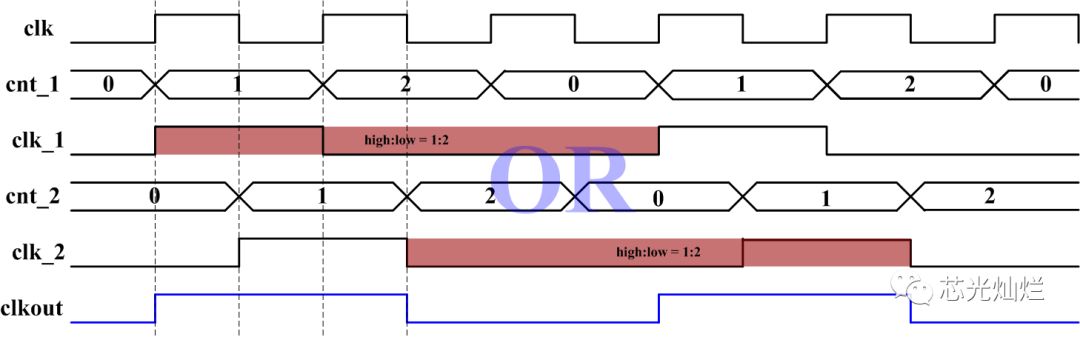

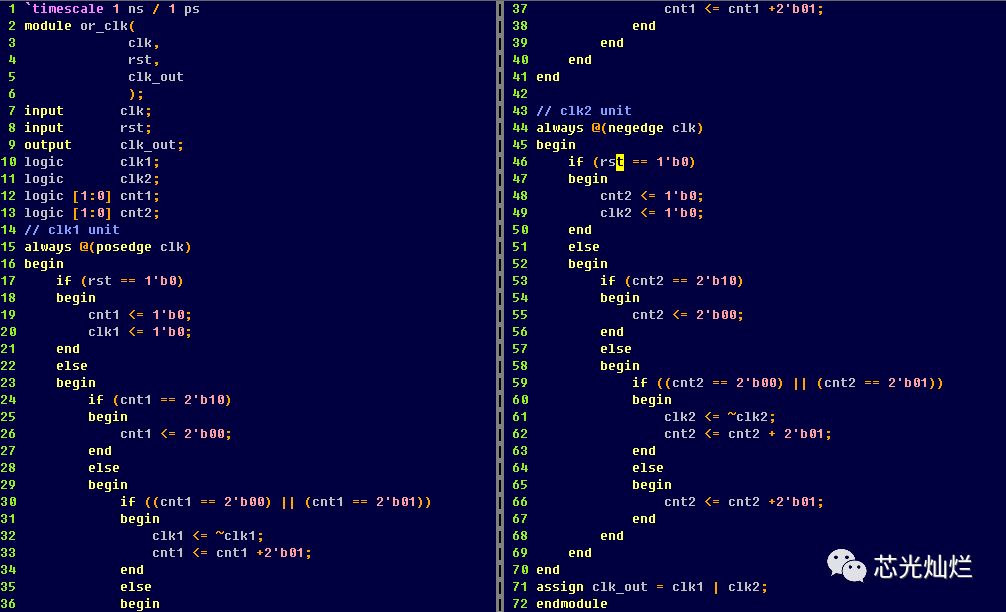

方法一:时钟相或产生

第一步:分别使用原时钟上升沿和下降沿产生两个两位计数器(基于上升沿计数的cnt1和基于下降沿计数的cnt2),计数器在计数到2(即2N)时,计数器归零重新从零开始计数,依次循环;

第二步:cnt1计数到0或者计数到1(即N)时,clk1翻转,从而得到占空比为1:3的clk1;

第三步:cnt2计数到0或者计数到1(即N)时,clk2翻转,从而得到占空比为1:3的clk2;

第四步:因为clk1和clk2相差半个原时钟周期,两个中间时钟进行或操作后,即可得到输出时钟clk_out;

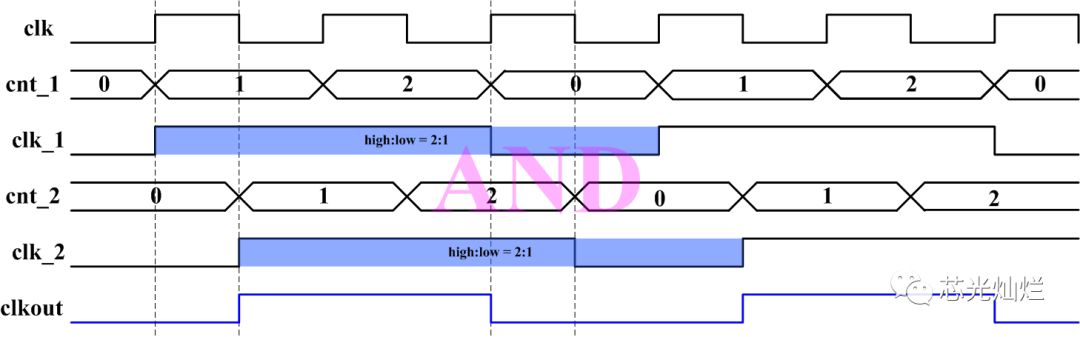

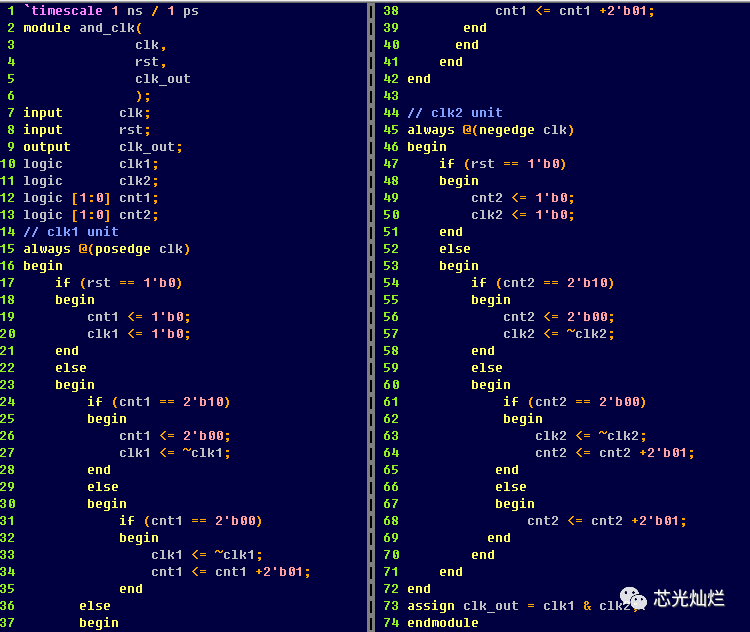

方法二:时钟相与产生

第一步:分别使用原时钟上升沿和下降沿产生两个两位计数器(基于上升沿计数的cnt1和基于下降沿计数的cnt2),计数器在计数到2(即2N)时,计数器归零重新从零开始计数,依次循环.

第二步:cnt1计数到0或者计数到2(即2N)时,clk1翻转,从而得到占空比为2:3的clk1;

第三步:cnt2计数到0或者计数到2(即2N)时,clk2翻转,从而得到占空比为2:3的clk2;

第四步:因为clk1和clk2相差半个原时钟周期,两个中间时钟进行与操作后,即可得到输出时钟clk_out;

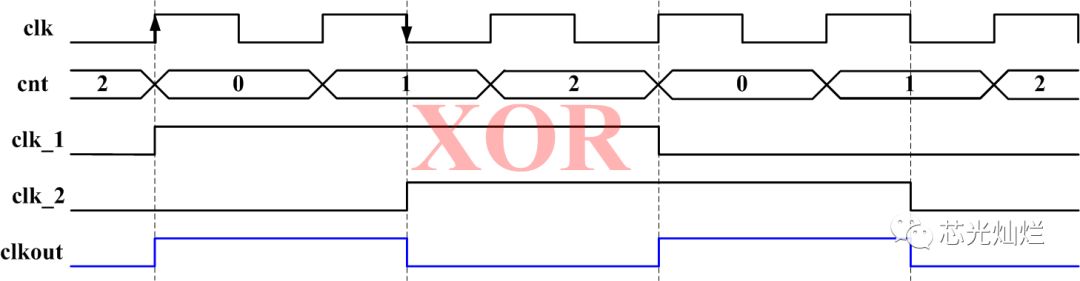

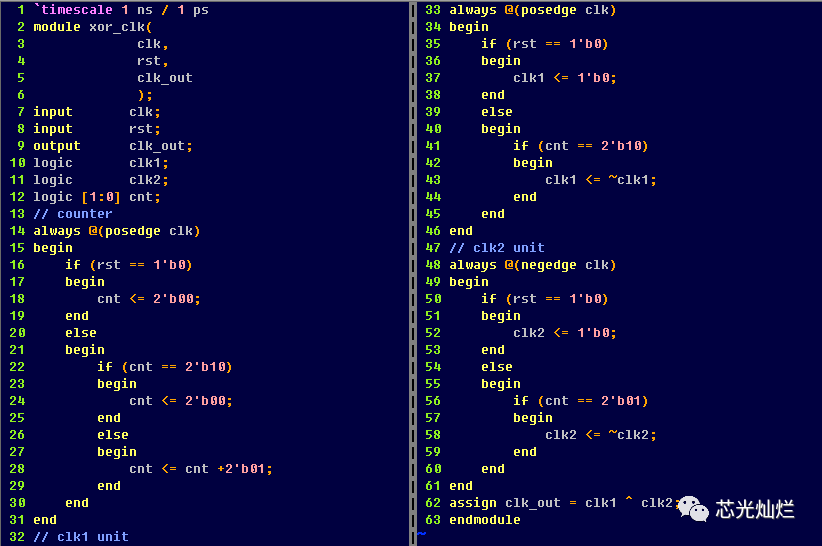

方法三:时钟异或产生

第一步:实现计数功能;

通过时钟上升沿实现计数器功能,在计数到2(即2N)时,计数器归零重新从零开始计数,依次循环;

第二步:上升沿产生中间时钟clk1;

在计数器计数到2时,clk1翻转,实现周期为6(2*(2N+1))的clk1;

第三步: 下降沿产生中间时钟clk2

时钟下降沿采样计数器的计数值,在计数器计数到1(N)时,clk2翻转,实现周期为6的clk2,此时clk1和clk2相位差为1(N)个原时钟周期加半个愿时钟周期;

第四步:clk1和clk2异或,即可得到输出时钟clk_out;

前两种方法使用了两个计数器,最后一种方法使用了一个计数器.因为偶数分频的半时钟周期为原时钟周期的偶数倍,奇数分频时钟周期的半周期为原来时钟周期整数倍加半个时钟周期,因此在进行奇数分频时一定要注意获取到原时钟周期的半个周期,这样才能在进行各种逻辑操作后获取到期望的奇数分频器.

【仿真结果】

【总结】

奇数分频器实际上就是通过两个分频器输出逻辑操作后获得,关键点在于两个分频器需通过待分频时钟的上升沿和下降沿分别进行设计。

-

分频器

+关注

关注

43文章

536浏览量

52259 -

计数器

+关注

关注

32文章

2306浏览量

97566 -

占空比

+关注

关注

0文章

114浏览量

29987 -

CLK

+关注

关注

0文章

132浏览量

17932

发布评论请先 登录

奇数分频如何得到呢? 解读奇数分频和逻辑分析仪(ILA)的使用

需要讲解一个占空比50%的奇数分频器的原理

基于FPGA 的等占空比任意整数分频器的设计

分频器的作用是什么 半整数分频器原理图分析

基于复杂可编程逻辑器件和VHDL语言实现半整数分频器的设计

FPGA学习-分频器设计

如何实现一种占空比为50%的奇数分频器设计呢?

如何实现一种占空比为50%的奇数分频器设计呢?

评论