学习内容

近期设计需要用到AXI总线的IP,所以就对应常用的IP进行简要的说明,本文主要对AXI互联IP进行介绍。

基础架构IP

基础的IP是用于帮助组装系统的构建块。基础架构IP往往是一个通用IP,它使用通用的AXI4接口在系统中移动或转换数据,而不解释数据。

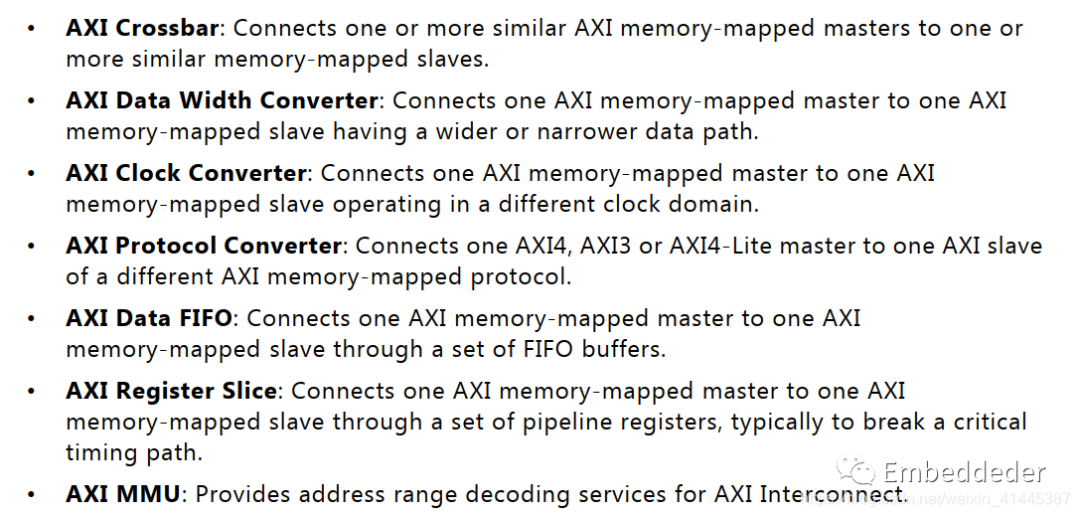

这些基础的IP各自有自己的常用的功能,下面列举出一部分AXI接口的基础构架IP。

° AXI Register slices (for pipelining)用于流水线操作。° AXI FIFOs (for buffering/clock conversion)用于缓存和时钟转换。° AXI Interconnect IP and AXI SmartConnect IP (for connecting memory-mapped IP together)用于连接存储器映射的IP互连。

° AXI Direct Memory Access (DMA) engines (for memory-mapped to stream conversion)用于存储器映射和数据流接口的转换。° AXI Performance Monitors and Protocol Checkers (for analysis and debug)用于分析仿真。° AXI Verification IP (for simulation-based verification and performance analysis) 用于仿真验证。

Xilinx AXI SmartConnect IP and AXI Interconnect IP(AXI互联IP)介绍

Xilinx AXI Interconnect IP和AXI SmartConnect IP都可以将一个或多个AXI存储器映射的主设备连接到一个或多个存储器映射的从设备。而使用AXI SmartConnect IP,更紧密地集成到Vivado设计环境中,用户以最小的用户干预自动配置和适应已连接的AXI主从IP。AXI互联IP(AXI SmartConnect IP and AXI Interconnect IP)可以用于所有的存储器映射设计中。

在某些情况下,对于高带宽应用程序,使用SmartConnect IP可以提供更好的优化。AXI SmartConnect IP通过综合针对重要接口进行优化的低区域自定义互连,在低延迟下提供最大的系统吞吐量。

AXI Interconnect IP(axi_interconnect)可以将一个或多个AXI存储器映射的主设备连接到一个或多个存储器映射的从设备。Interconnect 相对于SmartConnect IP更符合来自ARM的AMBA AXI4规范,包括AXI4-Lite 接口。

AXI Interconnect IP和AXI SmartConnect IP仅用于存储器映射传输。AXI4-Stream传输不适用。但可以使用AXI4-Stream Interconnect IP (axis_interconnect)。带有AXI4-Stream接口的IP通常彼此连接到DMA IP或者AXI4-Stream Interconnect IP上。

综上:对于中到高性能设计,推荐使用AXI SmartConnect IP,因为它在面积和时间上提供了更好的向上扩展。对于低性能(AX14-Lite)或中小型复杂性设计,AXI Interconnect IP可能更有效的面积。

AXI Interconnect IP使用方式

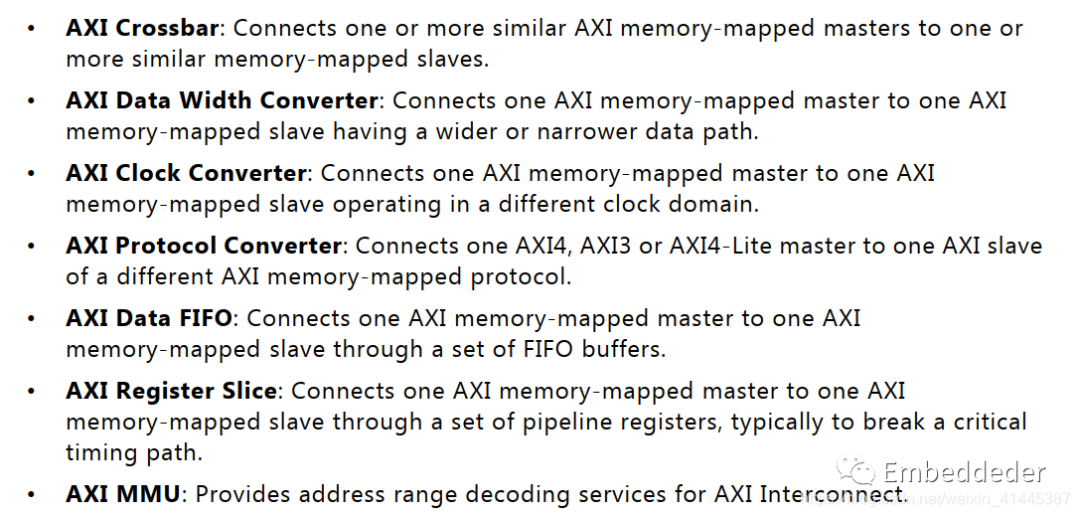

对于互联IP的使用,在xilinx的指导手册中提到了下述四种方式。

1. Conversion Only(仅转换操作)

当一个主设备连接到一个从设备时,AXI Interconnect IP可以执行各种转换和流水线功能。这些操作如下述:

数据宽度转换

时钟速率转换

AXI4-Lite从机自适配

AXI4-3从机自适配

流水线,如寄存器或数据通道FIFO操作。

在这些情况下,AXI Interconnect IP不包含仲裁、解码或路由等逻辑。可能会导致延迟,延迟大小取决于正在执行的转换类型。

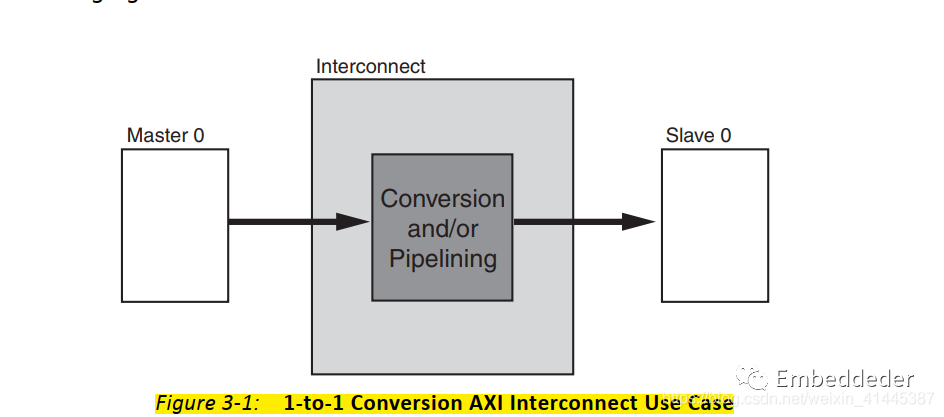

下图显示了一个转换的示例:

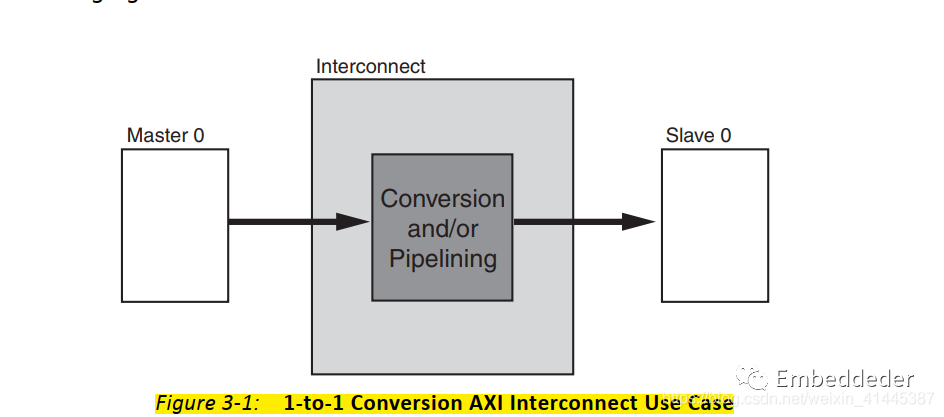

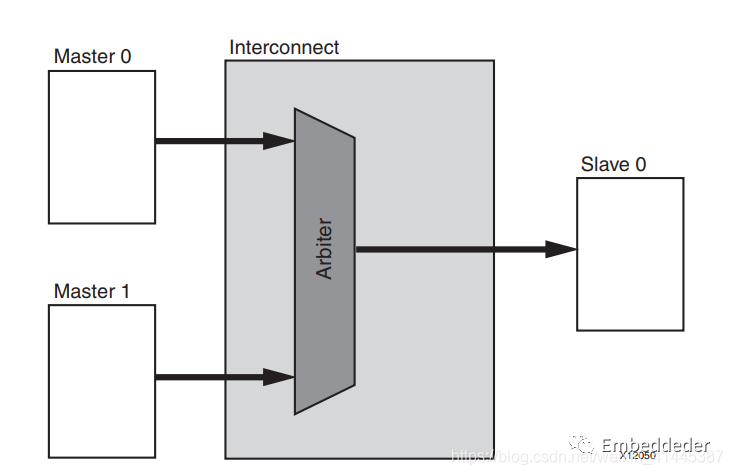

2. N-to-1 Interconnect

AXI Interconnect IP的一个常见退化配置(或者我翻译为简化配置)是多个主设备为访问一个从设备(通常是一个内存控制器)进行仲裁。在这些情况下,地址解码逻辑可能是不必要的,并且在AXI Interconnect IP被省略(除非需要地址范围验证)。在这种配置下,还可以执行数据宽度和时钟速率转换等转换功能。N-to-1 AXI互联示例如下图所示:

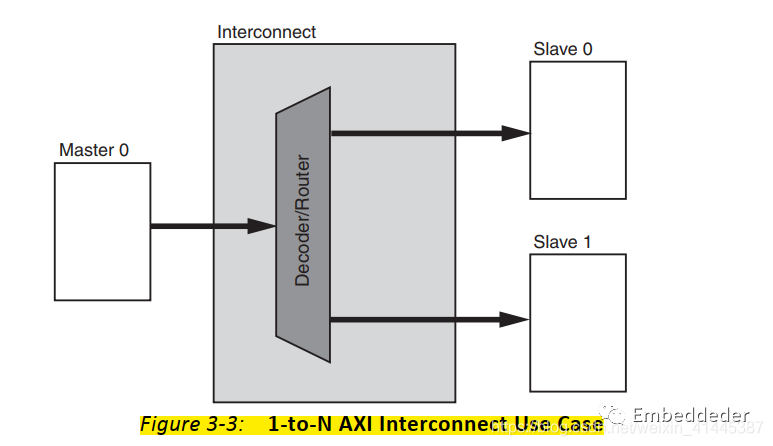

3. 1-to-N Interconnect

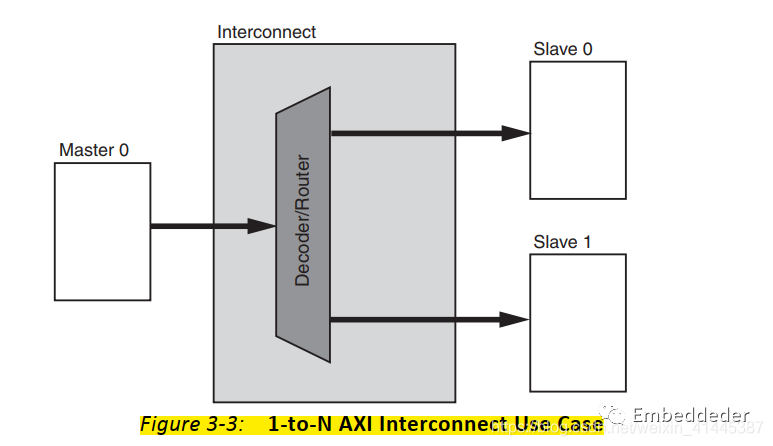

AXI Interconnect IP的另一种退化配置(简化配置)是当一个主设备(通常是一个处理器)访问多个内存映射的从外围设备时。在这些情况下,仲裁(在地址和写数据路径)不执行。1 - N互联示例如下图所示:

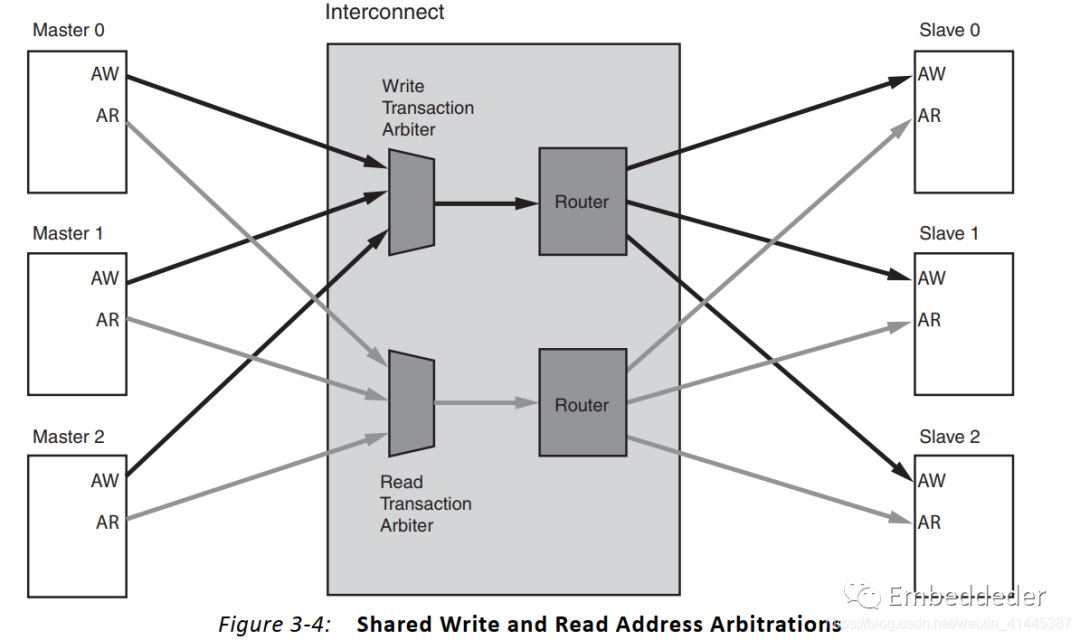

4. N-to-M Interconnect (Sparse Crossbar Mode)

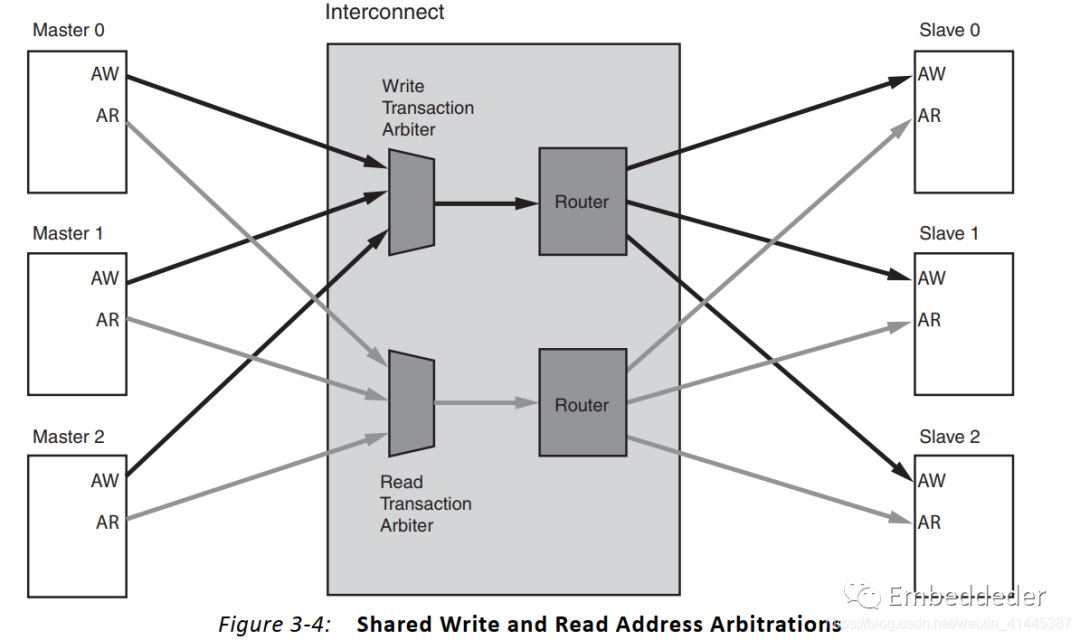

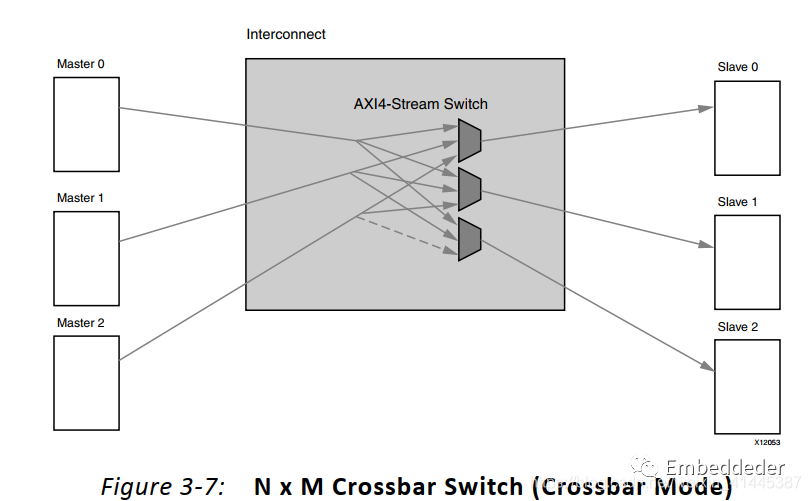

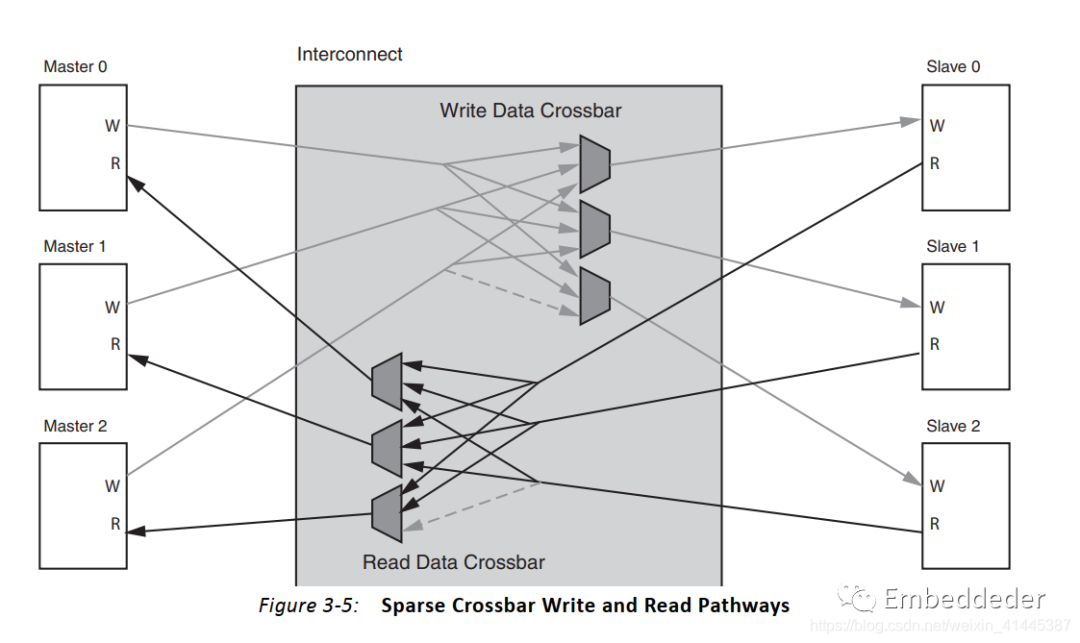

AXI Interconnect的N-to-M用例采用共享地址多数据(SAMD)拓扑,稀疏数据交叉连接,单线程写和读地址仲裁,如下图所示:

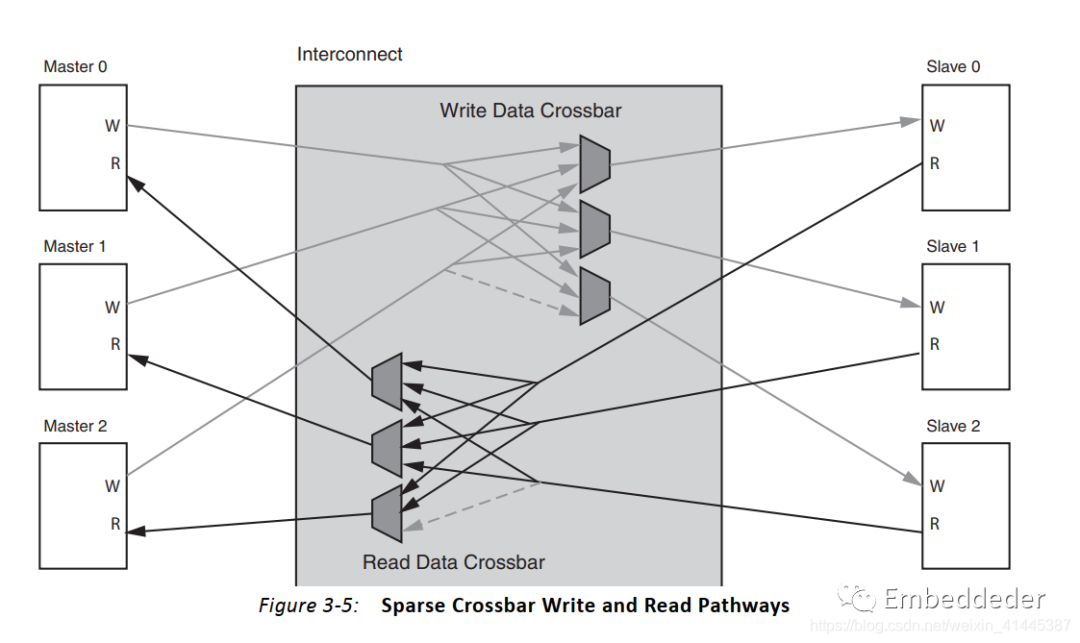

下图展示了稀疏交叉写和读数据路径:

根据配置的稀疏连接映射,并行写和读数据通道将每个SI插槽(连接到左边的AXI主机上)连接到它可以访问的所有MI插槽(连接到右边的AXI从机上)。当多个源有数据要发送到不同的目的地时,只要满足AXI排序规则,数据传输就可以独立并发地进行。在所有SI槽(如果> 1)中的写地址通道馈送到一个中心地址仲裁器,它一次授予对一个SI槽的访问权,对于读地址通道也是如此。

AXI4-Stream Interconnect Core IP介绍

AXI4-Stream Interconnect Core IP(axis_interconnect)将一个或多个AXI4-Stream主设备连接到一个或多个AXI4-Stream从设备。AXI4-Stream Interconnect Core IP 仅用于AXI4-Stream 传输;AXI4存储器映射传输不适用。

AXI4-Stream Interconnect Core 内部框图

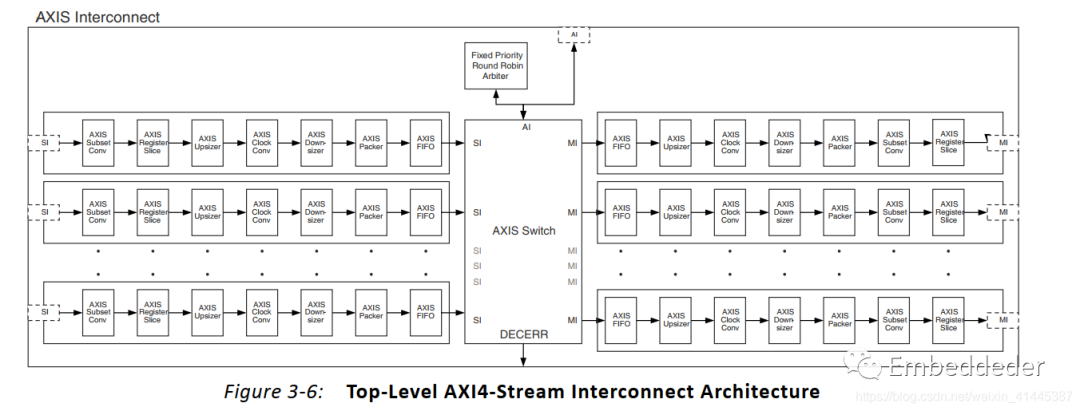

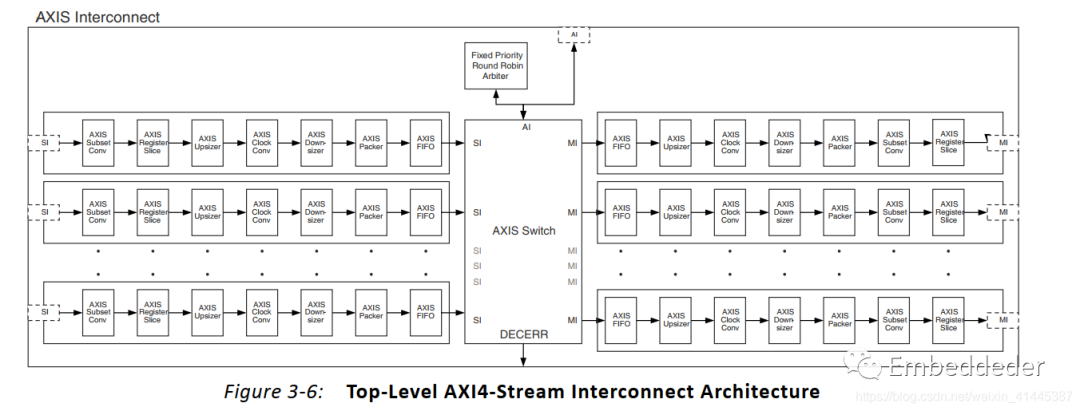

AXI4-Stream Interconnect Core IP由SI、MI和包括它们之间的AXI通道的功能单元组成。

SI接受来自连接的主设备的事务请求。

MI向从设备发送事务。

在中心是交换机,它仲裁和路由连接到SI和MI的各种设备之间的通信。

AXI4-Stream Interconnect Core IP还包括位于交换机和每个SI和MI接口之间的其他功能单元,可选择性地执行各种转换和存储功能。该开关有效地将AXI4-Stream Interconnect Core IP从SI相关功能单元(SI半球)和MI相关单元(MI半球)中间分开。这个架构类似于AXI Interconnect IP的架构。

AXI4-Stream Interconnect IP使用方式

AXI4-Stream Interconnect IP将一个或多个AXI4-Stream主设备连接到一个或多个AXI4-Stream从设备。对于AXI4-Stream Interconnect IP,主要有两种使用方式:

流数据路由和交换

流多路复用和去多路复用

Streaming Data Routing and Switching (Crossbar Mode)流数据路由和交换

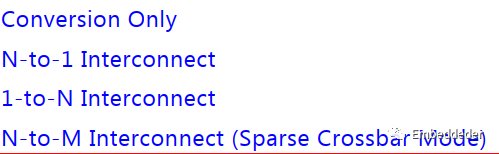

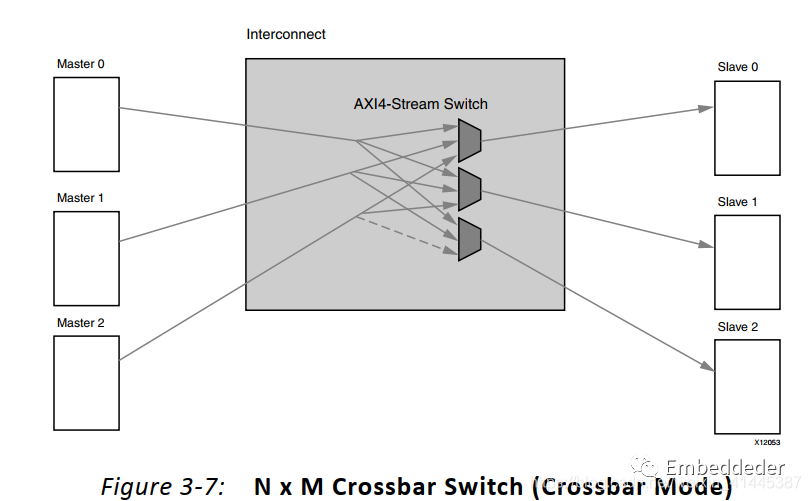

ax14流互连可以实现N × M全交叉开关,如下图所示。它支持从端仲裁,能够在N个主服务器和M个从服务器之间并行数据传输。解码器和仲裁者服务于主从之间的路由数据传输交互。

Stream Multiplexing and De-multiplexing(流多路复用和去多路复用)

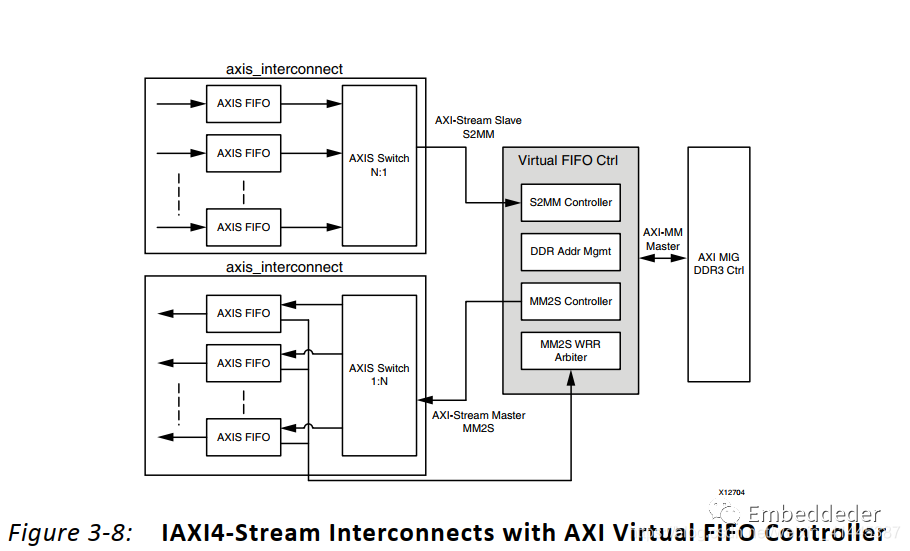

你可以在Nx1配置中将AXI4-Stream Interconnect IP配置为一起多路传输流,然后配置为1xM来解多路传输流。使用多路复用和多路复用解复用来创建多通道流,其中较小数量的导线可以携带来自多个主从的共享流量。

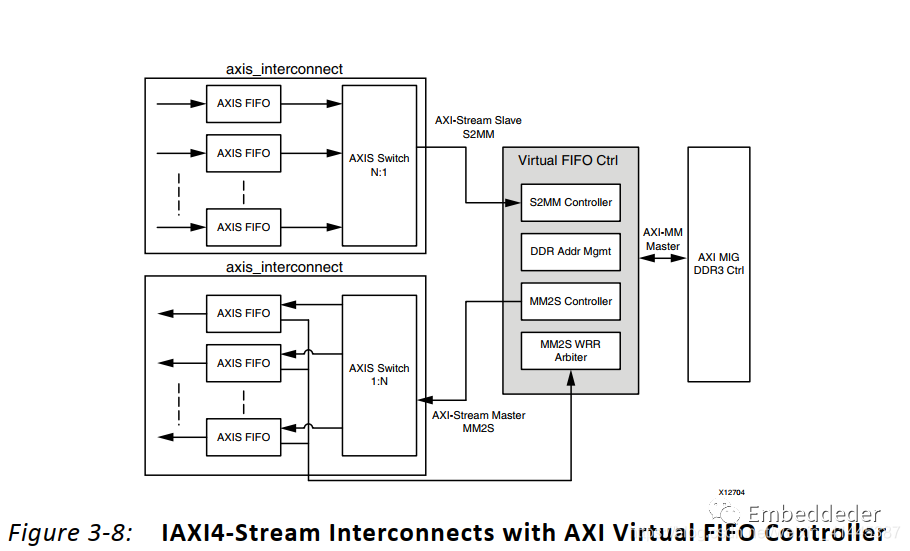

例如,在下面的图中,AX14-Stream互连与AXI虚拟FIFO控制器一起用于从多个端点主从复用和解复用多个流。

Reference

正点原子讲解视频

UG1037

Vuko csdn博客同步更新~

欢迎大家关注我的博客。如果需要工程微信后台留言即可~

学习内容

近期设计需要用到AXI总线的IP,所以就对应常用的IP进行简要的说明,本文主要对AXI互联IP进行介绍。

基础架构IP

基础的IP是用于帮助组装系统的构建块。基础架构IP往往是一个通用IP,它使用通用的AXI4接口在系统中移动或转换数据,而不解释数据。

这些基础的IP各自有自己的常用的功能,下面列举出一部分AXI接口的基础构架IP。

° AXI Register slices (for pipelining)用于流水线操作。° AXI FIFOs (for buffering/clock conversion)用于缓存和时钟转换。° AXI Interconnect IP and AXI SmartConnect IP (for connecting memory-mapped IP together)用于连接存储器映射的IP互连。° AXI Direct Memory Access (DMA) engines (for memory-mapped to stream conversion)用于存储器映射和数据流接口的转换。° AXI Performance Monitors and Protocol Checkers (for analysis and debug)用于分析仿真。° AXI Verification IP (for simulation-based verification and performance analysis) 用于仿真验证。

Xilinx AXI SmartConnect IP and AXI Interconnect IP(AXI互联IP)介绍

Xilinx AXI Interconnect IP和AXI SmartConnect IP都可以将一个或多个AXI存储器映射的主设备连接到一个或多个存储器映射的从设备。而使用AXI SmartConnect IP,更紧密地集成到Vivado设计环境中,用户以最小的用户干预自动配置和适应已连接的AXI主从IP。AXI互联IP(AXI SmartConnect IP and AXI Interconnect IP)可以用于所有的存储器映射设计中。

在某些情况下,对于高带宽应用程序,使用SmartConnect IP可以提供更好的优化。AXI SmartConnect IP通过综合针对重要接口进行优化的低区域自定义互连,在低延迟下提供最大的系统吞吐量。

AXI Interconnect IP(axi_interconnect)可以将一个或多个AXI存储器映射的主设备连接到一个或多个存储器映射的从设备。Interconnect 相对于SmartConnect IP更符合来自ARM的AMBA AXI4规范,包括AXI4-Lite 接口。

AXI Interconnect IP和AXI SmartConnect IP仅用于存储器映射传输。AXI4-Stream传输不适用。但可以使用AXI4-Stream Interconnect IP (axis_interconnect)。带有AXI4-Stream接口的IP通常彼此连接到DMA IP或者AXI4-Stream Interconnect IP上。

综上:对于中到高性能设计,推荐使用AXI SmartConnect IP,因为它在面积和时间上提供了更好的向上扩展。对于低性能(AX14-Lite)或中小型复杂性设计,AXI Interconnect IP可能更有效的面积。

AXI Interconnect IP使用方式

对于互联IP的使用,在xilinx的指导手册中提到了下述四种方式。

1. Conversion Only(仅转换操作)

当一个主设备连接到一个从设备时,AXI Interconnect IP可以执行各种转换和流水线功能。这些操作如下述:

数据宽度转换

时钟速率转换

AXI4-Lite从机自适配

AXI4-3从机自适配

流水线,如寄存器或数据通道FIFO操作。

在这些情况下,AXI Interconnect IP不包含仲裁、解码或路由等逻辑。可能会导致延迟,延迟大小取决于正在执行的转换类型。

下图显示了一个转换的示例:

2. N-to-1 Interconnect

AXI Interconnect IP的一个常见退化配置(或者我翻译为简化配置)是多个主设备为访问一个从设备(通常是一个内存控制器)进行仲裁。在这些情况下,地址解码逻辑可能是不必要的,并且在AXI Interconnect IP被省略(除非需要地址范围验证)。在这种配置下,还可以执行数据宽度和时钟速率转换等转换功能。N-to-1 AXI互联示例如下图所示:

3. 1-to-N Interconnect

AXI Interconnect IP的另一种退化配置(简化配置)是当一个主设备(通常是一个处理器)访问多个内存映射的从外围设备时。在这些情况下,仲裁(在地址和写数据路径)不执行。1 - N互联示例如下图所示:

4. N-to-M Interconnect (Sparse Crossbar Mode)

AXI Interconnect的N-to-M用例采用共享地址多数据(SAMD)拓扑,稀疏数据交叉连接,单线程写和读地址仲裁,如下图所示:

下图展示了稀疏交叉写和读数据路径:

根据配置的稀疏连接映射,并行写和读数据通道将每个SI插槽(连接到左边的AXI主机上)连接到它可以访问的所有MI插槽(连接到右边的AXI从机上)。当多个源有数据要发送到不同的目的地时,只要满足AXI排序规则,数据传输就可以独立并发地进行。在所有SI槽(如果> 1)中的写地址通道馈送到一个中心地址仲裁器,它一次授予对一个SI槽的访问权,对于读地址通道也是如此。

AXI4-Stream Interconnect Core IP介绍

AXI4-Stream Interconnect Core IP(axis_interconnect)将一个或多个AXI4-Stream主设备连接到一个或多个AXI4-Stream从设备。AXI4-Stream Interconnect Core IP 仅用于AXI4-Stream 传输;AXI4存储器映射传输不适用。

AXI4-Stream Interconnect Core 内部框图

AXI4-Stream Interconnect Core IP由SI、MI和包括它们之间的AXI通道的功能单元组成。

SI接受来自连接的主设备的事务请求。

MI向从设备发送事务。

在中心是交换机,它仲裁和路由连接到SI和MI的各种设备之间的通信。

AXI4-Stream Interconnect Core IP还包括位于交换机和每个SI和MI接口之间的其他功能单元,可选择性地执行各种转换和存储功能。该开关有效地将AXI4-Stream Interconnect Core IP从SI相关功能单元(SI半球)和MI相关单元(MI半球)中间分开。这个架构类似于AXI Interconnect IP的架构。

AXI4-Stream Interconnect IP使用方式

AXI4-Stream Interconnect IP将一个或多个AXI4-Stream主设备连接到一个或多个AXI4-Stream从设备。对于AXI4-Stream Interconnect IP,主要有两种使用方式:

流数据路由和交换

流多路复用和去多路复用

Streaming Data Routing and Switching (Crossbar Mode)流数据路由和交换

ax14流互连可以实现N × M全交叉开关,如下图所示。它支持从端仲裁,能够在N个主服务器和M个从服务器之间并行数据传输。解码器和仲裁者服务于主从之间的路由数据传输交互。

Stream Multiplexing and De-multiplexing(流多路复用和去多路复用)

你可以在Nx1配置中将AXI4-Stream Interconnect IP配置为一起多路传输流,然后配置为1xM来解多路传输流。使用多路复用和多路复用解复用来创建多通道流,其中较小数量的导线可以携带来自多个主从的共享流量。

例如,在下面的图中,AX14-Stream互连与AXI虚拟FIFO控制器一起用于从多个端点主从复用和解复用多个流。

编辑:jq

-

控制器

+关注

关注

112文章

15223浏览量

171174 -

数据

+关注

关注

8文章

6511浏览量

87596 -

IP

+关注

关注

5文章

1404浏览量

148272 -

fifo

+关注

关注

3文章

369浏览量

43069

原文标题:ZYNQ-AXI互联IP介绍

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

使用 PCIE 更新 AMD ZYNQ™ 的 QSPI Flash 参考设计

XILINX FPGA IP之AXI Traffic Generator

基于zynq7020器件来搭建Linux系统

ZYNQ的ARM和FPGA数据交互——AXI交互最重要的细节

LogiCORE IP AXI UART 16550内核简介

LogiCORE JTAG至AXI Master IP核简介

什么是AXI?AXI如何工作?

LogiCORE IP AXI4-Stream FIFO内核解决方案

AXI VIP当作master时如何使用?

自定义AXI-Lite接口的IP及源码分析

简单讲解AXI Interconnect IP核的使用方法

Video In to AXI4-Stream IP核知识介绍

全面介绍ZYNQ-AXI互联IP

全面介绍ZYNQ-AXI互联IP

评论