在一个项目中,当你使用microblaze作为控制器来进行系统调度的时候,一般是建议将所有模块封装成AXI形式的IP核,这样好管理,也容易调试。不过在初期的时候是不建议这样做的,因为你的模块并没有完全被验证是没问题的,所以还是使用.v文件,等后面这一功能验证通过,再把它封装成IP核形式。

1. AXI IP核简介

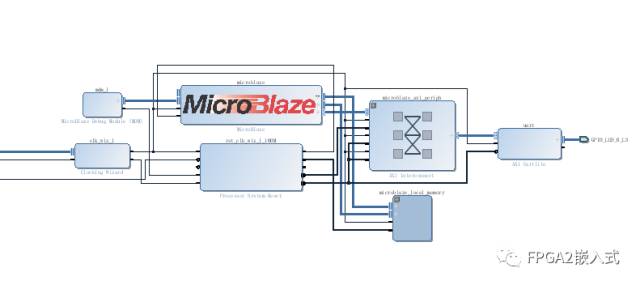

用过Microblaze或者看例程的人肯定都知道,Xilinx提供了很多AXI形式的IP核,像常用的UART、IIC、SPI等IP核。我们只要把他们在画布里调出来,然后使用自动连接形式,便能把对应接口连接起来,接着在软件上调用其相应的函数便可以工作了。

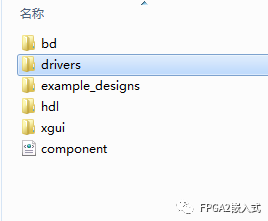

但是当我们自己封装了一个AXI形式的IP核后,又该怎么去使用呢?这不是官方IP,没有相应的函数呀?不知道大家是否有印象,上一篇文章介绍IP封装的时候说过,封装成AXI形式的IP核,会生成一些东西,如下图所示,这个可千万别去删,大有用处的。

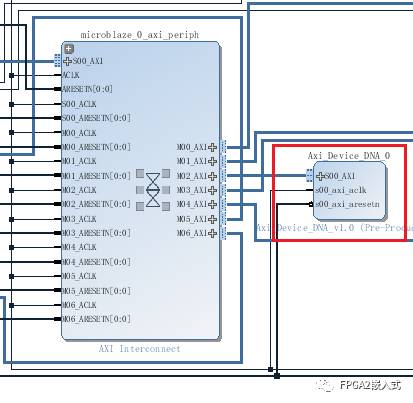

里面的drivers这个文件夹其实放的就是AXI的驱动函数。例如我们生成一个AXI的IP核(红框处)

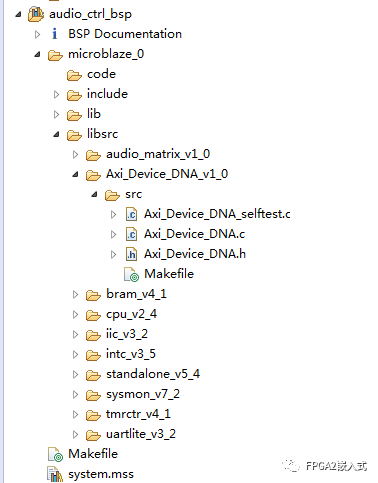

编译通过后生成软核工程,可以看到,我们自己加入的IP核是有被关联进来的。在“Axi_Device_DNA_v1_0”这个文件夹下包含有.c和.h文件,这个就是我们添加的IP核对应的驱动,它和iic、定时器、uart等IP核在同一个库里。这些都是IP核必须使用到的函数文件。

2. AXI IP核使用

看见自制的IP核都能给你生成驱动函数是不是觉得很高级,很爽呢!如果这样想那你就确实too young too simple了。打开它的.c和.h文件给你看看吧。

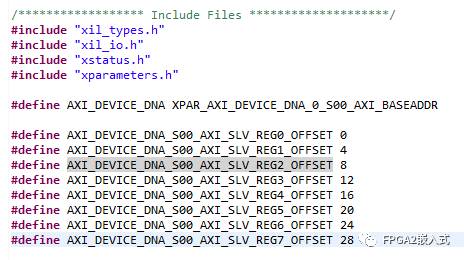

寄存器定义

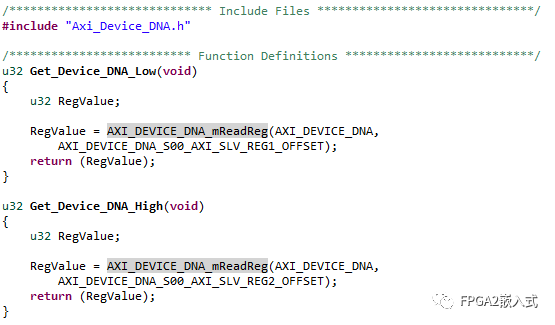

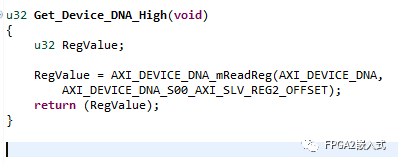

获取DNA数据高位、低位数据的函数

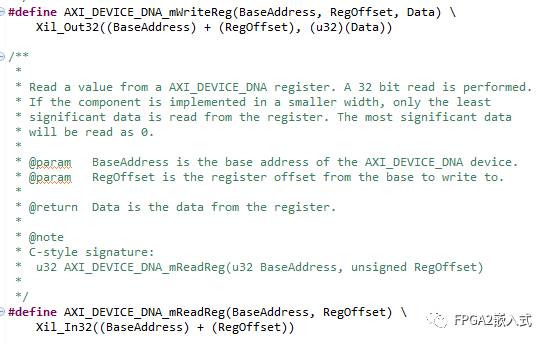

读写函数

是的,就只有这些,没有了!所以别以为能像IIC之类的IP核一样,会给你很全的函数,让你一次写一大串或读一大串数据的,如果真能根据不同IP功能给你定制不同函数,那就智能到逆天了···

不过人家都给你读写寄存器的函数和寄存器的定义,也就已经够了,都说下层基础决定上层建筑,有了这两个基本函数,你想自己做什么功能还不行?MCU控制的本质不也就是读写对应的寄存器,偷懒也得有个度的哈哈~就像这样,自己封装个函数就行了。

当然,你也可以不用Xilinx给你生成的读写函数,自己写也是可以的,不过不建议这么做,毕竟人家都给了,一方面可以给你节省编码时间,另一方面也保证了函数的稳定性,避免开发出错。

3. 总结

在封装成AXI IP 核时会有一个顶层的AXI时序代码,这个用户一定要熟悉,并且对应的寄存器要设置好,这样使用起来才不会有错误。不然容易出现寄存器读写不成功或者操作错寄存器导致数据不对。总之还是一句话,实践出真知,想了解深入得去用了才知道才会使用。

编辑:lyn

-

Xilinx

+关注

关注

70文章

2121浏览量

119372 -

MicroBlaze

+关注

关注

3文章

66浏览量

21436 -

IP核

+关注

关注

4文章

317浏览量

49041

原文标题:使用MicroBlaze调用AXI IP核

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

XILINX FPGA IP之AXI Traffic Generator

FPGA新IP核学习的正确打开方式

LogiCORE IP AXI UART 16550内核简介

LogiCORE JTAG至AXI Master IP核简介

什么是AXI?AXI如何工作?

LogiCORE IP AXI4-Stream FIFO内核解决方案

基于Xilinx FPGA AXI-EMC IP的EMIF通信测试

MicroBlaze MCS和MicroBlaze的区别在哪?

自定义AXI-Lite接口的IP及源码分析

简单讲解AXI Interconnect IP核的使用方法

Video In to AXI4-Stream IP核知识介绍

如何使用MicroBlaze调用AXI IP核详细解析

如何使用MicroBlaze调用AXI IP核详细解析

评论