ADI最近推出业界性能最高的ADF4159 13 GHz PLL频率合成器。ADF4159实现了突破性的110 MHz鉴频鉴相器工作频率,同时功耗低于100mW,仅为竞争解决方案的五分之一

2012-07-04 09:30:43 1726

1726 Analog Devices, Inc.(ADI),最近发布了一款提供领先相位噪声性能的PLL频率合成器ADF4153A。

2012-11-01 09:09:20 1497

1497 通过正确的设计方法,结合使用现代低成本高集成度的PLL和直接数字合成器(DDS)集成电路(IC)可以极大地促进高性能架构的实现。

2013-05-17 10:05:58 3325

3325

几乎每个RF和微波系统都需要频率合成器。频率合成器产生本振信号以驱动混频器、调制器、解调器及其他许多RF和微

2017-12-07 07:11:00 8835

8835

已经有段时间了。但是,在要求快速切换速度、低相位噪声或低杂散信号电平的场合,有必要使用更为复杂的架构。通过正确的设计方法,结合使用现代低成本高集成度的PLL和直接数字合成器(DDS)集成电路(IC)可以极大地促进高性能架构的实现。

2022-10-14 10:30:36 2025

2025 本篇文章是关于相位锁定环(PLL)频率合成器的设计和分析,重点讨论了相位噪声和频率噪声的测量、建模和仿真方法。文章以设计一个假想的PLL频率合成器为例,详细介绍了设计过程和步骤。从规格选择、电路配置

2023-10-26 15:30:51 483

483

概述:ADF41020是一款18GHz微波PLL频率合成器,ADF41020 频率合成器在无线接收机和发射机的上变频和下变频部分中,可用来实现高达18 GHz 的本振。

2021-04-12 07:59:42

DDS直接数字频率合成器、信号发生器、函数发生器1.DDS直接数字频率合成器、信号发生器、函数发生器他们之间有哪些异同?2.目前只发现ADI有相关的产品,国产有哪些品牌可以推荐3.如果要输出的频率和功率是实时可调的,用MCU控制DDS芯片是否可以实现?

2022-03-24 18:10:02

的输出,并且如果正弦波不够完美的话,在振荡器内部稍微改造下来改变它的性能。当合成器执行反馈时,它们有时称为锁相环或PLL。www实际生活中的介成器作常复杂,也很昂贵。它们可以完成许多功能而不仅仅是反馈

2017-12-06 14:06:07

频率合成器的高性能架构实现技术详解

2021-04-07 06:48:49

(DDS),内置一个12位数模转换器,目标工作速率最高达3.5 GSPS。该器件采用先进的DDS技术,连同高速、高性能数模转换器,构成数字可编程的完整高频合成器,能够产生最高1.4 GHz的频率捷变模拟输出

2019-06-17 15:28:25

`AD9914BCPZ直接数字频率合成器AD9914是一款直接数字频率合成器(DDS),内置一个12位数模转换器,目标工作速率最高达3.5 GSPS。该器件采用先进的DDS技术,连同高速、高性能

2020-11-18 11:36:18

的DDS技术,连同高速、高性能数模转换器,构成数字可编程的完整高频合成器,能够产生1.4 GHz的频率捷变模拟输出正弦波。AD9914专为提供快速跳频和精密调谐分辨率(标准模式下32位、可编程模数模式下

2019-04-29 15:06:55

DAC模拟乘法器、DDS(频率合成器)、信号发生器1.DAC模拟乘法器构成的混频器是否可以和DDS(频率合成器)、信号发生器一样?可以生成任意目前波形?2.DDS(频率合成器)、信号发生器它俩之间有存在哪些异同?

2022-03-24 17:24:37

。选择频率合成器芯片时,第一步是决定使用整数N还是分数N型频率合成器。设计良好的Σ-Δ分数N频率合成器能够在相位噪声、PLL锁定时间和鉴相噪声抑制方面提供优异的性能。虽然分数N频率合成器的成本不断降低,但

2019-06-26 06:42:04

的输出能否具有调幅(AM)、调频(FM)和调相(PM)等功用。 随着电子技术的不时开展,对频率合成器性能的请求越来越高。20世纪80年代以来,各国都在研制和开展各自的DDS产品,如今盛行的DDS产品以

2020-03-17 14:54:24

频率合成技术是现代通信的重要组成部分,它是将一个高稳定度和高准确度的基准频率经过四则运算,产生同样稳定度和准确度的任意频率。频率合成器是电子系统的心脏,是影响电子系统性能的关键因素之一。本文结合

2019-06-25 06:36:13

问:什么是PLL频率合成器?

2019-09-17 19:00:51

和相位来生成被调制信号,因此对于数字通信系统来说可以产生任意的波形。软件无线电系统中的数字上下变频、本地载波的产生以及压控震荡器等重要环节都可以用DDS技术实现。 采用DDS技术的直接数字频率合成器

2019-08-19 19:18:00

限,因此在设计工作频率宽、调协精度高的频率合成器时,这两种方式均不能满足技术要求。但是,采用DDS+PLL方式,可以满足高精度和宽频带的需要,其实现的难点是如何提高合成器输出频谱纯度。在实际印制电路板制作中,DDS的良好接地和合理布线非常有助于系统设计的实现。来源:与非网

2011-07-16 09:09:54

(DDS)技术,提出毫米波频率合成器的设计方案。进行方案系统实验,结果表明,相位噪声为-85dBc/Hz@10kHz,提升了整个毫米波通信系统的性能。【关键词】:毫米波;;频率合成;;相位噪声;;频率

2010-04-22 11:47:22

直接数字频率合成(DDS)在过去十年受到了频率合成器设计工程师极大的欢迎,它被认为是一种具有低相位噪声和优良杂散性能的灵活的频率源,基于DDS的频率合成器在许多应用中能比基于锁相环(PLL)频率

2019-07-08 07:26:17

本文设计了一种多环锁相频率合成器。多环锁相环路有直接数字频率合成(DDS)环路和锁相频率合成环路(PLL)组成。充分利用两个不同环路的优点,既保证了高的输出频率,又得到了较高的频率分辨率。【关键词

2010-05-13 09:09:53

电子技术应用频率合成技术是现代通信的重要组成部分,它是将一个高稳定度和高准确度的基准频率经过四则运算,产生同样稳定度和准确度的任意频率。频率合成器是电子系统的心脏,是影响电子系统性能的关键因素之一

2019-07-30 07:55:22

PLL应用中颇具价值的注意事项和使用技巧基于锁相环(PLL)技术的频率合成器

2021-05-12 06:59:03

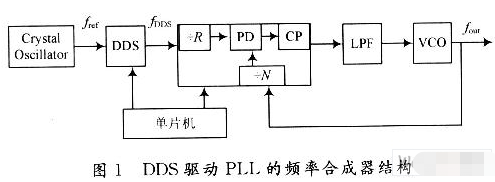

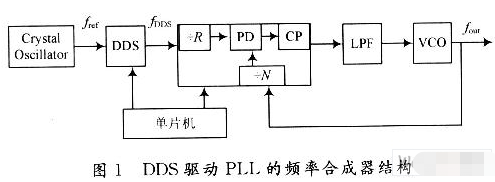

本文将介绍DDS和PLL的工作原理,并结合一电台(工作频率2 MHz~500 MHz)的设计,给出DDS做参考的PLL频率合成器的设计方案。

2021-04-20 06:42:27

的技术和器件产,它的性牟指标尚不能与已有的技术盯比,故未受到重视。近1年间,随着微电子技术的迅速发展,直接数字频率合成器(Direct Digital Frequency Synthesis简称DDS

2019-08-21 07:45:04

用DDS制作数控信号合成器

2016-11-04 21:52:02

EV-ADF41020EB1Z,用于ADF41020 PLL频率合成器评估板的评估板。评估用于锁相环(PLL)的ADF41020频率合成器。它包含ADF41020合成器,100 MHz TCXO,电源,USB接口和RF输出。板载有一个有源环路滤波器和一个13 GHz VCO

2019-02-28 07:23:02

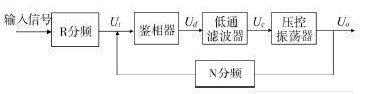

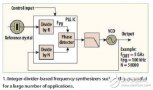

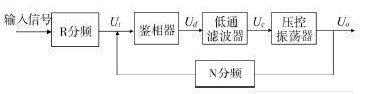

)可以极大地促进高性能架构的实现。大部分高频系统都使用传统的基于整数分频器的设计(图1)或基于分数N分频器的设计。不管是使用哪种设计,联合使用单个通用频率合成器IC和一个外部压控振荡器(VCO)通常都可以

2019-07-08 06:10:06

DDS9850的原理是什么?怎样去设计数字化可编程频率合成器?DDS与使用PLL技术实现的频率合成器相比,有哪些优势?

2021-04-20 07:30:07

AD9914 / PCBZ,评估板,采用AD9914,3.5 GSPS直接数字频率合成器,内置12位DAC。 AD9914是一款直接数字频率合成器(DDS),具有12位DAC。 AD9914采用先进的DDS技术,并配有内部高速,高性能DAC,可形成数字编程

2019-03-01 08:00:00

频率合成器的主要性能指标锁相环频率合成器原理锁相环频率合成器捕捉过程的分析与仿真

2021-04-22 06:27:35

AD9850 是AD I 公司采用先进的DDS 技术, 1996年推出的高集成度DDS 频率合成器, 它内部包括可编程DDS 系统、高性能DAC 及高速比较器, 能实现全数字编程控制的频率合成器和时钟

2008-04-10 13:14:29 83

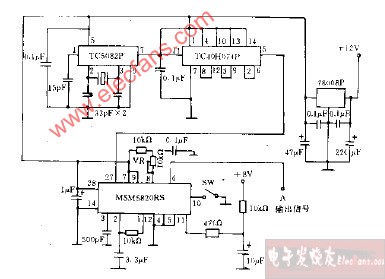

83 在介绍DDS 芯片STEL-1479 和PIC16C73A 单片机的基础上,设计了一种利用单片机控制DDS 芯片实现的中波频率合成器。进行了详细的硬件和软件设计,给出了具体的硬件电路及软件流程。

2009-09-03 09:16:06 17

17 本文讨论了DDS+PLL 结构频率合成器硬件电路设计中需要考虑的几方面问题并给出了设计原则,依此原则我们设计了一套短波波段频率合成器,实验结果证实了其可行性。

2009-09-07 16:07:29 34

34 直接数字合成(DDS)是近年发展起来的一种新型合成技术,有频率分辨率高,转换时间短,相位噪声低等特点,与锁相合成技术(PLL)配合,可以设计出频带宽、分辨率高的频率

2009-09-11 15:55:32 13

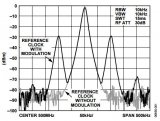

13 PLL频率合成器的噪声基底测量

在无线应用中,相位噪声是频率合成器的关键性能参数。像PHS、GSM和IS-54等相位调制蜂窝系统的RF系统设计均需要低噪声本地振荡(L

2010-04-07 15:25:21 22

22 直接数字合成(DDS)是近年发展起来的一种新型合成技术,有频率分辨率高,转换时间短,相位噪声低等特点,与锁相合成技术(PLL)配合,可以设计出频带宽、分辨率高的频率合

2010-08-04 15:57:03 0

0 应用FPGA,采用PLL频率合成技术,结合教学实验平台的需要,设计出了一个整数/半整数频率合成器,输出范围为1kHz~999.5kHz,步进频率可达到0.5kHz。与以前的教学实验装置相比,系统在性能指

2010-09-01 09:43:34 45

45 摘要:讨论了DDS的工作原理及性能性点,介绍了目前实现DDS常用的三种技术方案,并对各方案的特点作了简单的说明。 关键词:直接数字频率合成器 相位累加

2008-03-25 23:51:27 887

887

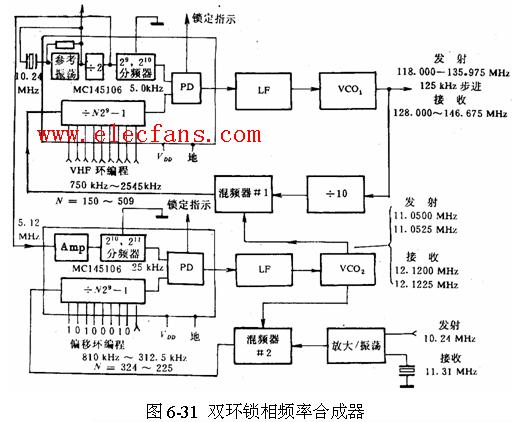

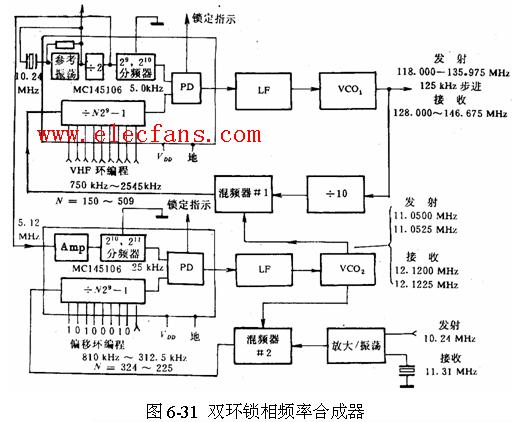

双环锁相频率合成器

2008-04-21 14:38:36 1088

1088

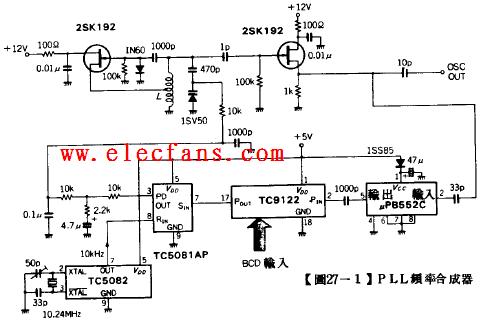

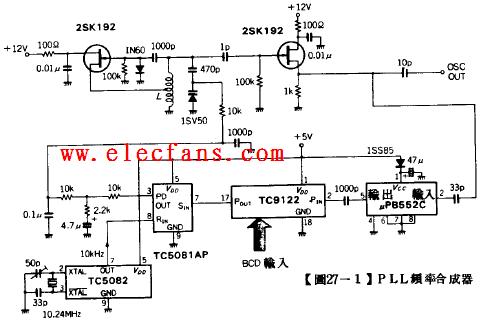

80M~120MHz频带PLL频率合成器图27-1为使用PLL IC TC9122(东芝)之80~120MHz的

2008-08-17 16:16:50 2106

2106

超高速频率合成器方案的设计与实现

综合考虑各个方案的优缺点,采用了一种DDS加倍频链的合成方法,研制了105 跳/s的宽带超高速频率

2009-03-01 17:20:21 1143

1143 对CDMA手机频率合成器的各关键部分进行分析,提出了设计方案。 关键词:CDMA手机,射频前端,频率合成器,相位噪声

2009-05-10 13:11:40 1253

1253

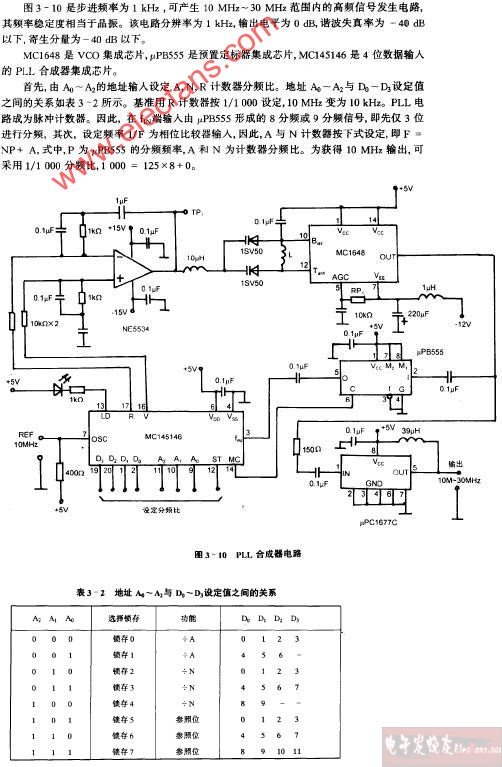

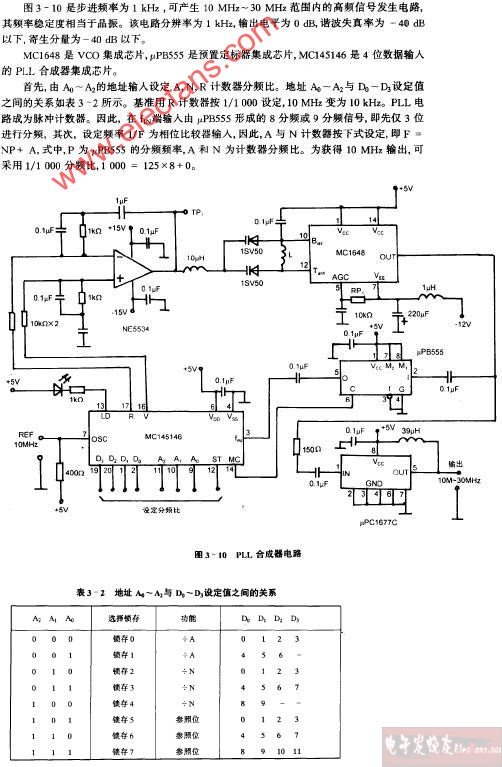

PLL合成器电路图

2009-07-14 17:08:22 439

439

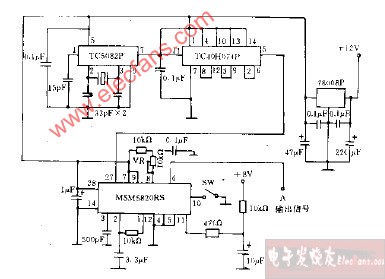

采用PLL的频率合成器电路图

2009-07-20 11:38:29 1118

1118

用AD9850激励的锁相环频率合成器

提出了一种DDS和PLL相结合的频率合成方案,介绍了DDS芯片AD9850的基本工作原理、性能特点及引脚功能,给出了以AD9850作

2009-12-08 15:27:31 1556

1556

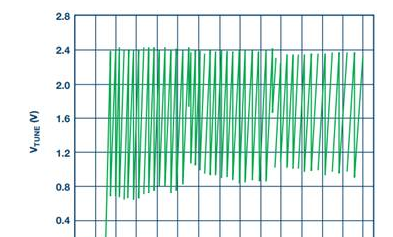

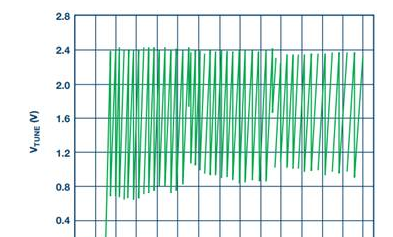

ADI推出的 ADF4158 PLL 合成器

ADI最新推出的 ADF4158 PLL 合成器,可灵活 、高性价比地实现 FMCW (频率调制连续波)雷达系统。FMCW 雷达系统广泛应用于汽车、航空、军事、工业

2010-01-13 11:38:55 1287

1287 频率合成器,频率合成器原理及作用是什么?

所谓的频率合成器,就是以一个精确度、稳定度极好的石英晶体振荡器作为基准频率,并利用加、减

2010-03-23 11:04:54 14601

14601 单环锁相频率合成器,单环锁相频率合成器是什么意思

频率合成的历史

频率合成器被人们喻为众多电子系统的“心脏”。现代战争是

2010-03-23 11:36:28 883

883 集成锁相环频率合成器,什么是集成锁相环频率合成器

频率合成的历史

频率合成器被人们喻为众多电子系统

2010-03-23 11:45:44 770

770 针对RF设计的新版PLL频率合成器设计软件

ADI全球领先的高性能信号处理解决方案供应商,和提供覆盖整个RF信号链的RF IC功能模块的全球领导者,最

2010-05-24 11:21:08 731

731 对体积、速度和省电的更进一步的要求推动了频率合成器技术的发展。目前频率合成器的一个明显趋势是集成了越来越多的微型锁相环(PLL)/压控振荡器(VCO)元件。过去在PCB上的多个元

2010-05-28 11:11:31 1858

1858 全球领先的高性能信号处理解决方案和 RF IC供应商,最近推出一款用于无线通信系统的 PLL(锁相环)频率合成器ADF4351。

2011-06-21 16:50:02 2278

2278 针对高性能DDS芯片AD9858设计宽带 频率合成器 , 分析DDS的工作原理,给出宽带频率合成器的原理框图和实现过程,并对软件控制流程进行了详细说明,结合理论对系统的相位噪声和杂散

2011-06-22 10:49:03 50

50 本文将介绍DDS和PLL的工作原理,并结合一电台(工作频率2 MHz~500 MHz)的设计,给出DDS做参考的PLL频率合成器的设计方案。

2011-07-18 09:38:02 3423

3423

杂散抑制是PLL 频率合成器的几个关键指标之一。在实际设计中,杂散的输出种类比较多,产生的原因也各不一样,但是它们中的大多数并不常见。首先从杂散的基本概念出发,详细地介绍了

2011-09-01 16:34:56 68

68 同步多个基于DDS的频率合成器AD9850

2011-11-29 16:03:42 56

56 随着微电子技术的迅速发展,直接数字频率合成器(Direct Digital Frequency Synthesis简称DDS或DDFS)得到了飞速的发展,它以有别于其它频率合成方法的优越性能和特点成为现代频率合成技术中

2012-03-30 11:38:22 2608

2608 摘 要:结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分辨率、低杂散、宽频段频率合成器,并对该频率合成器

2012-06-25 13:53:59 2540

2540

在非相参雷达测试系统中,频率合成技术是其中的关键技术.针对雷达测试系统的要求,介绍了一种用DDS激励PLL的X波段频率合成器的设计方案。文中给出了主要的硬件选择及具体电路设

2012-06-28 17:33:39 39

39 为了满足宽频段、细步进频率综合器的工程需求,对基于多环锁相的频率合成器进行了分析和研究。在对比传统单环锁相技术基础上,介绍了采用DDS+PLL多环技术实现宽带细步进频综,输

2013-04-27 16:26:51 48

48 △∑小数频率合成器中的小数分频器设计设计方案、技术指标、调试等。

2016-05-24 10:03:05 9

9 DDS-PLL组合跳频频率合成器,有需要的都可以看看。

2016-07-20 15:48:57 42

42 学习单片机电路图的很好的资料——DDS-PLL组合跳频频率合成器

2016-11-03 15:15:39 0

0 结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分 辨率、低杂散、宽频段频率合成器,并对该频率合成器进行了分析

2017-10-27 17:54:21 8

8 频率合成器是决定电子系统性能的关键设备,随着通信、数字电视、卫星定位、航空航天、雷达和电子对抗等技术的发展,对频率合成器提出了越来越高的要求。频率合成理论自20世纪30年代提出以来,已取得了迅速

2017-11-02 10:49:36 4

4 频率合成器是决定电子系统性能的关键设备,随着通信、数字电视、卫星定位、航空航天、雷达和电子对抗等技术的发展,对频率合成器提出了越来越高的要求。频率合成理论自20世纪30年代提出以来,已取得了迅速

2017-11-02 11:56:26 0

0 无线电系统会因为各种各样的原因而采用基于锁相环(PLL)技术的频率合成器。PLL 的好处包括: (1)易于集成到 IC 中。 (2)无线信道间隔中的灵活性。 (3)可获得高性能。 (4)频率合成器

2017-11-16 15:28:13 15

15 频率合成器主要有直接式、锁相式、直接数字式和混合式4种。目前,锁相式和数字式容易实现系列化、小型化、模块化和工程化,性能也越来越好,已逐步成为最为典型和广泛的应用频率合成器[1]。本文主要采用集成锁相环PLLphase-Lockde Loop芯片CD4046,运用FPGA来实现PLL频率合成器。

2019-01-07 09:52:00 3076

3076

PLL频率合成器和ADIsimFrequencyPlanner

2019-07-01 06:12:00 3764

3764 直接数据频率合成器(DDS)因能产生频率捷变且残留相位噪声性能卓越而著称。另外,多数用户都很清楚DDS输出频谱中存在的杂散噪声,比如相位截断杂散以及与相位-幅度转换过程相关的杂散等。此类杂散是实际DDS设计中的 有限相位和幅度分辨率造成的结果。

2019-11-14 17:10:08 5173

5173

几乎每个RF和微波系统都需要频率合成器。频率合成器产生本振信号以驱动混频器、调制器、解调器及其他许多RF和。频率合成器常被视为系统的心跳,创建方法之一是使用锁相环(PLL)频率合成器。传统

2020-10-15 10:43:00 8

8 利用频率合成器,你可以产生单一参考频率的各种不同倍数的输出频率。其主要应用是为RF信号 的上变频和下变频产生本振(LO)信号。频率合成器在锁相环(PLL)中工作,其中鉴频鉴相器(PFD)将反馈频率

2020-10-12 10:43:00 0

0 要满足苛刻的频率合成器要求,通常需要做到一定程度的设计灵活性。基本的锁相环(PLL)频率合成器能以低成本、高空间效率、低功耗封装提供合理的频谱纯度和频率捷变,因此它在射频(RF)系统核心位置发挥作用已经有段时间了。但是,在要求快速切换速度、低相位噪声或低杂散信号电平的场合,有必要使用更为复杂的架构。

2020-09-29 10:44:00 2

2 AN-605: 同步多个基于DDS的频率合成器AD9852

2021-03-19 09:08:03 0

0 UG-161:PLL频率合成器评估板

2021-03-20 09:54:34 6

6 AN-1254: 同步多个基于DDS的频率合成器AD9915

2021-03-20 19:59:38 2

2 ADF4107:PLL频率合成器数据表

2021-04-14 09:44:36 8

8 ADF4106:PLL频率合成器数据表

2021-04-29 08:52:36 12

12 ADF4108:PLL频率合成器数据表

2021-05-19 18:23:27 13

13 图1所示电路使用带集成式VCO和外部PLL的ADF4350频率合成器,通过隔离PLL频率合成器电路与VCO电路将杂散输出降至最低。集成PLL和VCO的器件可从数字PLL电路馈通至VCO,由于PLL

2021-05-28 17:50:57 7

7 直接数字频率合成技术(DDS+PLL)资料下载。

2021-06-07 14:41:54 38

38 结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分辨率、低杂散、宽频段频率合成器,并对该频率合成器进行了分析

2021-06-08 14:07:08 3049

3049

ADF4107 PLL频率合成器数据表

2021-06-18 10:01:57 7

7 pll频率合成器工作原理与pll频率合成器的原理图解释 我们要搞清楚pll频率合成器工作原理与pll频率合成器的原理图就要先搞清楚pll和频率合成器的概念。 频率合成器:将一个高稳定度和高精度的标准

2023-02-24 18:19:52 8262

8262

MAX2902 ISM发送器设计用于与外部频率合成器IC组合,形成完整的TX路径方案。根据系统要求,可以使用小数N分频或整数N分频频率合成器IC。了解两种频率合成器的通道步长、相位噪声和PLL锁定时间有何不同,对于确定哪种频率合成器更适合特定应用是必要的。本说明将尝试说明主要差异,以便正确选择合成器。

2023-03-03 15:22:43 429

429

电子发烧友网站提供《一种用DDS激励PLL的X波段频率合成器的设计方案.pdf》资料免费下载

2023-10-24 09:10:26 4

4

电子发烧友App

电子发烧友App

评论