本文章是接上期《锁相环中的相位噪声建模、仿真和传播(一)》的第二部

本文要点

该文章是关于频率合成器的设计和分析的,重点讨论了相位噪声和频率噪声的测量和分析方法。

文章介绍了PLL频率合成器的一般设计过程,包括选择电路配置、选择元件和开环传递函数的建立。

接下来的步骤包括模拟器和实际电路的搭建与测试,并对模型和实际性能进行比较和调整。

本文摘要

本篇文章是关于相位锁定环(PLL)频率合成器的设计和分析,重点讨论了相位噪声和频率噪声的测量、建模和仿真方法。文章以设计一个假想的PLL频率合成器为例,详细介绍了设计过程和步骤。从规格选择、电路配置到元件选择和相噪模型的建立,文章提供了一套完整的设计流程。通过建模和仿真,可以评估设计的性能并进行优化。最后,文章还介绍了如何根据模型和实测数据进行参数调整,以实现设计的要求和性能。

如第 一 部分所述,锁相环 (PLL) 在当今的高科技世界中无处不在。几乎所有商业和军用产品都在其运行中使用它们,并且相位(或 PM)噪声是一个主要问题。频率(或 FM)噪声密切相关(瞬时频率是相位的时间导数),通常被认为是在相位噪声的范畴内(也许两者都可能被视为“角度噪声”)。幅度(或 AM)噪声是另一个考虑因素。

虽然两者都会影响 PLL 性能,但幅度噪声通常是自限性的,不会产生任何后果。因此,PLL 输出和 RF 组件的相位噪声是主要问题。当然,输出相位噪声是最终关注的问题,并且很大程度上取决于每个组件的相位噪声。造成组件相位噪声的因素有很多,例如电源、EMI 和半导体异常等,了解这些因素使我们能够实施组件相位噪声的缓解策略,并最终实现输出相位噪声的缓解策略。

第 1 部分讨论了相位噪声的简要理论和典型测量及其分析(建模、仿真和传播),并展示了大多数计算机辅助设计 (CAD) 应用程序使用的方法。第 2 部分深入研究用于分析的假设 PLL 频率合成器的设计。

8 至 12 GHz 输出/50 MHz 步进 PLL 频率合成器的设计

为了演示第 1 部分中回顾的概念和方法,我们设计了一个假设的单环 8 至 12 GHz/50 MHz 步长(通道间隔)整数合成器,具有 25 MHz 参考(50 MHz 是可实现的最小步长,因为,展望未来,我们将使用固定模数除以 2 预分频器)。它将通过在 10 GHz 中频输出处实现最低相位噪声来设计,以实现整个频段内最低的平均输出相位噪声。我们遵循标准的设计程序:

1. 审查规格。

对于此示例,唯一的规范是如上所述的相位噪声(对于此示例明确的不切实际的过度简化)。

2. 选择电路配置、类型、顺序和环路滤波器拓扑。

离散(而不是 I2C 或混合)配置、类型 2、二阶和一阶有源 PI 环路滤波器(因其简单和流行而选择)。

3. 选择组件。

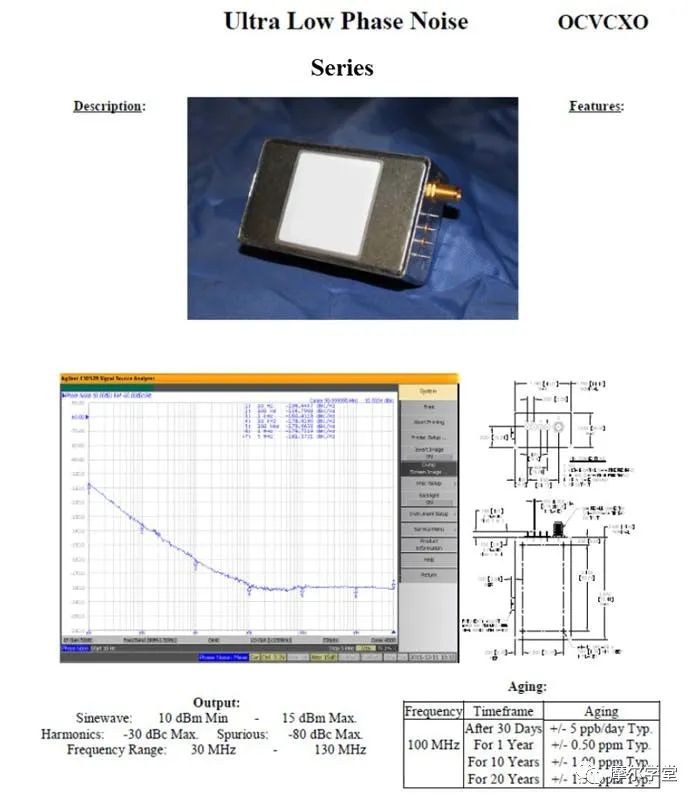

参考:著名电子制造商的 100 MHz OCVCXO (图 5 和 6

5. 制造商提供的 8 至 12 GHz 输出/50 MHz 步进 PLL 频率合成器的参考 (100 MHz OCVCXO) 数据表。

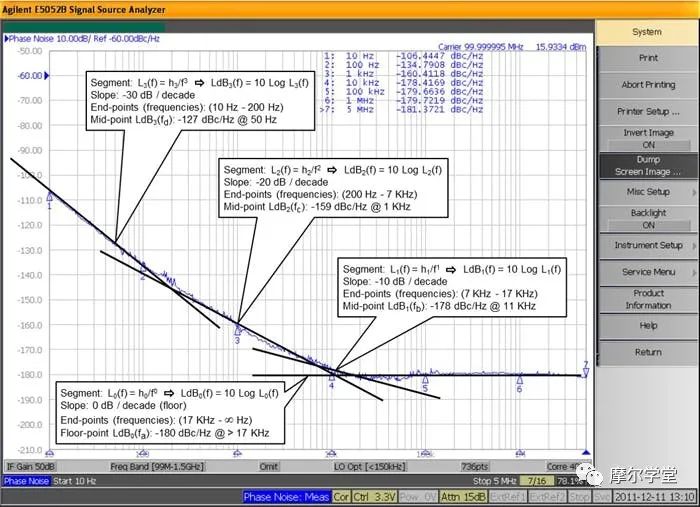

6. 参考 (100 MHz OCVCXO) 相位噪声图(图 5)与通用相位噪声模型(第 1 部分中的图 3)适合 8 至 12 GHz 输出/50 MHz 步进 PLL 频率合成器的图。

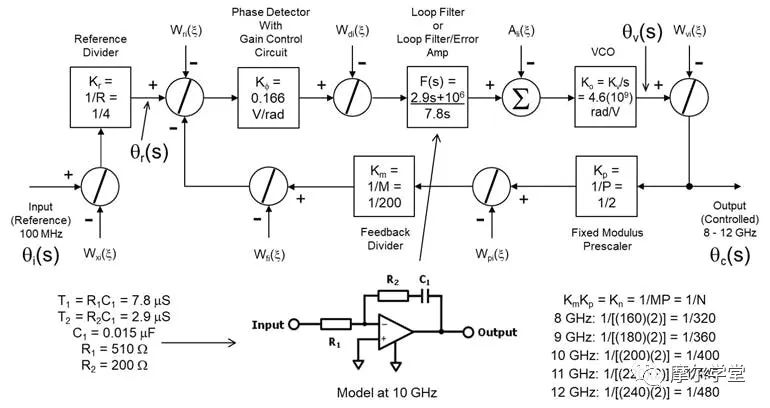

参考分频器:著名电子制造商的可编程整数分频器,范围 K r(= 1/R) = 1/1 至 1/17 (R = 1 至 17) 编程为:

在所有 GHz 下 R = 4。

反馈分频器:著名电子制造商的可编程整数/小数分频器,用于整数模式,范围 K m(= 1/M) = 1/32 至 1/1048575 (M = 32 至 1048575) 编程为:

8 GHz 时 M = 160

9 GHz 时 M = 180

10 GHz 时 M = 200

11 GHz 时 M = 220

12 GHz 时 M = 240

预分频器:著名电子制造商的固定模数除以 2 预分频器,K p(= 1/P) = 1/2 (P = 2) 给出总反馈因子 Kn(=1/N) = 1/MP (N =MP) 生产:

在所有 GHz 下 P = 2

N = MP = 320(8 GHz)

N = MP = 360(9 GHz)

N = MP = 400(10 GHz)

N = MP = 440(11 GHz)

12 GHz 时 N = MP = 480。

VCO:著名电子制造商的 8 至 12.5 GHz 低噪声 VCO 11,具有:

8 GHz 时Kv= 900 MHz/V [5.7(109) rad/S/V]

9 GHz 时Kv= 825 MHz/V [5.2(109) rad/S/V]

10 GHz 时Kv= 725 MHz/V [4.6(109) rad/S/V]

11 GHz 时Kv= 540 MHz/V [3.4(109) rad/S/V]

12 GHz 时Kv= 375 MHz/V [2.4(109) rad/S/V]

相位检测器:著名电子制造商的相位/频率检测器 (PFD),带有增益控制电路,可补偿整个 VCO 频段的Kv变化(保持 KψKv= 恒定),从而产生有效的:

Kφ= 0.134 V/rad(8 GHz)

9 GHz 时Kφ = 0.147 V/rad

10 GHz 时Kφ = 0.166 V/rad

11 GHz 时Kφ= 0.225 V/rad

12 GHz 时Kφ= 0.318 V/rad

环路滤波器/误差放大器:著名电子制造商的运算放大器(具有足够的增益、精度、噪声、带宽、稳定性、电源要求和输出电压/电流驱动能力)。

4. 开发射频组件的相位噪声模型。

我们使用相位噪声分析程序(第 1 部分)的步骤 1 至 6 来开发 RF 组件相位噪声模型并在图 7中对其进行仿真。我们展示了参考的完整开发过程,包括适合其数据表相位噪声图(图 5 和 6)的通用相位噪声模型(图 3,第 1 部分)以及其计算和生成的特定相位噪声模型。

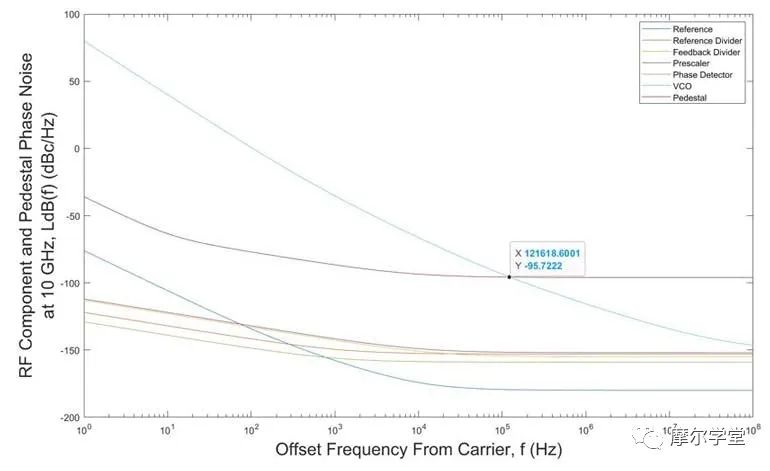

7. 10 GHz 中频输出处的 RF 分量和基座相位噪声显示了8 至 12 GHz 输出/50 MHz 步进 PLL 频率合成器的 VCO/基座交叉处的最佳环路带宽 fg 。

对于其他组件,为了简洁起见,我们仅显示它们的计算和由此产生的特定相位噪声模型(此外,为了简单起见,没有对环路滤波器/误差放大器进行建模,因为它不是射频组件,并且其分析比射频组件1):

A. 参考(100 MHz)

相位噪声模型点LdBj(fk),从将通用相位噪声模型拟合到数据表图:

地板段:0 dB/dec (17 kHz - ∞ Hz)

底点:LdB 0(fa) = −180(17 kHz) (dBc/Hz)

L0(fa) = 10LdB0/10= 10-18.0(17 kHz) (伏特比2/Hz)

闪烁段:−10 dB/dec (7 kHz - 17 kHz)

中点:LdB 1(fb) = −178(11 kHz) (dBc/Hz)

L1(fb) = 10LdB1/10= 10-17.8(11 kHz) (伏特比2/Hz)

闪烁段:−20 dB/dec (200 Hz - 7 kHz)

中点:LdB 2(fc) = −159(1 kHz) (dBc/Hz)

L2(fc) = 10LdB2/10= 10-15.9(1 kHz) (伏特比2/Hz)

闪烁段:−30 dB/dec (10 Hz - 200 Hz)

中点:LdB 3(fd) = −127(50 Hz) (dBc/Hz)

L3(fd) = 10LdB3/10= 10-12.7(50 Hz) (伏特比2/Hz)

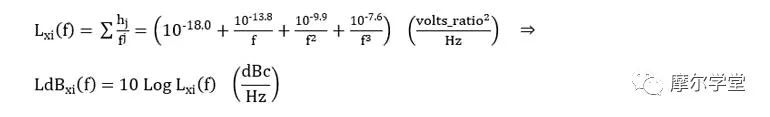

来自上述相位噪声模型点的相位噪声模型系数 hj :

h0= L0fa0= 10-18.0(伏特比2Hz-1)

h1= L1fb1= (10-17.8)[11(103)]1= 10-13.8(伏特比2)

h2= L2fc2= (10-15.9)(103)2= 10-9.9(伏特比2Hz)

h3= L3fd3= (10-12.7)[5(101)]3= 10-7.6(伏特比2Hz2)

相位噪声模型 LdBxi(f),根据上述系数:

模拟图 7中的LdBxi(f)。

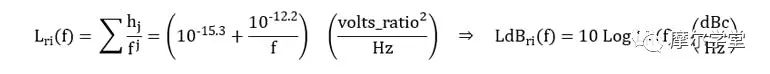

B. 参考分频器(与频率无关)

相位噪声模型点LdBj(fk),来自将通用相位噪声模型拟合到数据表图(未显示):

地板段:0 dB/dec (3 kHz - ∞ Hz)

底点:LdB 0(fa) = −153(3 kHz) (dBc/Hz)

L0(fa) = 10LdB0/10= 10-15.3(3 kHz) (伏特比2/Hz)

闪烁段:−10 dB/dec (100 Hz - 3 kHz)

中点:LdB 1(fb) = −150(600 Hz) (dBc/Hz)

L1(fb) = 10LdB1/10= 10-15.0(600 Hz) (伏特比2/Hz)

来自上述相位噪声模型点的相位噪声模型系数 hj :

h0= L0fa0= 10-15.3(伏特比2Hz-1)

h1= L1fb1= (10-15.0)[6(102)]1= 10-12.2(伏特比2)

相位噪声模型 LdBri(f),根据上述系数:

仿真图 7中的LdBri(f)。

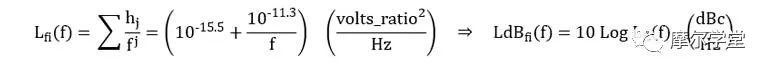

C. 反馈分频器(与频率无关)

相位噪声模型点LdBj(fk),来自将通用相位噪声模型拟合到数据表图(未显示):

地板段:0 dB/dec (10 kHz - ∞ Hz)

底点:LdB 0(fa) = −155(10 kHz) (dBc/Hz)

L0(fa) = 10LdB0/10= 10-15.5(10 kHz) (伏特比2/Hz)

闪烁段:-10 dB/dec (100 Hz - 10 kHz)

中点:LdB 1(fb) = −143(1 kHz) (dBc/Hz)

L1(fb) = 10LdB1/10= 10-14.3(1 kHz) (伏特比2/Hz)

来自上述相位噪声模型点的相位噪声模型系数 hj :

h0= L0fa0= 10-15.5(伏特比2Hz-1)

h1= L1fb1= (10-14.3)(103)1= 10-11.3(伏特比2)

相位噪声模型 LdBfi(f),根据上述系数:

模拟图 7 中的LdBfi (f)。

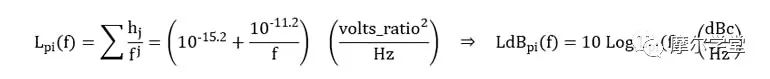

D. 预分频器(与频率无关)

相位噪声模型点LdBj(fk),来自将通用相位噪声模型拟合到数据表图(未显示):

地板段:0 dB/dec (10 kHz - ∞ Hz)

底点:LdB 0(fa) = −152(10 KHz) (dBc/Hz)

L0(fa) = 10LdB0/10= 10-15.2(10 kHz) (伏特比2/Hz)

闪烁段:−10 dB/dec (100 Hz - 10 kHz)

中点:LdB 1(fb) = −142(1 kHz) (dBc/Hz)

L1(fb) = 10LdB1/10= 10-14.2(1 kHz) (伏特比2/Hz)

来自上述相位噪声模型点的相位噪声模型系数 hj :

h0= L0fa0= 10-15.2(伏特比2Hz-1)

h1= L1fb1= (10-14.2)(103)1= 10-11.2(伏特比2)

相位噪声模型 LdBpi(f),根据上述系数

模拟图 7中的LdBpi(f)。

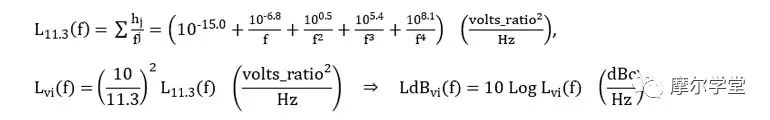

E. VCO(10 GHz 时从数据表中给出的 11.3 GHz 缩放)

相位噪声模型点LdBj(fk),来自将通用相位噪声模型拟合到 11.3 GHz 数据表图(未显示):

地板段:0 dB/dec (100 MHz - ∞ Hz)

底点:LdB 0(fa) = −150(100 MHz) (dBc/Hz)

L0(fa) = 10LdB0/10= 10-15.0(100 MHz) (伏特比2/Hz)

闪烁段:-10 dB/dec (10 MHz - 100 MHz)

中点:LdB 1(fb) = −143(30 MHz) (dBc/Hz)

L1(fb) = 10LdB1/10= 10-14.3(30 MHz) (伏特比2/Hz)

闪烁段:−20 dB/dec (40 kHz - 10 MHz)

中点:LdB 2(fc) = −111(600 kHz) (dBc/Hz)

L2(fc) = 10LdB2/10= 10-11.1(600 kHz) (伏特比2/Hz)

闪烁段:−30 dB/dec (1 kHz - 40 KHz)

中点:LdB 3(fd) = −59(6 kHz) (dBc/Hz)

L3(fd) = 10LdB3/10= 10-5.9(6 kHz) (伏特比2/Hz)

闪烁段:−40 dB/dec (100 Hz - 1 kHz)

中点:LdB 4(fe) = −18(300 Hz) (dBc/Hz)

L4(fe) = 10LdB4/10= 10-1.8(300 kHz) (伏特比2/Hz)

相位噪声模型系数 hj,来自上述 11.3 GHz 处的相位噪声模型点:

h0= L0fa0= 10-15.0(伏特比2Hz-1)

h1= L1fb1= (10-14.3)[3(107)]1= 10-6.8(伏特比2)

h2= L2fc2= (10-11.1)[6(105)]2= 100.5(伏特比2Hz)

h3= L3fd3= (10-5.9)[6(103)]3= 105.4(伏特比2Hz2)

h4= L4fe4= (10-1.8)[3(102)]4= 108.1(伏特比2Hz3)

相位噪声模型 LdBvi(f),来自上述系数 [数据表中给出的 11.3 GHz 时的 L11.3(f) 缩放至 10 GHz 时的 Lvi(f)]:

模拟图 7中的LdBvi(f)。

F. 鉴相器(25 MHz)

相位噪声模型点LdBj(fk),来自将通用相位噪声模型拟合到数据表图(未显示):

地板段:0 dB/dec (1 kHz - ∞ Hz)

底点:LdB 0(fa) = −159(1 kHz) (dBc/Hz)

L0(fa) = 10LdB0/10= 10-15.9(1 kHz) (伏特比2/Hz)

闪烁段:−10 dB/dec (100 Hz - 1 kHz)

中点:LdB 1(fb) = −154(300 Hz) (dBc/Hz)

L1(fb) = 10LdB1/10= 10-15.4(300 kHz) (伏特比2/Hz)

来自上述相位噪声模型点的相位噪声模型系数 hj :

h0= L0fa0= 10-15.9(伏特比2Hz-1)

h1= L1fb1= (10-15.4)[3(102)]1= 10-12.9(伏特比2)

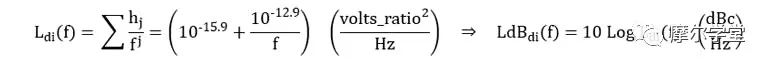

相位噪声模型 LdBdi(f),根据上述系数:

模拟图 7中的LdBdi(f)。

G. 环路滤波器/误差放大器(频率不适用)

如前所述,未建模,因为它不是具有固有相位噪声的射频组件。对其有效相位噪声进行建模以及计算影响输出相位噪声的传播动态,比射频组件更为复杂。1

5.通过在 10 GHz 中带输出处实现最低相位噪声,根据整个频段的最低平均输出相位噪声的唯一规范来确定环路带宽fg 。

环路最佳带宽 fg由 10 GHz 中带输出处的 VCO 和基座(参见下面的定义)相位噪声曲线的交点确定。

10 GHz 时的 VCO 相位噪声模型,LdBvi(f),曲线如前述第 4 节 E 部分所示。

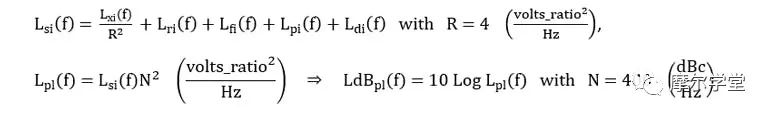

10 GHz 处的基准相位噪声模型、LdBpl(f) 和曲线,其中基准定义为所有 RF 组件(VCO 除外)相位噪声模型 Lsi(f) 乘以输出的总和传递函数(稍后讨论)直流增益平方,N2:

仿真图 7中的LdBpl(f)。

然后通过数学或图形方式确定环路带宽,结果为 fg= 121.6 kHz。

6. 确定标准参数fn和z。

我们根据经验法则 fn= fg / 1.55 确定 fn,其中 ze = 0.707(参考文献 2),并根据其他规格确定 ze(未给出其他规格,因此保留 ze = 0.707 作为默认值)。这些被发现是:

fn =78.5kHz

ρ = 0.707

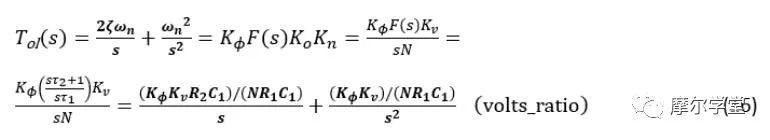

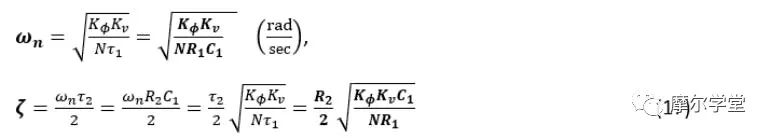

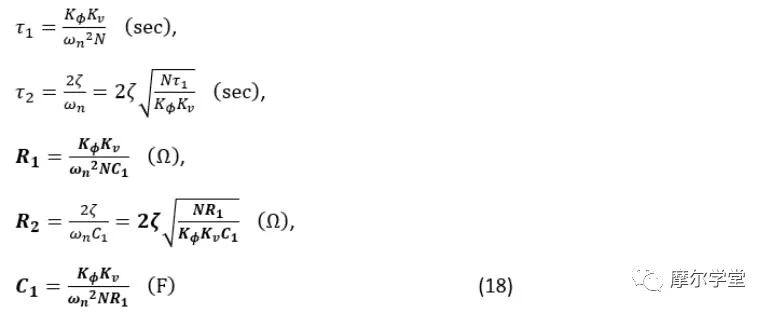

7. 将开环传递函数Tol的二阶形式(粗体)等同于电路常数形式(粗体),从而根据电路常数R1、R2和C给出标准参数fn和ze1.

(转换为ωn= 2πfn)

这给出了所需的关系(粗体):

8. 确定电路常数 R1、R2和C1(粗体)作为标准参数fn和δ对于 10 GHz 中频输出 (N= 400) 并计算任何其他感兴趣的量;将理论值修改为最接近的 EIA 5% 标准值。

(转换回fn=ωn/2π)。

注意,R1、R2和C1不是唯一确定的,因此必须绝对选择其中之一,通常是C1。对于这种情况,选择C1,然后计算R1和R2(均适用于谐振频率fn= 78.5 kHz 和阻尼系数z= 0.707),其中选择C1是为了保持R1和R2相对较低。因此,电阻噪声相对于误差放大器(运算放大器)噪声来说是微不足道的,并且在实际限制内:12,13

C1= 0.015 µF(已经是标准值的 5%)

R1= 522.9Ω(5%标准值为510Ω)

R2= 191.1Ω(5%标准值为200Ω)

使用这些标准值,通过将通用PLL 框图和相位噪声传播模型(图 4,第 1 部分)应用于我们的具体案例,形成特定 PLL 框图和相位噪声传播模型,完成设计并配置系统示例 PLL 的 10 GHz 中频输出(图 8)。14

8. 8 至 12 GHz 输出/50 MHz 步进 PLL 频率合成器的 10 GHz 中频输出下的特定 PLL 框图和相位噪声传播模型。

9. 对 PLL 开环/闭环动态和输出相位噪声进行建模,并使用适当的建模/仿真工具来仿真性能。

根据需要调整模型理论(标准值)电路常数和开环增益,以使仿真和计算的环路动态之间最接近,以及由于计算和仿真性能之间的差异而导致的输出相位噪声。

10. 构建并测试 EDM 单元。

使用调整后的电路常数构建并测试 EDM 单元。由于模拟和 EDM 性能之间存在差异,请根据需要进一步调整 EDM 电路常数,以获得适当的性能。

11. 根据模型和 EDM 单元之间的协议需要调整模型开环增益。

因此,使用步骤 8 中确定的理论(标准值)电路常数完成了设计。然后将根据步骤 9、10 和 11 细化这些值,但由于我们不是为我们的示例构建 EDM,理论值完成了设计。

审核编辑:汤梓红

-

锁相环

+关注

关注

36文章

637浏览量

91300 -

频率合成器

+关注

关注

5文章

368浏览量

33879 -

仿真

+关注

关注

55文章

4535浏览量

138664 -

pll

+关注

关注

6文章

990浏览量

138378 -

相位噪声

+关注

关注

2文章

198浏览量

23806

原文标题:锁相环中的相位噪声建模、仿真和传播(二)

文章出处:【微信号:moorexuetang,微信公众号:摩尔学堂】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于DDS驱动PLL结构的宽带频率合成器的设计与实现

CN0369 低相位噪声的转换锁相环频率合成器

关于相位锁定环(PLL)频率合成器的设计和分析

关于相位锁定环(PLL)频率合成器的设计和分析

评论