同步电路设计中静态时序分析的时序约束和时序路径

同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最坏情况下满足时序要求,我们需要进行静态时序分析,即不依赖于测试向量和动态仿真,而只根据每个逻辑门的最大延迟来检查所有可能的时序违规路径。

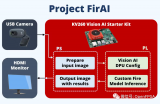

基于FPGA 的AI火灾侦查定位解决方案

解决方案包括建立一个分布式计算机视觉系统,增加建筑物火灾的早期检测。该系统的分布式和模块化特性可以轻松部署,而无需增加更多基础设施。在

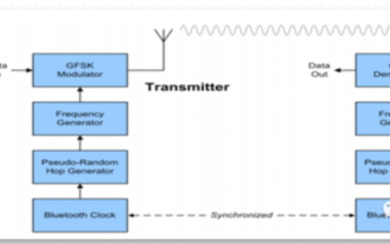

基于FPGA的音乐蜂鸣器设计案例解析

蜂鸣器是一种一体化结构的电子讯响器,采用直流电压供电,广泛应用于计算机、打印机、复印机、报警器、电子玩具、汽车电子设备、电话机、定时器等电子产品中作发声器件。

FPGA设计如何提高同步系统中的工作时钟

在FPGA设计的同一个模块中常常是包含组合逻辑与时序逻辑,为了保证在这些逻辑的接口处数据能稳定的被处理,那么对建立时间与保持时间建立清晰的概念非常重要。

基于FPGA的PCIE应用架构设计分析(2)

通过AXI_Lite接口来配置Bram,通过这个ram来与PC机进行一定的数据交互,解决图像断帧的现象

基于FPGA的PCIE应用架构设计分析(1)

PCIe总线作为处理器系统的局部总线,其作用与PCI总线类似,主要目的是为了连接处理器系统中的外部设备,当然PCIe总线也可以连接其他处理器系统。

以太网网口与FPGA连接的常用方案

随着技术的发展和各类应用的需求,出现了各种以太网的标准,包括标准以太网(10Mbit/s)、百兆以太网(100Mbit/s)、千兆以太网(1000Mbit/s)和10G(10Gbit/s)以太网[1]。不同类型的以太网有其各自需要遵循的标准,同时其所用的传输介质以及数据吞吐量也各不相同。

基于亿海神针系列FPGA应用案例

光纤传输系统由PDH发展到SDH,再到后来的WDM系统,从最初的单波长通道发展到多波长通道,光纤通信系统的传输容量在不断提高,光纤传输系统未来会继续沿着超高速、超大容量、超长距离传输的方向发展。

基于FGPA底层的RAM基块大小

不同的用户可能需要不同容量的RAM来构建他们的特定应用。所以FGPA底层的RAM基块大小就是一个有意思的话题。

如何在可编程逻辑中实现 MCU 内核设计

六级流水线 NIOS 内核可以用少至 600 个逻辑元件和特征向量中断控制、紧密的内存和 DSP 耦合以及添加自定义指令(最多 256 个)的能力来实现。它可以使用内存管理单元 (MMU),并支持开源和商业支持版本的嵌入式 Linux。

FPGA 应用的电源模块的选择

FPGA的电源 通常包括开关稳压器和线性稳压器的组合,以合理的效率提供不同的电压和稳定的电源。设计这样的电源并非易事,但通过将电路基于将多个开关和线性稳压器集成到单个芯片中的电源模块,事情可以变得更加简单。

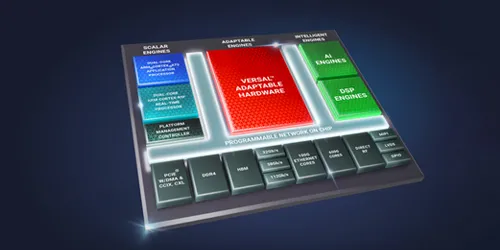

异构平台设计方法 探索赛灵思Versal ACAP设计方法论

身处智能时代,科技发展日新月异,伴随数据中心、有线网络、5G 无线和汽车等愈加丰富的场景,相应的技术与功能也正经历飞速迭代,因此,单一计算架构已难以应对海量数据处理需求,赛灵思 Versal ACAP多核异构计算平台致力于帮助所有开发者保持即时的灵活应变能力。

如何在Vitis中把设置信息传递到底层的Vivado

在Vitis完成这个过程的底层,实际调用的是Vivado。Vitis会指定默认的Vivado策略来执行综合和实现的步骤。当默认的Vivado策略无法达到预期的时序要求时,我们需要在Vivado中分析时序问题的原因, 并根据时序失败的原因调整Vivado各个步骤的选项。有时我们也需要调整Vivado各个步骤的选项做不同方向的优化。

对IP设计中注意事项及FPGA原型设计进行说明

如果我们试图将环形连接可视化,那么在高层次上,我们可以考虑使用这种类型的FPGA内部连接的引脚连接。IO的浪费不能局限在这种连通性上。FPGA处于下端;IO会被浪费掉,而且对于电路板设计师和电路板布局团队来说,将这些IO连接到高阻抗状态是额外的开销。

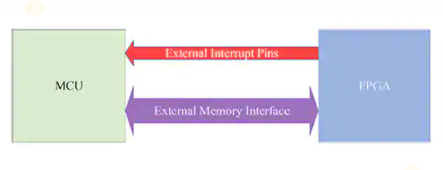

结合MCU 和FPGA 技术的协处理器硬件架构技术分析

从基于 C 语言的实现开始,DCT 算法接受两个 16 位数的数组;数组 “a” 是 DCT 的输入数组,数组 “b” 是 DCT 的输出数组。

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |