完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W原则。...

直角走线的对信号的影响就是主要体现在三个方面:一是拐角可以等效为传输线上的容性负载,减缓上升时间;二是阻抗不连续会造成信号的反射;三是直角尖端产生的EMI,到10GHz以上的RF设计领域,这些小小的直角都可能成为高速问题的重点对象。...

在对一块完好的PCB电路板进行原理图的逆向设计时,合理划分功能区域能够帮工程师减少一些不必要的麻烦,提高绘制的效率。一般而言,一块PCB板上功能相同的元器件会集中布置,以功能划分区域可以在反推原理图时有方便准确的依据。...

电流流过阻抗最小路径的概念是不正确的。电流在全部不同阻抗路径的多少与其电导率成比例。在一个地平面,常常有不止一个大比例地电流流经的低阻抗路径:一个路径直接连至旁路电容;另一个在达到旁路电容前,对输入电阻形成激励。图1示意了这两个路径。地回流电流才是真正引发问题的原因。...

在PCB板设计时,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。以下是一些常见的防范措施。...

高频电路往往集成度较高,布线密度大,采用多层板既是布线所必须,也是降低干扰的有效手段。在PCB Layout阶段,合理的选择一定层数的印制板尺寸,能充分利用中间层来设置屏蔽,更好地实现就近接地,并有效地降低寄生电感和缩短信号的传输长度,同时还能大幅度地降低信号的交叉干扰等,所有这些方法都对高频电路的...

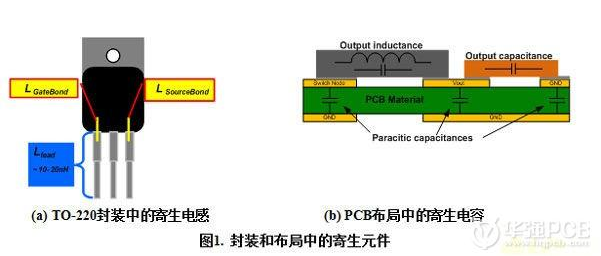

为驱动快速开关超级结MOSFET,必须了解封装和PCB布局寄生效应对开关性能的影响,以及为使用超级结所做的PCB布局调整。主要使用击穿电压为500-600V的超级结MOSFET。在这些电压额定值中,工业标准TO-220、TO-247、TO-3P和TO-263是应用最广泛的封装。封装对性能的影响有限,...

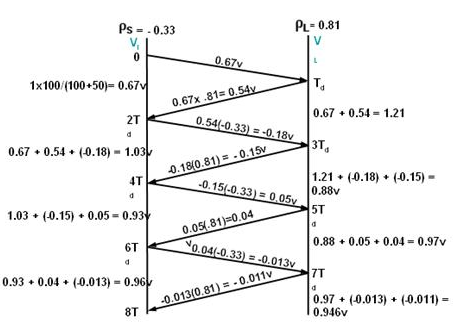

在高速电路中,信号的传输如上图所示,如果一根走线没有被正确终结(终端匹配),那么来自于驱动端的信号脉冲在接收端被反射,从而引发不可预期效应,使信号轮廓失真。当失真变形非常显著时可导致多种错误,引起设计失败。同时,失真变形的信号对噪声的敏感性增加了,也会引起设计失败。如果上述情况没有被足够考虑,EMI...

在核芯结构中,PCB板中的所有导电层敷在核芯材料上;而在敷箔结构中,只有PCB板内部导电层才敷在核芯材料上,外导电层用敷箔介质板。所有的导电层通过介质利用多层层压工艺粘合在一起。...

智能时代的到来,不仅给普通人的生活带来了便利,也对各行业产生了深刻的影响。为了使得PCB有高可靠性,必然要对PCB抄板、设计提出更高的要求。例如智能化产品对器件品质的要求、对密度散热的要求、对无处不在的物联网通信的要求,而智能化生产对柔性设备的要求、对智能机械的要求、对复杂环境的要求等等。...

最有效的电路板堆叠方法是将主接地面(主地)安排在表层下的第二层,并尽可能将RF线走在表层上。将RF路径上的过孔尺寸减到最小不仅可以减少路径电感,而且还可以减少主地上的虚焊点,并可减少RF能量泄漏到层叠板内其他区域的机会。在物理空间上,像多级放大器这样的线性电路通常足以将多个RF区之间相互隔离开来,但...

在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。以下是一些常见的防范措施。...

在元器件的布局方面,应该把相互有关的元件尽量放得靠近一些,例如,时钟发生器、晶振、CPU的时钟输入端都易产生噪声,在放置的时候应把它们靠近些。对于那些易产生噪声的器件、小电流电路、大电流电路开关电路等,应尽量使其远离单片机的逻辑控制电路和存储电路(ROM、RAM),如果可能的话,可以将这些电路另外制...

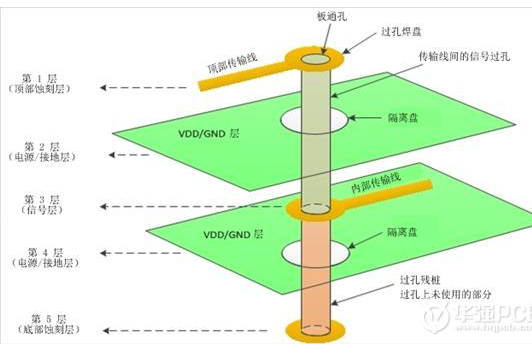

过孔是镀在电路板顶层与底层之间的通孔外的金属圆柱体。信号过孔连接不同层上的传输线。过孔残桩是过孔上未使用的部分。过孔焊盘是圆环状垫片,它们将过孔连接至顶部或内部传输线。隔离盘是每个电源或接地层内的环形空隙,以防止到电源和接地层的短路。...

无论是在制造组装流程还是在实际使用中,PCB都要具有可靠的性能,这一点至关重要。除相关成本外,组装过程中的缺陷可能会由PCB带进最终产品,在实际使用过程中可能会发生故障,导致索赔。因此,从这一点来看,可以毫不为过地说,一块优质PCB的成本是可以忽略不计的。在所有细分市场,特别是生产关键应用领域的产品...

1、如果设计的电路系统中包含FPGA器件,则在绘制原理图前必需使用Quartus II软件对管脚分配进行验证。(FPGA中某些特殊的管脚是不能用作普通IO的)。 2、4层板从上到下依次为:信号平面层、地、电源、信号平面层;6层板从上到下依次为:信号平面层、地、信号内电层、信号内电层、电源、信号...

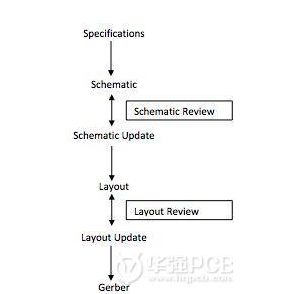

前面三个步骤花的时间最多,因为原理图检查是一个手工过程。想像一个具有1000条甚至更多连线的SoC电路板。人工检查每一根连线是冗长乏味的一项任务。事实上,检查每根连线几乎是不可能的,因而会导致最终电路板出问题,比如错误的连线、悬浮节点等。...

一、资料输入阶段 1.在流程上接收到的资料是否齐全 2.确认PCB模板是最新的 3. 确认模板的定位器件位置无误 4.PCB设计说明以及PCB设计或更改要求、标准化要求说明是否明确 5.确认外形图上的禁止布放器件和布线区已在PCB模板上体现 6.比较外形图,确认P...

PCB布局规则: 1、在通常情况下,所有的元件均应布置在电路板的同一面上,只有顶层元件过密时,才能将一些高度有限并且发热量小的器件,如贴片电阻、贴片电容、贴片IC等放在低层。 2、在保证电气性能的前提下,元件应放置在栅格上且相互平行或垂直排列,以求整齐、美观,在一般情况下不允许元件重叠;...

PageUp:以鼠标为中心放大 PageDown:以鼠标为中心缩小。 Home:将鼠标所指的位置居中 End:刷新(重画) *:顶层与底层之间层的切换 +(-)逐层切换:“+”与“-”的方向相反 Qmm(毫米)与mil(密尔)的单位切换 IM:测量两点间的距...