在FPGA系统设计中,要达到性能最大化需要平衡具有混合性能效率的元器件,包括逻辑构造(fabric)、片上存储器、DSP 和I/O带宽。在本文中,我将向你解释怎样能在追求更高系统级性能的过程中受益于Xilinx® 的Virtex™-5 FPGA构建模块,特别是新的ExpressFabric™技术。以针对逻辑和算术功能的量化预期性能改进为例,我将探究ExpressFabric架构的主要功能。基于实际客户设计的基准将说明Virtex-5 ExpressFabric技术性能平均比前一代Virtex-4 FPGA要高30%。

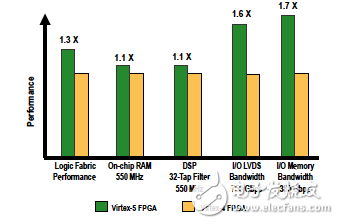

利用新的逻辑构造(在里面你可以实现诸如计数器、累加器和RAM/ROM存储)和可用的硬IP模块、存储器DSP(经最优化以运行在高达550MHz的时钟速率),Virtex-5 FPGA无疑是针对高性能设计的平台选择。

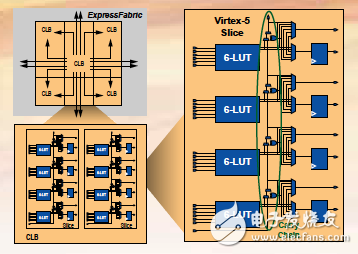

ExpressFabric的性能自从上世纪80年代中期第一颗FPGA问世以来,大多数FPGA的逻辑构造一直是基于相同的基本四输入查找表(LUT)架构。Virtex-5系列是第一个提供完全独立输入(不共享)的真正6输入LUT(6-LUT)构造的FPGA 平台(图1)。向6-LUT 构造架构转移为65nm 的Virtex-5 FPGA 系列提供了在关键路径延迟—决定逻辑构造性能的因素—与裸片面积之间的最有效折衷。

图1 - Virtex-5可配置逻辑模块(CLB)构成两个逻辑片,每逻辑片利用4 个提供更少逻辑级好处的独立6 -LUT。

随着工艺技术的进步,互连时间延迟能占关键路径延迟的50%以上。Xilinx已经为Virtex-5 FPGA开发了新的互连模式,通过较少的跳跃(hops)到达更多的地方来增强性能。新的模式增加了两到三跳之内可以到达的逻辑互连的数量。此外,更为有序的路由模式使 Xilinx ISE™软件更容易找到最优化的路由。所有互连功能对FPGA设计工程师都是透明的,但是,将转变为更高的整体性能和更容易设计的可路由性。本质上,Virtex-5模式根据距离提供快速可预测的路由。

通过把新的6-LUT构造与进位链、专用多路选择器和触发器(与把这些单元连接起来的独特方法)这样的特殊功能相结

合,创造了非常卓越的性能和实现逻辑及算术功能的效率。

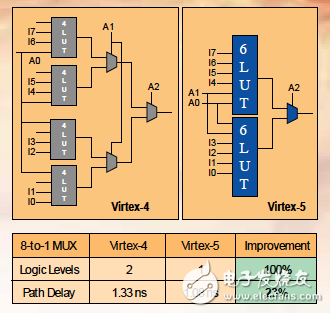

多路选择器(MUX)就是清楚地说明ExpressFabric技术好处的例子之一。在Virtex-4架构中实现一个4:1 MUX需要两

个4 输入LUT和一个MUXF模块;同样的4:1 MUX 现在可以在Virtex-5 器件中用一个LUT 来实现。类似地,在Virtex-4 架构中实现一个8:1 MUX 需要四个LUT和三个MUXF 模块;而新的Virtex-5 架构仅仅需要两个6-LUT,因此,性能更高且逻辑利用更佳,如图2所示。

图2 - Virtex-5 FPGA 与Virtex-4 FPGA在8:1多路选择器实现上的比较。

与过去的Xilinx FPGA系列一样,Virtex-5 Slice L(逻辑片)利用专用的进位链可以实现逻辑功能、寄存器和算术功能。

稍微更复杂的Slice M(存储器片)提高了在LUT(SRL)内部实现分布式RAM及移位寄存器的性能。

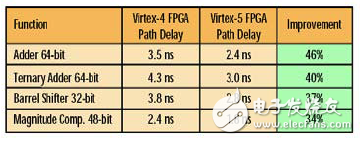

由ExpressFabric 架构所提供的各种各样改进当中,新的进位链结构当被用于实现算术运算时实质上产生了更高的性

能,其对关键路径延迟的影响可以在表1中的若干例子容易地看到。

表1 Virtex-5 FPGA与Virtex-4 FPGA在实现算术功能上的比较。

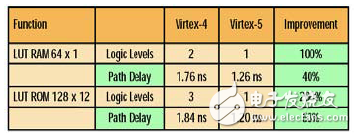

分布式存储器功能如LUT RAM或ROM也以若干方式从较大的LUT构造获益。新的宽高比容许更为密集地包装小的存储器功能,从而引向重大的性能好处,如表2所描述。

表 2 Virtex-5 FPGA与Virtex-4 FPGA在实现基于LUT的RAM/ROM上的比较。

由已改进的具有6-LUT架构的逻辑构造和互连结构所提高的性能是有重大价值的,但是,这仅仅是开端。

大多应用需要的片上RAM 比基于LUT的RAM能提供的要多。利用增强的Virtex-5模块RAM,你可以实现更高的片上存储器性能。

模块RAM性能

随着向65nm的转移,Virtex-5模块RAM的时钟速度获得了10%的提升,达到550MHz。然而,为了实现目前大多应用

所渴望的性能,模块RAM需要的不仅仅是速度更快,而是需要规模更大。

Virtex-5模块RAM的规模已经加倍到36 kb。这个较大的模块规模(由两个18kb存储器构成)在简单的双口模式中将支持72位数据字,因此,把模块RAM的带宽提高了一倍。此外,Virtex-5 FPGA提供专用的连接,使你能够在模块RAM行

中把两个相邻的36kb 模块RAM级联起来,因此,实现一个运行在最大550MHz速率的72kb存储器。

不断加大的FPGA的实用性已经加速了把更多子系统集成到单一器件之中的趋势,使得对多个时钟域进行接口的必要性

更为普遍。Virtex-5器件通过提供集成逻辑来简化灵活和有效的FIFO的实现来适应这种趋势。

通过这种增强的组合,Virtex-5模块RAM提供更多片上存储器,更容易构建FIFO,并获得更高的带宽。

DSP性能

作为一种针对高性能DSP应用的可行解决方案,FPGA的认知度日益增加是理所当然的。无论作为一种协处理器或一种针对更为苛刻应用要求的单机解决方案,FPGA都不断提供最佳的性能、功率和成本组合。

为了满足对更高DSP性能看来贪得无厌的需求,Xilinx的Virtex-5 DSP性能在时钟速率和精度两个方面都居于领先地位;时钟速率已经提高到550MHz,而精度已经从18 x 18位提高到25 x 18位。

Xilinx也针对累计器链实现而优化了Virtex-5 DSP48片,其强大的性能使创建非常有效的高性能滤波器成为可能。在每

一个DSP48片输入和输出上的专用路由资源允许在一行内把任意数量的片链接起来。这种专用的路由确保在链中的每一个DSP48片将以全速运行而不消耗任何构造路由或逻辑资源,因为其它FPGA需要。

综合起来看,这些改进把实现通用高精度功能所需要的资源数量减少了一半。例如,对于35 x 25 位乘法,采用Virtex-4 FPGA就需要四个DSP48片;在Virtex-5 FPGA中具有更宽的DSP模块可用,实现这种乘法功能只要采用一半的DSP48片。

I/O 带宽性能

随着性能基准的进展,FPGA能处理数据的速度与器件I/O带宽的前后使用情况有关,它就是大量数据能被搬移到器件上及从器件上卸下所用的速度。当利用外部存储缓冲器时,接口必须比数据处理率至少快两倍,因为数据既要写出也要读回FPGA之中。

通过既提高每一个引脚的数据率,又利用更大的封装来增加可用I/O的数量,Virtex-5 FPGA提高了Virtex-4的带宽。例

如, 对于流行的存储器接口如DDR2 SDRAM,每一个引脚的带宽已经从534 Mbps提高到了667 Mbps;数据I/O的数

量—当考虑SSO要求时—已经从32 增加到了576。

客户设计基准

为了进一步评估由Virtex-5 FPGA逻辑构造所提供的性能改进,我们利用Xilinx的ISE软件实现了一组客户设计。

这些设计完全采用VHDL或Verilog编写。我们利用库组件或综合参考的直接调用方法实现了一些像存储器和FIFO那样的特殊设计单元,但是许多是利用由CORE Generator™软件生成的EDIF模块实现的。

对于这些基准,我们采用Synplicity公司的Synplify Pro工具以时序驱动方式执行综合,并利用严紧和现实的约束来有

效地测量性能。完成这一点就确保所有特殊优化和逻辑复制获得了使用。在ISE 软件中的实现是把布局和路由努力设置到“high”来完成的。时钟被以5%的增量反复增加,直到该设计不能满足设计约束。

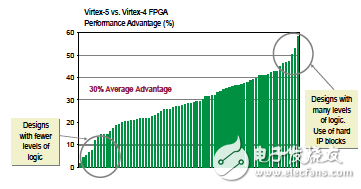

结果是 - 与利用Virtex-4 FPGA实现的设计相比 - 平均性能提高了30%,如图3所示。

图 3 - 根据利用ISE 8.2i 软件实现的一套74个客户设计的比较。

这些改进最多的设计具备大的逻辑锥体;关键路径常常实现大的复杂逻辑等式。

例如,ASIC原型设计的关键路径中的大量逻辑通常将具有非常少的寄存器。这些类型的设计展示了采用Virtex-5 ExpressFabric技术的重大改进。在展示适度改进的设计中,要么具有较少的逻辑级,要么为使用硬IP 模块或改进性能的进位链结构提供很少的机会。

图4通过把Virtex-5 FPGA对前一代Virtex-4 FPGA的性能改进进行分类做了总结。

图4 - Virtex-5 FPGA 性能的改进。

结论

利用其新的ExpressFabric技术和对其它高性能硬IP及I/O的紧密耦合,与前一代架构相比,Virtex-5 FPGA系列表现了重大的性能提升。

电子发烧友App

电子发烧友App

评论