在特定条件下采用更智能的技术来隔离特定错误,找到问题电路的源头并渐进式修复错误,这很重要。Synopsys 公司的Synplify Premier 和Synplify Pro FPGA设计工具以及Identify RTLDebugger 等产品能帮助设计人员完成上述工作。

2013-08-15 09:59:30 3156

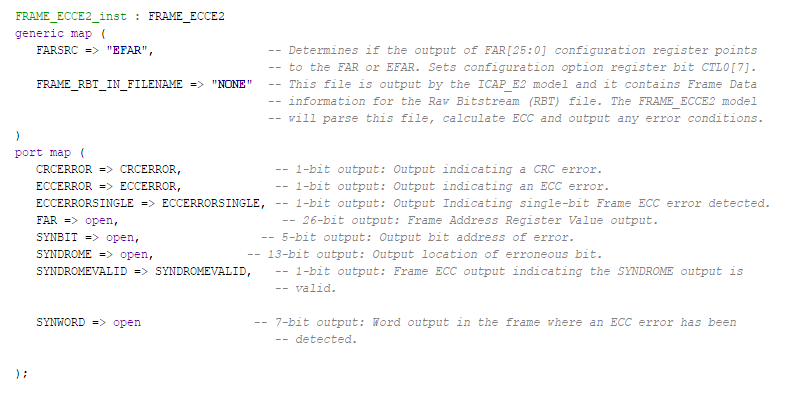

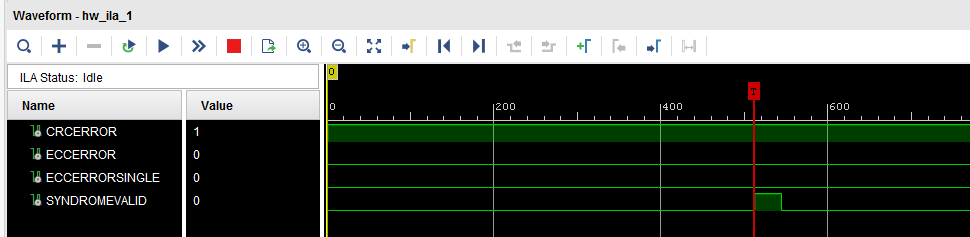

3156 7 系列 FPGA 帧 ECC 逻辑可检查配置帧数据的单位或双位错误。它可使用基于帧数据( BitGen 生成)计算的 13 位汉明码校验值

2017-09-28 06:04:00 8412

8412 在压缩视频流中,每个比特都是非常重要的,在传输过程中发生的错误会严重影响解码后的视频效果。所以,在所接收的视频流中进行错误检测在实际工作中是非常重要的。只有解码器在所接收的比特流中检测到误码,才能采用相应的策略对它进行错误恢复和错误隐藏,因此,选择一种行之有效的误码检测方法是致关重要的。

2020-07-23 14:51:16 905

905

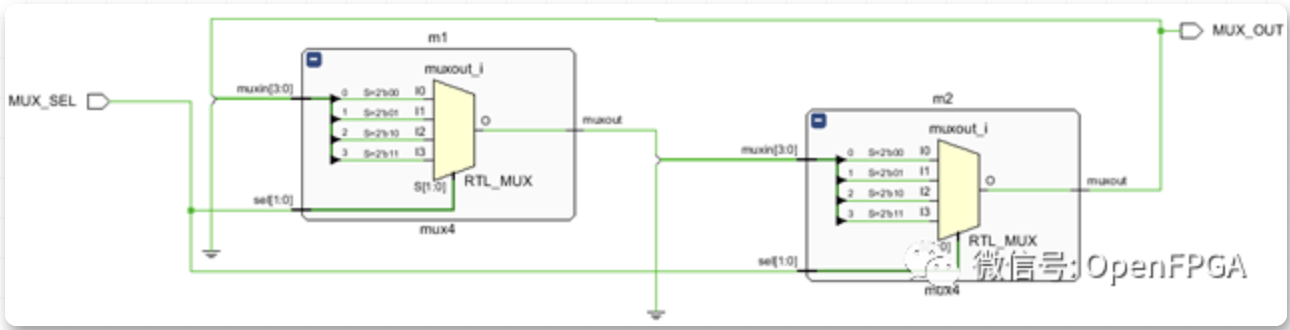

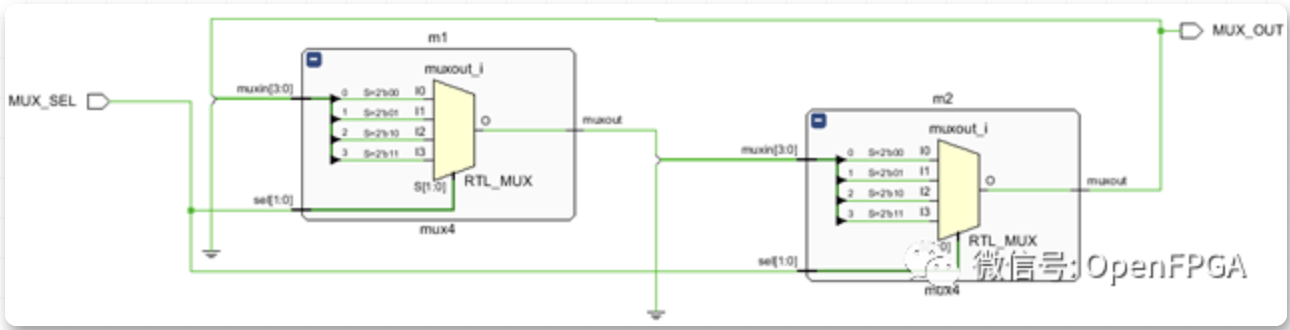

本文列出了FPGA设计中常见的十个错误。我们收集了 FPGA 工程师在其设计中犯的 10 个最常见错误,并提供了解决方案的建议和替代方案。本文假定读者已经具备 RTL 设计和数字电路方面的基础。接下来让我们深入探讨在FPGA 设计中要避免的 10 大错误。

2023-05-31 15:57:28 1607

1607

本文列出了FPGA设计中常见的十个错误。我们收集了 FPGA 工程师在其设计中犯的 10 个最常见错误,并提供了解决方案的建议和替代方案。

2023-06-01 17:28:57 1828

1828

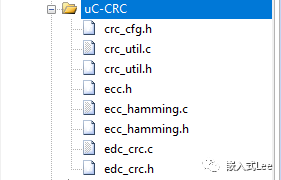

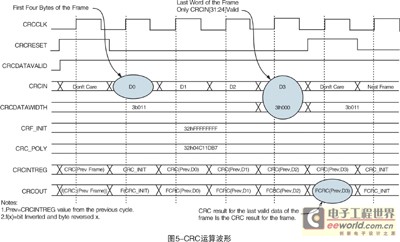

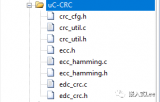

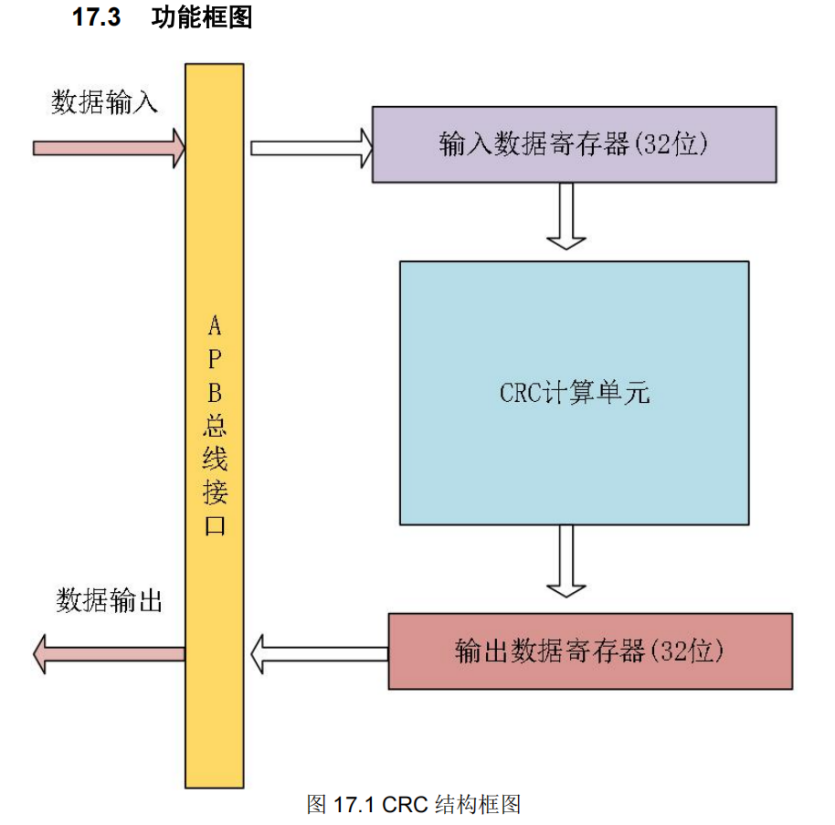

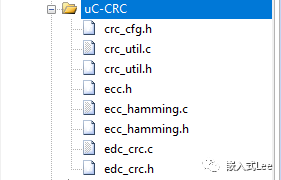

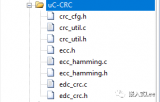

前一篇我们讲了Micrium全家桶之uC-CRC: 0x01 ECC:https://mp.weixin.qq.com/s/FKVvzwL7wzxLJCkx3gOdJQ。ECC常用于NAND进行误码校正。而CRC一般用于错误检测,比如镜像,协议的正确完备性检测。

2023-06-08 11:00:26 2252

2252

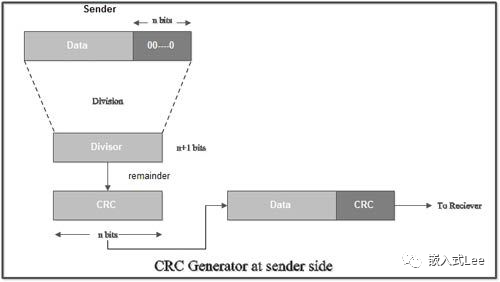

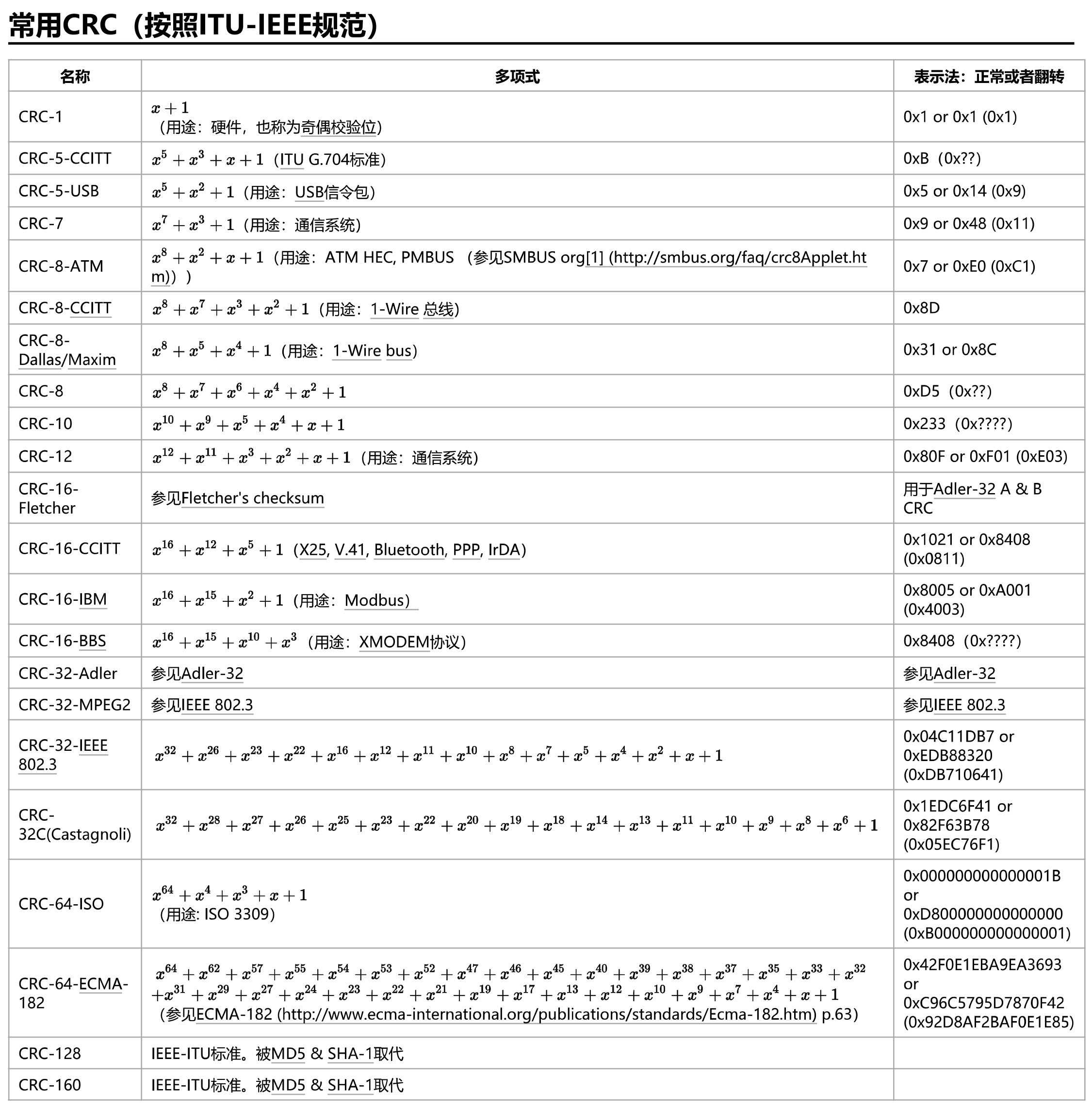

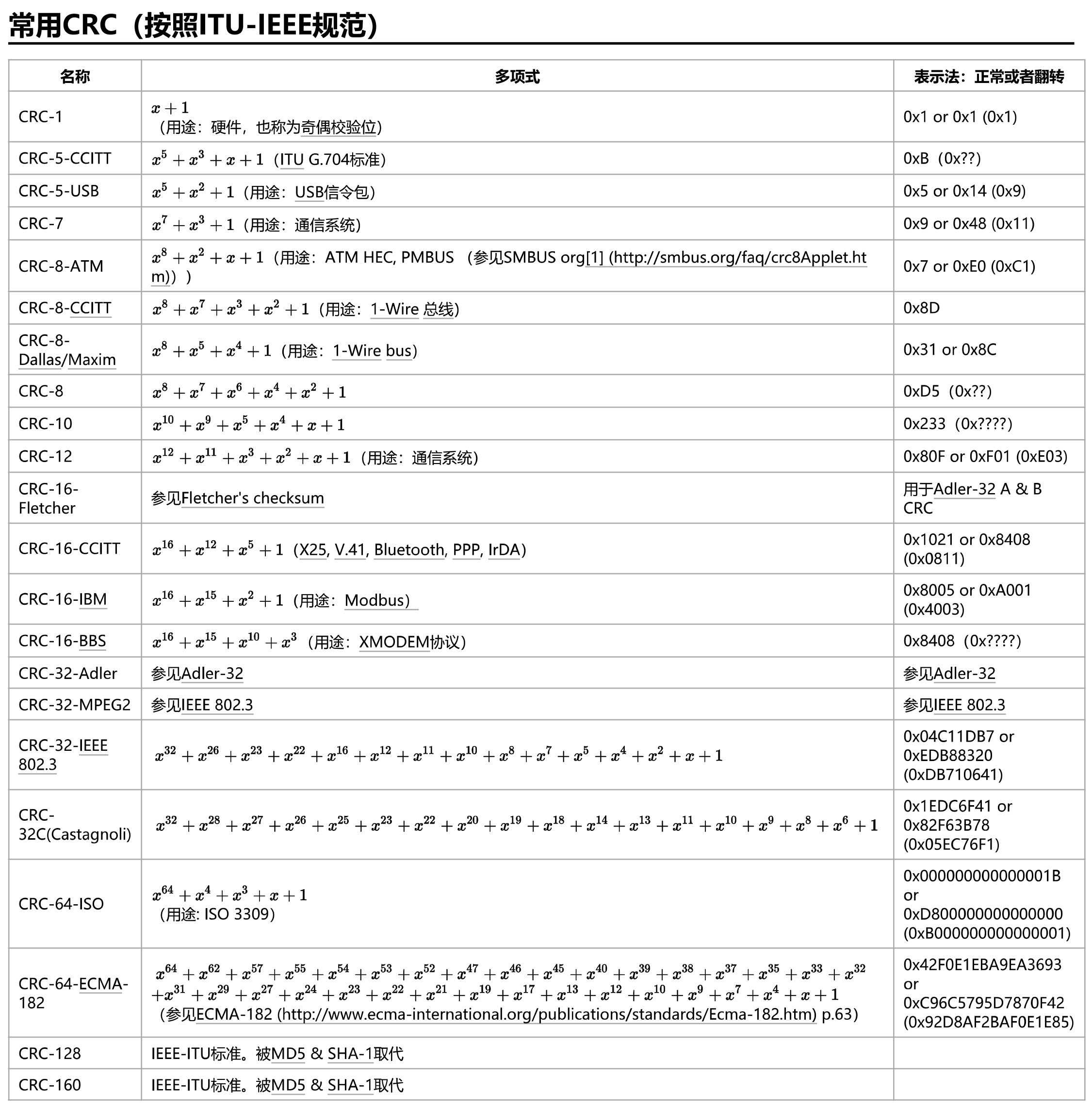

我们这一篇来讲讲Micrium全家桶的uC-CRC。该代码库提供了CRC算法进行错误检测EDC,使用HAMMING算法实现ECC错误纠正。ECC算法在NAND的TFL中使用。

2023-06-08 11:04:43 2056

2056

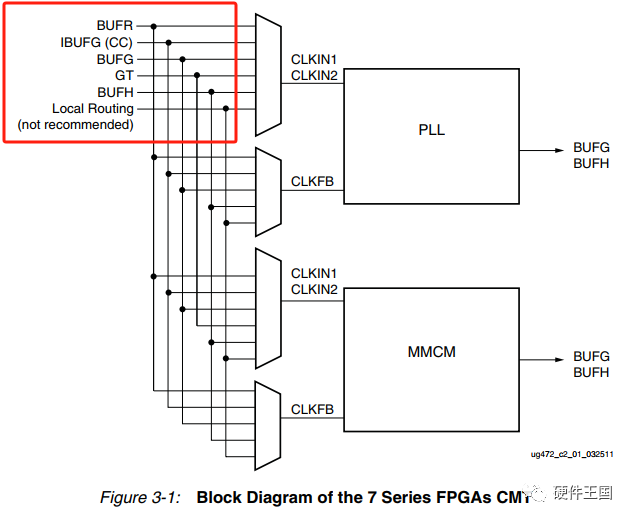

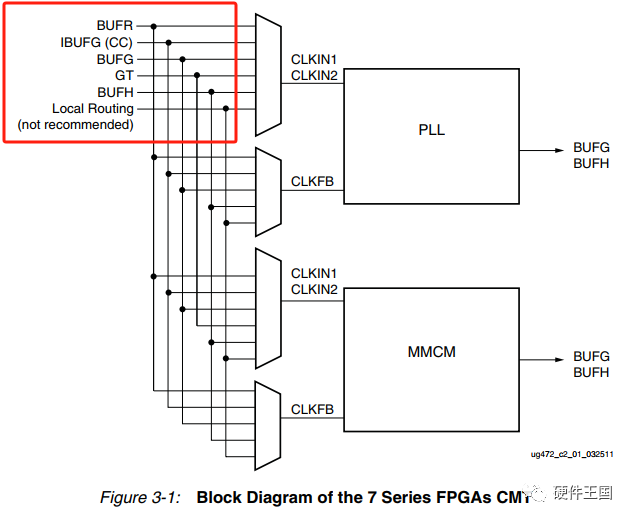

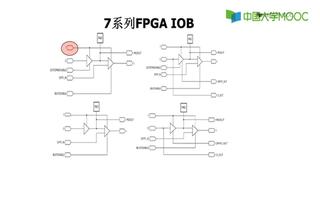

7系列FPGA包含最多24个CMT块,CMT具体的分布和与其他时钟资源的关系请参考本合集(FPGA应用开发)的上一篇文章。本文主要介绍CMT内部MMCM和PLL的区别以及在实际开发中怎么使用CMT,怎么实现跨时钟区域,第一次读者最好先阅读上一篇文章——解剖时钟结构篇。

2023-11-17 17:08:11 11730

11730

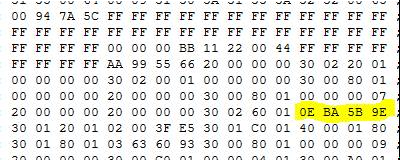

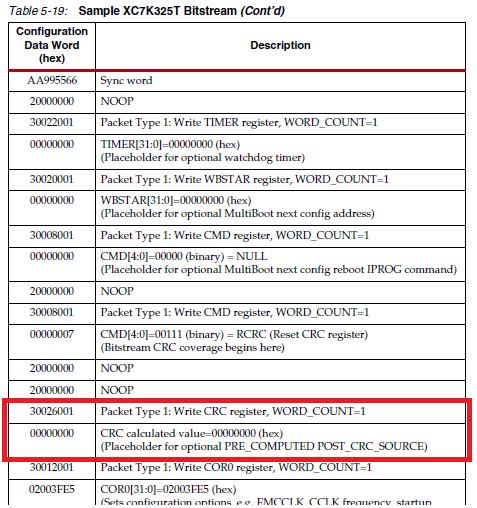

本博文介绍了利用 POST_CRC 试错的方法,但总体而言,赛灵思推荐在所有架构上使用 Soft Error Mitigation (SEM) IP

2019-07-29 10:16:56 4798

4798 7系列FPGA DSP48E1片的特点什么

2021-03-05 06:26:41

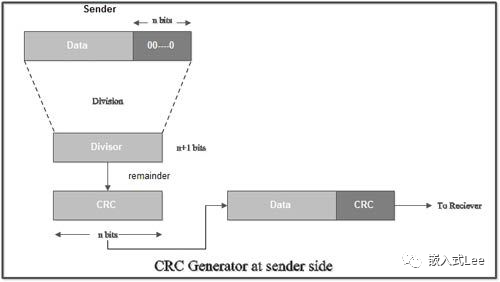

= 商 ... 余数 → 余数 = CRC码。

接收方用同样的多项式去除接收到的数据(含CRC),余数为0则认为无错。

特点:

检测能力极强:

能检测所有单比特错误。

能检测所有双比特错误(如果生成

2025-11-14 06:48:36

) = CRC(A)⊕CRC(B)的代数关系

在某风电场SCADA系统中,通过对比CRC校验与和校验的误码检测效果,发现CRC对连续8位错误的检测率比和校验高3个数量级。

2025-11-13 07:58:02

摘要:FPGA异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的几种同步策略。关键词

2009-04-21 16:52:37

EDA技术具有什么特征?FPGA是什么原理?FPGA设计应用及优化策略基于VHDL的FPGA系统行为级设计

2021-04-15 06:33:58

解决一下这个问题吗?边界扫描链成功验证。'2':读取状态寄存器内容... CRC错误:0解密器安全设置:0DCM锁定:1DCI匹配:1传输输入错误:GTS_CFG_B的第一个:GWE的0状态:GHIGH

2019-05-09 06:29:44

之间的时间间隔?还有一个问题:当POST_CRC约束设置为ENABLE时,是否意味着配置数据(或至少其中的一部分)被回读到用户逻辑中...减少可用于用户设计的资源?谢谢。

2020-06-10 09:31:14

人工智能大热之前,Cloud或Data Center已经开始使用FPGA做各种加速了。而随着Deep Learning的爆发,这种需求越来越强劲。本文主要讨论Cloud巨头Amazon和Microsoft的FPGA策略。

2019-08-13 08:37:24

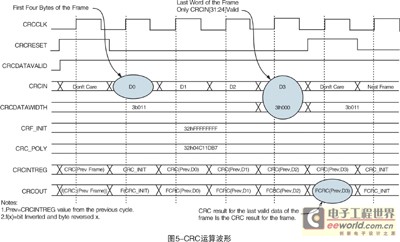

本章介绍了用户模式下的循环冗余检查 (CRC)错误检测功能,并对如何从软错误中恢复作了讲解。1 所有的 Cyclone® IV 器件均支持配置错误检测功能,其中包括 Cyclone IV GX 器件

2017-11-14 10:49:16

你好,我有一个Virtex-5设计,我试图利用POST_CRC = ENABLE约束进行SEU检测。编程后,INIT_B引脚在我预期为高电平时立即转为低电平。我的.UCF文件包含以下3行CONFIG

2020-06-16 07:37:59

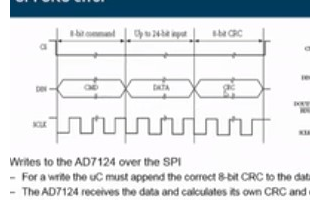

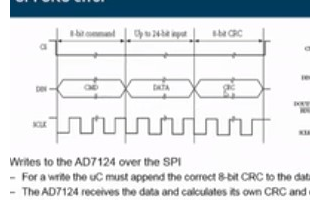

SPI 使用 CRC 时,在数据的最后半个周期写 NTC 位(Next Transmission CRC),发出的 CRC 数是错误的,举例如下:发送数据 0x55,0xAA,0x66 在收到

2023-10-20 08:10:26

Xilinx 7系列FPGA简介--选型参考

2021-02-01 06:10:55

BIOS报警声的意义是什么?什么是POST上电自检?POST是如何进行自检测的?POST自检是按什么顺序进行检测的?POST自检测代码含义是什么?POST自检发现错误后如何提示?显示卡常见故障有哪些?如何解决?

2021-11-02 06:30:38

FPGA内部直接下载比特流后)获得回读crc_error。当我们读取状态时,除了“1”而不是“0”的回读CRC错误之外,所有参数都是正常的。问题发生在+/-通常取决于4 FPGA。太多次怀疑真正的SEU问题。有什么想法来调试这个问题?谢谢。Pascal.MED

2020-06-11 10:50:22

大家好 在virtex 5 FPGA用户指南ug190中,它说: “Virtex-5 FPGA中的时钟管理磁贴(CMT)包括两个DCM和一个PLL。在CMT中有专用路由将各种组件耦合在一起。” 在7

2020-08-21 09:16:28

循环冗余校验(CRC)技术用于检测数字数据中的错误,但在检测到错误时不进行校正。该技术旨在检查数据传输或数据存储的完整性。在确保数据可靠性方面,CRC技术功能强大且易于实施。该技术的诊断覆盖范围可

2023-09-07 07:45:39

本帖最后由 mingzhezhang 于 2012-5-23 20:05 编辑

大型设计中FPGA的多时钟设计策略 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重

2012-05-23 19:59:34

调用堆栈以查看它在哪里。我在丢失远程资源库之后做的是停止并重新启动UART组件。我不认为这是最好的方法,不能找到一个明确的教程,从UART错误恢复。是否有一个状态,我可以读取和重置标志后,错误检测,使UART可以恢复硬件故障(串行线断开和重新连接)谢谢

2019-08-14 11:57:04

你好,我正在使用连接到TMS320F28335 DSP的XC7A35T FPGA。有没有办法将位流CRC存储在FPGA中,然后使用DSP进行读取?我想为每个版本生成一个新的固件版本号,将版本号存储在FPGA中,然后使用微控制器读取它。我该怎么做谢谢。斯蒂芬

2020-06-10 14:58:29

我想更改配置文件。但如果我直接编辑配置文件,则会发生crc错误。如果我想更改配置fie手动。例如:我用0xff填充原始配置文件的末尾。但我希望fpga芯片无法识别这种变化。以上来自于谷歌翻译以下

2018-10-09 15:45:56

操作中?3-在哪里我可以在软件中找到算法来计算我自己的CRC?4-有什么方法可以读取FPGA上CRC寄存器的实际值?最好的祝福,马尔特以上来自于谷歌翻译以下为原文Hi, I need some

2019-07-05 08:22:59

得到以下错误:D:/Freescale/CW MCU v11.1/gnu/bin/mingw32-make --no-print-directory post-build D:\Freescale

2023-03-31 08:42:30

的F2,F7,F10选项。所以30分钟左右后,我手动重启了NUC。此时我遇到了POST错误,无法对NUC做任何事情。如果我的回答是肯定的,那么NUC就会变得没有反应。如果我回答否,那么NUC将进入NUC

2018-10-18 14:15:55

CRC是什么东西呢?你用过RAR和ZIP等压缩软件吗?它们是不是常常会给你一个恼人的“CRC校验错误”信息呢?我想你应该明白了吧,CRC就是块数据的计算值,它的全称是“Cyclic Redundancy

2009-12-10 20:15:32 51

51 循环冗余码(cRc)是种常用的检测错误码,广泛应用十测控I耍通信领域。文中介绀基于Tt54x系列DsP的cR【:软件实上见力法。

2010-10-21 15:46:37 27

27 大型设计中FPGA的多时钟设计策略

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率

2009-12-27 13:28:04 827

827

CRC根据一个给定的数据位组算出,然后在传输或存储之前附加到数据帧尾部。接收或检索到帧后,对其内容重新计算CRC,以此来验证其有效性,确保数据无误。

2010-07-02 11:09:36 7397

7397

ARM7与FPGA相结合在工业控制和故障检测中的应用

工业控制中往往需要完成多通道故障检测及多通道命令控制(这种多任务设置

2010-11-24 10:19:54 1748

1748

在纠错编码代数中,把以二进制数字表示的一个数据系列看成一个多项式。例如,二进制数字序列10101111,用 多项式可以表示

2011-04-19 10:37:31 0

0 循环冗余码校验 CRC (Cyclic Redundancy Check) 广泛用于通讯领域和数据存储的数据检错。基于FPGA在通讯领域和数据存储的应用越来越广泛,CRC的编码解码模块已经是FPGA上的常用模块了。采

2011-08-15 11:19:57 40

40 本文利用纠错编码的基本知识,提出了一种简单实用的能自动纠正一位错误和检查两位错误的编码方法,并且通过VHDL语言编程,用FPGA器件来实现。在我们自己的嵌入式系统中,EDAC电路

2012-01-18 16:29:15 2954

2954

电子发烧友网: 本文主要介绍了赛灵思Kintex-7 FPGA 系列芯片的性能。 业界最佳性价比 Kintex-7 FPGA 是一款新型的 FPGA,展现高端性能,成本降低过半。Kintex-7 系列是在通用 28nm 架构基础

2012-06-12 10:14:18 17125

17125

本文是关于 xilinx公司的7系列FPGA应用指南。xilinx公司的7系列FPGA包括3个子系列,Artix-7、 Kintex-7和Virtex-7。本资料就是对这3各系列芯片的介绍。 下表是xilinx公司的7系列FPGA芯片容量对比表

2012-08-07 17:22:55 201

201 crc校验原理 利用CRC进行检错的过程可简单描述为:在发送端根据要传送的k位二进制码序列,以一定的规则产生一个校验用的r位监督码(CRC码),附在原始信息后边,构成一个新的二进制

2012-09-05 09:26:47 35625

35625

分析了FPGA器件发生单粒子效应的空间分布特性,设计并实现了一种面向FPGA单粒子软错误的检测电路。将该电路放置在FPGA待检测电路的附近,利用单粒子效应的空间特性,则可以根据检测模块的状态变化

2015-12-31 09:25:13 8

8 Xilinx FPGA工程例子源码:在FPGA上实现CRC算法的程序

2016-06-07 15:07:45 28

28 。该文利用输入和校验多项式的逻辑关系,成功地将基于字节的并行CRC校验算法运用于UART控制器中,在Xilinx公司的可编程门阵列(FPGA)芯片上验证通过,可实现连续多个字节校验。

2017-11-18 11:24:54 2395

2395

CRC即循环冗余校验,是一种根据网络数据包或电脑文件等数据产生简短固定位数校验码的一种散列函数,主要用来检测或校验数据传输或者保存后可能出现的错误。它是利用除法及余数的原理来作错误侦测的。

2017-11-20 13:18:07 24571

24571

编码器及检测电路实现。从其检错能力来看,它所不能发现的错误的几率仅为0.0047%以下。从性能上和开销上考虑,均远远优于奇偶校验及算术和校验等方式。因而,在数据存储和数据通讯领域,CRC无处不在。

2017-12-02 11:32:04 4973

4973 CRC即循环冗余校验码(Cyclic Redundancy Check[1] ):是数据通信领域中最常用的一种查错校验码,其特征是信息字段和校验字段的长度可以任意选定。循环冗余检查(CRC)是一种

2017-12-05 15:34:30 49537

49537

关键词:FPGA , VC707 , Virtex-7 , Xilinx Xilinx公司的7系列FPGA产品包括Artix-7系列, Kintex-7系列和Virtexreg;-7系列,具有低成本

2019-02-11 11:26:02 2524

2524

关键词:FPGA , 错误检测 , 自动纠正 引言 在一些电磁环境比较恶劣的情况下,一些大规模集成电路常常会受到干扰,导致不能正常工作。特别是像RAM这种利用双稳态进行存储的器件,往往会在强干扰下发

2019-02-18 16:34:02 1086

1086

Xilinx 7系列FPGA包括四个可满足全系列系统需求的FPGA系列,从低成本、小尺寸、成本敏感、大容量应用到超高端连接带宽、逻辑容量和信号处理能力,满足最苛刻的高性能应用。7系列FPGA包括:

2019-02-25 16:43:37 81

81 对IC或子系统之间的接口常常会增加循环冗余校验(CRC)以检测数据是否损坏,但标准中对如何确定所选CRC是否足够好则语焉不详。

2019-06-28 06:20:00 3236

3236

本文档的主要内容详细介绍的是FPGA基础及7系列FPGA基本原理的基础资料说明

2019-04-28 08:00:00 15

15 Xilinx Artix®-7 FPGA系列是一款高性价比FPGA, 提供高性能/功耗比, 高收发器线路速率, DSP处理, 集成AMS.

2019-12-03 07:07:00 12963

12963 本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-02 07:09:00 4453

4453

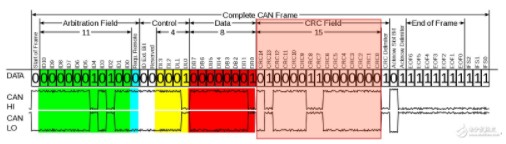

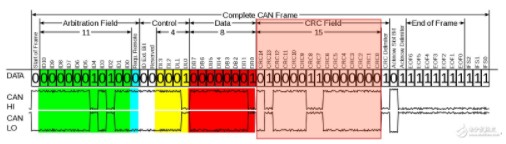

在CAN总线通信过程中CAN控制器具备完整的错误检测能力,其中包含:位错误检测、格式错误检测、填充错误检测、应答错误检测和CRC错误检测。作为一种重要的错误检测手段,CRC错误检测是接收节点判断CAN帧信息的完整性并向总线确认应答的依据。

2019-07-15 08:45:06 11409

11409

CRC 校验是一种在数据通信系统和其它串行传输系统中广泛使用的错误检测手段。通用的CRC 标准有CRC-8、CRC-16、CRC-32、CRC-CCIT,其中在网络通信系统中应用最广

2019-08-06 16:39:14 36

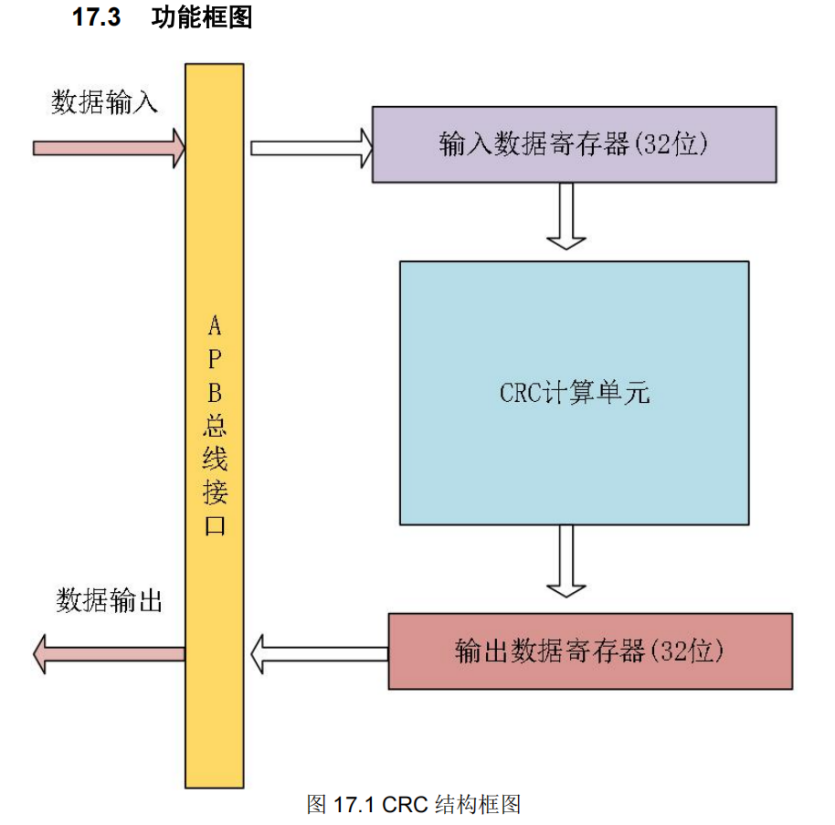

36 CRC校验、STM32中CRC计算单元、CRC应用

2020-03-04 13:54:44 7275

7275 循环冗余校验(CRC)是一种检错机制,可提高通信可靠性,以及避免意外执行错误命令。SPI 协议初始没有任何检错能力,在恶劣工业环境下可能破坏串行数据。使能 CRC 检测时(SRIAL= 高电平

2020-08-28 14:13:09 2706

2706

Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达®-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-09 14:49:00 25

25 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达?7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-09 14:49:00 6

6 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达®-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-09 15:31:13 10

10 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-10 14:20:00 18

18 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达®-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-10 15:27:48 24

24 在电脑使用过程中,可能由于非正常关机,导致系统文件损坏,从而在开机时出现windows错误恢复提示,对于这个问题,可通过计算机属性设置来解决,具体步骤如下。

2020-12-23 15:32:31 14058

14058 本文档的主要内容详细介绍的是Xilinx 7 系列FPGA中的Serdes总结。

2020-12-31 17:30:58 26

26 Xilinx-7系列FPGA主要包括:Spartan®-7、Artix®-7、Kintex®-7、Virtex®-7。其性能、密度、价格也随着系列的不同而提升。和前几代FPGA产品不同的是,7系列

2021-01-30 06:00:11 21

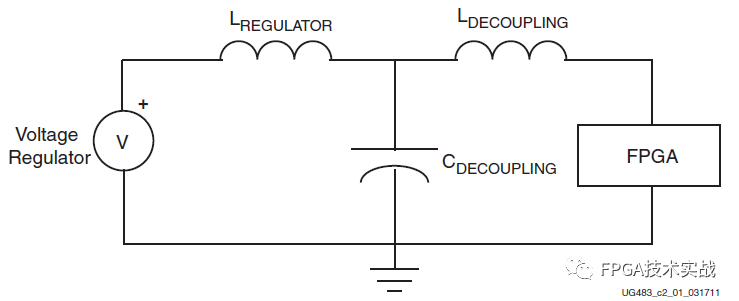

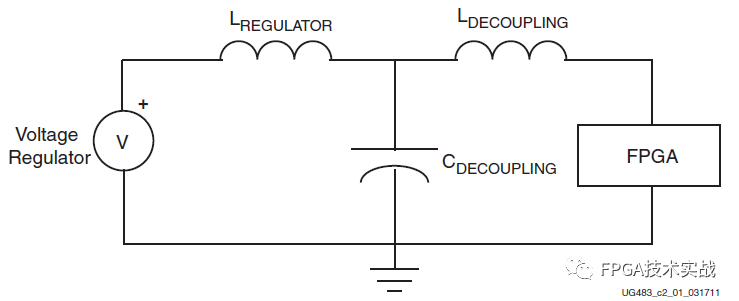

21 引言:我们继续介绍FPGA PCB设计相关知识,本章介绍7系列FPGA的配电系统(PDS),包括去耦电容器的选择、放置和PCB几何结构,并为每个7系列FPGA提供了一种简单的去耦方法。另外,还介绍了

2021-03-12 14:42:45 4988

4988

引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。为了最好地利用时钟路由资源,必须了解如何从PCB到FPGA获取用户时钟,确定哪些时钟路由资源

2021-03-22 10:16:18 6115

6115

和前几代FPGA差异,总结7系列FPGA中的时钟连接。有关7系列FPGA时钟资源使用的详细信息,请关注后续文章。 时钟资源架构概述 7系列FPGA与前一代FPGA时钟资源差异 时钟资源连接概述 1.时钟资源架构概述 1.1 时钟资源概述 7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管

2021-03-22 10:25:27 6070

6070 了按字节并行计算 CRC 校验码的 原理 ,并以常见的 CRC - 16 和 CRC - CCITT 为例 ,用 VHDL 语言进行了可综合设计。结果表明这种实现方法在速度和占 用资源方面优于常见的设计 ,适合在 FPGA 中实现 CRC 校验码的计算。

2021-03-28 09:34:24 30

30 博主的微信公众号:FPGA动力联盟博主的个人微信:fpga_start前几篇咱们说了FPGA内部逻辑,本篇咱们再聊一聊7系列FPGA的供电部分。首先咱们说spartan7系列,通常咱们需要使用以

2021-11-06 19:51:00 20

20 其中有的CRC寄存器初始值设置为全1,如以太网的CRC32,目的就是为了能检测出数据前面的0的个数。1234算出来的CRC,跟01234算出来的,不一样,这就能应对前面带0的数据了。

2022-08-26 14:11:35 3697

3697 AN4187 在STM32系列中CRC外设的使用方法

2022-11-21 17:07:04 1

1 以正确的方式发音是最难获得的技能之一,全球的研究人员正专注于使用机器/深度学习技术检测发音错误。在线学习中错误发音检测的目的是高精度地识别发音错误或缺陷,并提供指导性反馈以改善发音。

2022-11-29 12:10:26 1220

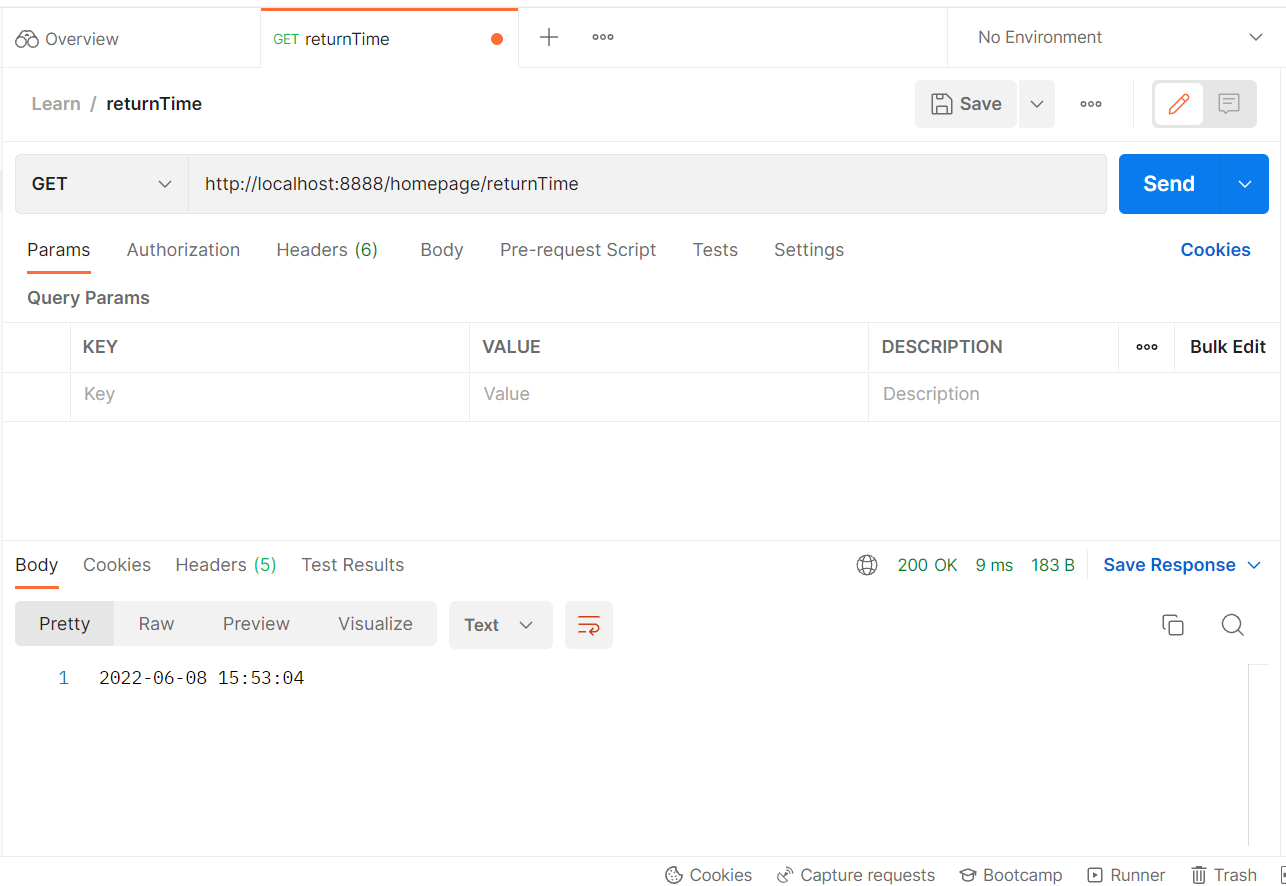

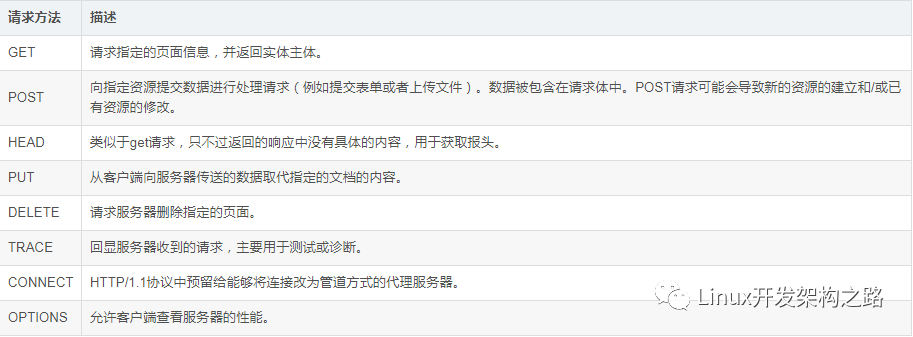

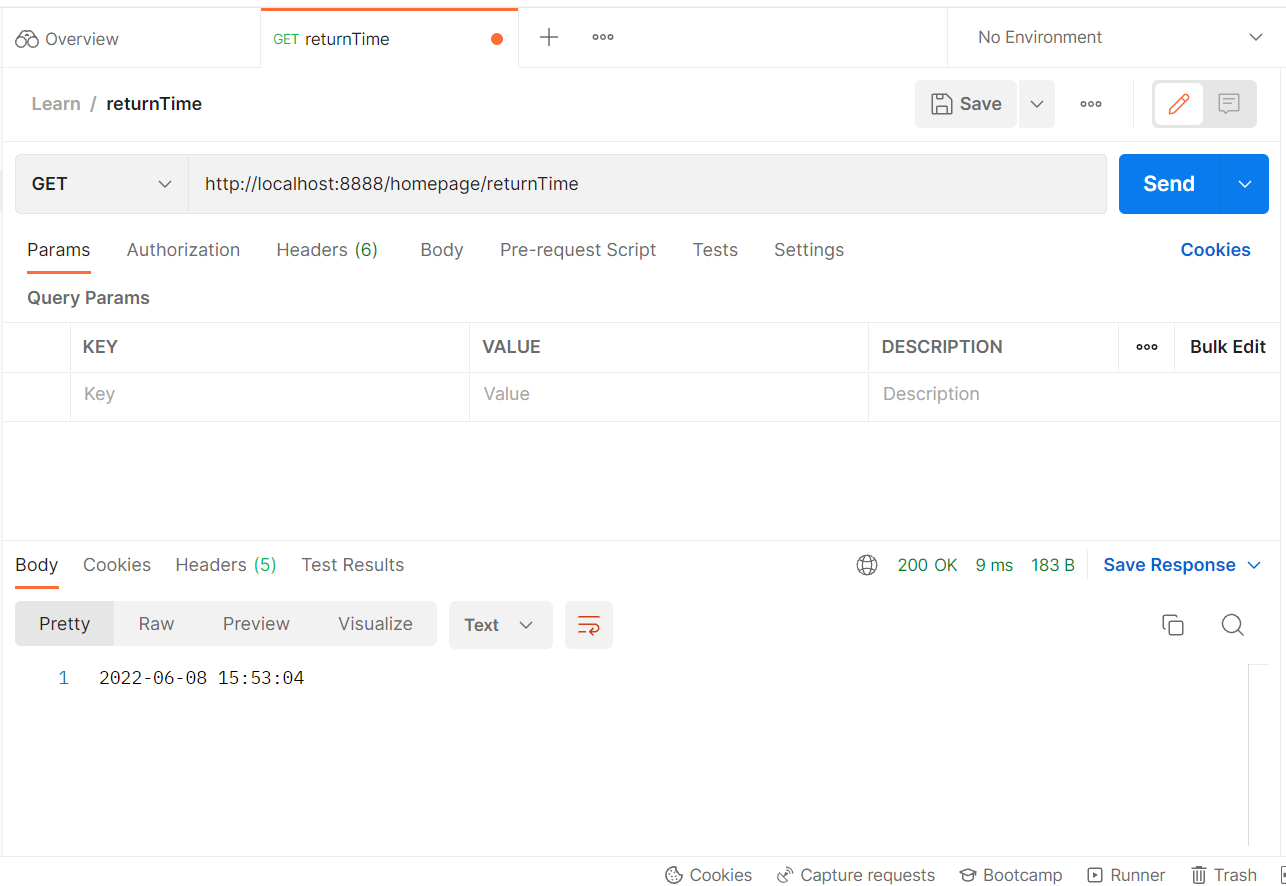

1220 Java中Get和Post的使用

2023-01-12 15:38:05 1376

1376

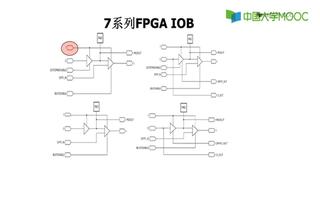

7系列FPGA是基于28nm工艺制程。在7系列FPGA中,每个输入/输出区域(I/O Bank)包含50个输入/输出管脚,其中有4对(8个)全局时钟管脚,称之为CCIO(Clock-capable IO)。

2023-03-03 09:46:49 3186

3186 我们这一篇来讲讲Micrium全家桶的uC-CRC。该代码库提供了CRC算法进行错误检测EDC,使用HAMMING算法实现ECC错误纠正。

2023-05-04 10:47:44 1642

1642

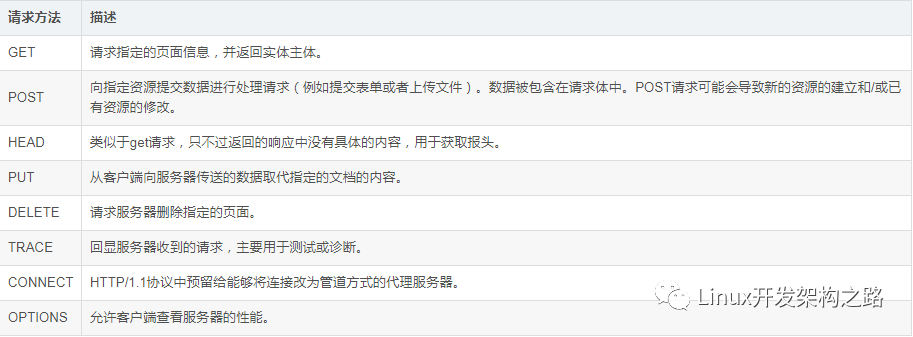

GET和POST是HTTP请求的两种基本方法,要说它们的区别,接触过WEB开发的人都能说出一二。

最直观的区别就是GET把参数包含在URL中,POST通过request body传递参数。

2023-08-05 12:21:42 828

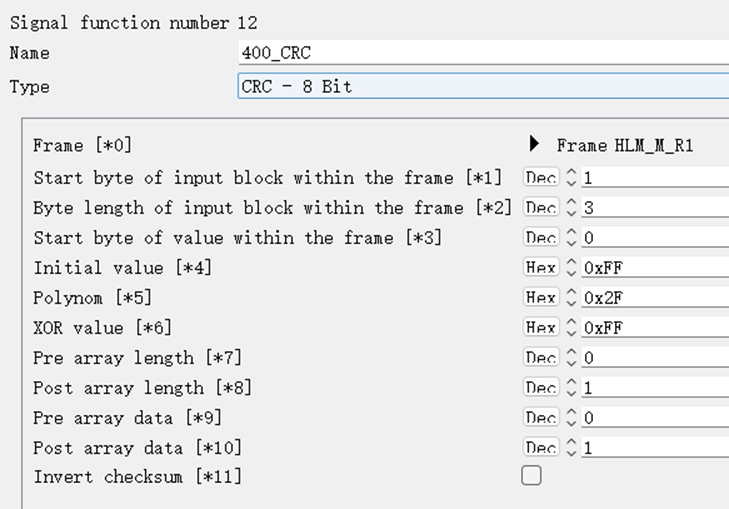

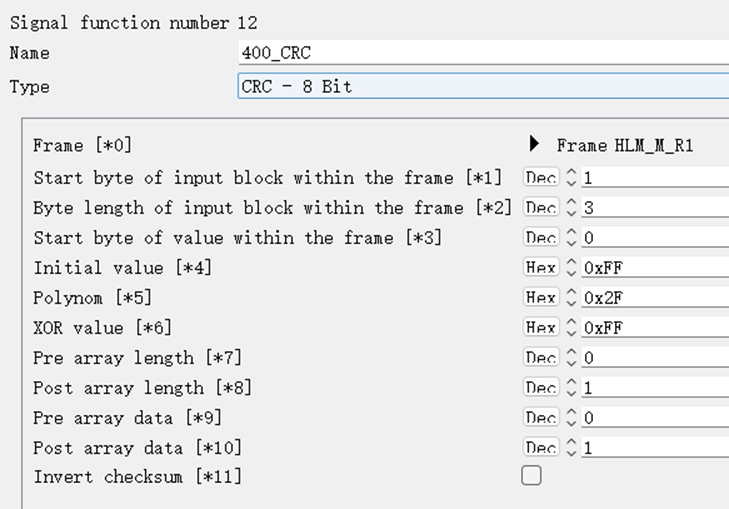

828 在通讯过程中,用户需要利用CheckSum信号对传输数据用自己规定的算法逻辑进行校验,来看数据在传输过程中是否被更改或传输错误。本文主要介绍TSMaster如何设置自己的CRC算法信号。CRC相关

2023-09-09 08:23:25 2543

2543

电子发烧友网站提供《将SPI闪存与7系列FPGA结合使用.pdf》资料免费下载

2023-09-13 10:00:23 0

0 电子发烧友网站提供《7系列FPGA配置用户指南.pdf》资料免费下载

2023-09-15 10:19:57 3

3 Xilinx是一家专业的可编程逻辑器件(PLD)厂商,其产品包括FPGA、CPLD、SOC等。Xilinx的FPGA产品线有多个系列,其中7系列和Ultrascale系列是比较常见的两种。那么,这两个系列有什么区别呢?

2023-09-15 14:44:54 9018

9018

单片机中CRC原理及应用

2023-09-27 16:02:15 3129

3129

奇偶校验和crc校验的区别 CRC校验和奇偶校验之间有什么关系? 奇偶校验和 CRC(Cyclic Redundancy Check)校验都是用于网络通信或存储数据时的错误检测方法,两种校验

2023-10-17 16:28:21 4821

4821 一、概述 HTTP 的请求报文 GET 方法的特点 POST 方法的特点 GET 和 POST 的区别 二、HTTP 的请求报文 首先我们要解决的第一个问题是:GET 和 POST 是什么? GET

2023-11-11 14:40:22 1694

1694

Xilinx 7系列 芯片 应用非常广泛,具有成本低、性能强悍、成熟稳定的特点,目前Xilinx( AMD )已延长该系列芯片的生命周期至少到2035年。 本文主要介绍Xilinx 7系列 FPGA

2023-11-28 10:20:02 2842

2842

文章将以CRC8校验为例,介绍在BabyLIN产品中如何使用CRC校验算法。 CRC校验原理 在CAN报文中,增加Checksum校验,能够用来检测和校验数据传输或保存后可能出现的错误。它是利用除法及余数的原理来作错误侦测的。CRC8校验算法,就是对一帧报文进行校验和计算

2024-01-02 10:45:16 1279

1279

常用的校验方法,用于检测和校正数据传输中的错误。在FPGA设计中,CRC故障指的是与CRC相关的错误或问题。 首先,让我们了解CRC是什么以及它在数据传输中的作用。CRC是一种基于二进制算法的校验

2024-01-04 11:06:15 2808

2808 电子发烧友网站提供《SRAM中的错误检测.pdf》资料免费下载

2024-09-20 11:15:25 0

0 Xilinx7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7系列FPGA PCIe Gen3的应用接口及一些特性。

2024-11-05 15:45:10 4694

4694

、执行器动作异常甚至整个控制系统宕机。循环冗余校验(CRC)作为一种高效的错误检测技术,如同数据传输与存储过程中的"安全校验屏障",持续保障MCU与外部设备交互数据的准确性。本文将系统阐述国科安芯推出的AS32系列MCU芯片中的CRC计算单

2025-11-21 15:20:14 1210

1210

数据损坏与校验错误是瀚海微SD NAND/TF卡在数据存储与传输过程中的关键故障,除常见的CRC错误外,数据比对失败(读取数据与写入数据不一致)是核心表现形式,直接影响数据准确性,在工业控制、高清存储等场景中可能引发严重后果。以下从故障表现、成因及解决方案展开详细说明。

2025-11-30 15:15:54 611

611

电子发烧友App

电子发烧友App

评论