经常涉及对宽带模拟信号进行数据采集和存储,以便计算机进一步进行数据处理。为了对高速模拟信号进行不失真采集,根据奈奎斯特定理, 采样频率必须为信号频率的2 倍以上,但在电阻抗多频及参数成像技术中正

2023-09-15 09:45:01 3841

3841

1、 应用背景

基于ARM+FPGA的高速同步数据采集方案,解决了数据采集的同步性问题,与以往

2010-07-22 16:36:17 1633

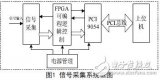

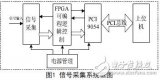

1633 为解决现场测试系统中微弱信号的高速实时采集处理和及时可靠存储的问题,本文提出了基于PCI总线的数据采集电路的设计方案,该方案将模拟信号通过高速A/D芯片有效采样,在FPGA的控制下将数据上传到PC机

2014-01-24 09:45:29 4027

4027

随着现代检测技术和科技水平的高速发展,信号采集技术的应用范围越来越广泛[1]。与此同时,对信号采集系统的采集精度、采样率以及便携性等设计需求提出了更高的要求。现场可编程门阵列(FPGA)具有逻辑门

2020-01-26 16:58:00 2987

2987

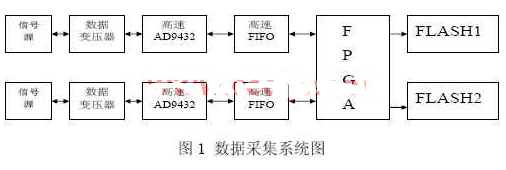

的领域。目前由于数字信号的快速发展,对信号采集的要求也不断的提高,特别是在参数方面的要求越来越高,如精度、速度、采样通道数等。鉴于此,本文会介绍一种基于FPGA来控制高速A/D转换器AD9432实现高速采集,从而满足在系统中的应用。

2020-07-30 17:53:31 3597

3597

,基于Xilinx 6系列FPGA实现。集成了丰富的对外高速和低速接口。系统由CPU子系统、数据采集(DAQ子系统、高速存储(Storage)子系统和数据回放(loopback)子系统构成,具有配置灵活

2016-07-25 11:35:43

E30-M系列/E32-M系列的产品有哪些?有什么优势?

2022-03-02 07:19:01

门阵列实现1bit 的RAM时一般需要4 个门,因此 ESB/BARM 做RAM使用时,1bit 等效 4 个门,对Altera FPGA 中一个2048bit的ESB ,等效门数为8K。光靠这些数据还不

2012-08-11 10:29:07

RAM Bits 327,680Maximum Macrocells2,560Maximum I/O Pins 716图1 EP20K 系列的等效门数下面以EP20K1000E 为例详细说明FPGA

2012-03-01 10:08:53

的EZ-USB FX2系列智能USB接口芯片。其作用是将主机所发送的命令序列经USB2.0端口输出,实现对数据采集系统的控制;同时把A/D转换器采集的数据以高速的数据序列形式发送到主机。其中,USB2.0端口

2020-01-07 07:00:00

比较器将网线传输过来的差分信号转为单端信号,该信号时钟频率为100M,电平标准能满足FPGA的输入电平标准,波形质量尚可。单端信号直接连接到FPGA,现在如果想用FPGA直接采集,应该怎么处理呢,是当作异步信号直接打拍吗,过采样的话时钟频率不够。时钟恢复目前来不及实现。

2020-03-07 16:01:37

JESD204B协议ADC多片多通道之间采样点相对时延固定,从而确保各通道采集信号相位一致。JESD204B协议支持的确定性延迟特性保证了设计实现。验证方案的测试电路采用XilinxK7系列FPGA控制

2019-12-03 17:32:13

。JESD204B协议支持的确定性延迟特性保证了设计实现。验证方案的测试电路采用XilinxK7系列FPGA控制两片AD9694(采样率320Msps)同步采集,证实设计方案满足应用需求。3、雷达

2019-12-04 10:11:26

采用的高速AD:PXIe-5114 PXI示波器,高速DA:PXIe-5413 PXI波形发生器,跪求实现高速DA采样和AD的例程。

2018-08-21 16:19:19

各种高速AD采集卡大体硬件功能相同时,使用不同的FPGA 时,如V5和V6系列,单就高速AD采集卡的逻辑和性能来说,带来一些差异。通过简单对比北京坤驰科技有限公司的使用了交织采样技术的高性能同系列

2016-03-10 14:10:43

。 3、海量缓存的设计实现 本系统使用了两片256k16bit容量的SRAM作为高速缓存,系统中的4个通道可同时存储每通道128k点采样数据。在25MHz的采样频率下,一次可采集存储5ms多的波形

2020-12-04 15:59:14

ADC采样遇到了问题,采集的信号值是逐渐连续减小的。我采样时是每10ms采集一次,采集32次排序,取中间的24个值求平均,每秒运算出一个值。但是实际测量中,大概每隔30S左右。我的采样值会连续2-4

2023-06-26 08:14:59

测试条件:

1,线性电源12.6V,分压电阻20K:2K

2,AMS1117降压到5V供电 N76E003 ;

3,ADC_BandGap读出来是比较稳定的。

4,ADC单通道在分压电阻处连续采样

2023-06-25 13:23:43

PCIE高速传输方案传输的带宽利用率可达到90%以上,延迟可达到理论的最低延迟值。该方案已经应用到航天航空、雷达等领域。一、 高效率传输方案 该采集方案 Demo 基于 VC709 开发板

2021-05-19 08:58:02

10KE EPF10K30E, FLEX 10KE EPF10K50S, FLEX 10KE EPF10K100E, FLEX 10KE EPF10K130E, FLEX 10

2012-08-15 12:30:03

需要实现整数和半整数频率合成;输出频率范围为1KHz-999.5KHz,步进频率为0.5KHz。FPGA芯片选用的是FLEX 10K系列的EPF10K10LC84-4,40MHz的有源晶振,LCD1602显示小妹实在是太菜了,看了几日还在门外徘徊,不知大神们是否有心情,求赐教~

2014-03-30 13:51:03

项目名称:高速AD采集板试用计划:申请理由本人一直做高速AD采集及高速DA设计,一直使用Xilinx K7 系列及ZYNQ系列FPGA,电源方面一直寻求更好的解决方案。想借助发烧友论坛和MPS电源

2020-06-18 13:43:36

对数据采集与处理系统提出了新的更高的要求,即高速度、高精度和高实时性。对数据采集与处理系统的设计,有以下3种方案可供选择:(1)A/D+DSP方案在传统的高速信号处理中,大多采用这种方案。将A/D、D

2019-07-05 06:41:27

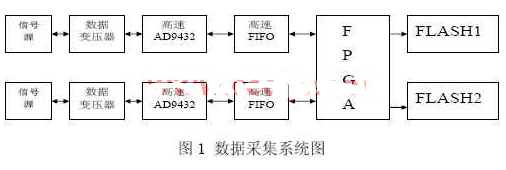

高速、超宽带信号采集技术在雷达、天文和气象等领域应用广泛。高采样率需要高速的模/数转换器(ADC)。目前市场上单片高速ADC的价格昂贵,分辨率较低,且采用单片超高速ADC实现的数据采集对FPGA的性能和PCB布局布线技术提出了严峻的挑战。

2019-11-08 06:34:52

环境模拟信号的高速采集、分析、记录、存储和回放产生。超宽带信号高速采集记录存储回放系统基于高性能PCI EXPRESS及SRIO协议,实现标准化、模块化、可扩展、可重构的超宽带信号高速连续采集记录回放产生

2020-08-26 11:53:36

哪位大神能告我如何在qutars ii上添加EPF10K20TC144-4的裤

2014-05-31 11:01:55

。为了实现高速、连续采样的数据采集系统,本文介绍了一种基于 FPGA +AD7609的数据采集系统的构成及技术实现。采用 FPGA 作为主模块,AD7609为数据采集模块,并设计了硬件实现电路。实验测试

2018-08-09 14:28:00

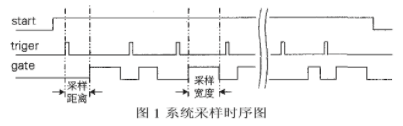

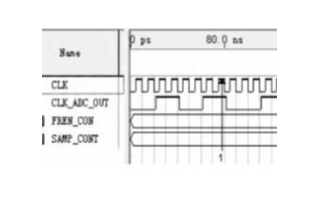

的输入输出接口设计就显得尤为重要。1 高速采集系统介绍 数据采集系统原理框图如图1所示,输入的中频信号经A/D采样电路采样后,转换成LVDS信号送入FPGA中,或通过FPGA的端口RocketIO从高速接口

2018-12-18 10:22:18

目前,在数据采集系统的硬件设计方案中,有采用通用单片机和USB相结合的方案,也有采用DSP和USB相结合的方案,前者虽然硬件成本低,但是时钟频率较低,难以满足数据采集系统对速度要求;后者虽然可以实现

2019-09-05 07:22:57

率、高精度、多通道同步数据采集方案,可以通过监测者的要求完成多通道数据的同步采集并实现实时的网络传输。 基于ARM+FPGA的高速同步

2010-08-31 09:14:55

为了实现—是弹武器瞄准自动化,本文设计了基于DSP和FPGA的高速高精确度双通道CCD图像采集系统,采用QUartuBn在AJtera的FPGA器件CYCLONEII上设计了CCD驱动时序电路,采用

2014-11-07 14:54:07

) 以其可靠性好、集成度高、功耗低和运算速度高等优势,在高速实时图像采集系统得到广泛应用。这里采用FPGA控制MV-D1024E系列相机的数据接口,实现了脱离PC机的图像采集卡功能。为方便系统和用户输入,设计了基于USB的PC机接口。通过USB接口,同样可用于脱离PC机的系统。

2019-07-02 08:11:34

本文主要讨论使用FLEX10K系列FPGA来实现信道编码的功能。

2021-06-07 06:00:58

高速连续数据采集系统的背景及功能是什么?如何利用FPGA实现高速连续数据采集系统设计?FPGA在高速连续数据采集系统中的应用有哪些?

2021-04-08 06:19:37

怎么实现高速采样保持电路的设计?

2021-10-11 07:42:17

你好,我感兴趣的是汇集一个高速数据采集系统。我正在考虑将高速ADC直接连接到FX3/FX3S的可能性,而不使用例如使用GPIF的FPGA。我所看到的ADCs是14(或16)位四路和八路同时采样ADC

2019-09-11 10:56:03

数字滤波器是什么?数字滤波器有哪些特点?怎样去设计一种基于EPF10K10LC84芯片的IIR滤波器?

2021-10-20 08:01:13

如何利用单片机AT89C52对FLEX10K系列FPGA中的EPF10K10进行在线并行配置?

2021-04-29 06:19:03

求大神分享一种高速突发模式误码测试仪的FPGA实现方案

2021-04-29 06:58:18

电机控制之旋变及位置反馈解决方案篇其它话题的热门问答请前往总贴查看。http://www.deyisupport.com/question_answer/microcontrollers/c2000

2020-05-20 09:33:31

得到采集数据,在数据传输端,可以采用如下4种方案:方案1:通过设置触发门限,只采集有用信号。 在脉冲周期为10ms时,每个脉冲根据触发设置,采集3us左右(长度可以设置),约3000个采样点;实时传输

2016-08-15 14:59:39

在超高速数据采集方面,FPGA(现场可编程门阵列)有着单片机和DSP所无法比拟的优势。FPGA时钟频率高,内部时延小,目前器件的最高工作频率可达300MHz;硬件资源丰富,单片集成的可用门数达1000万门;全部控制逻辑由硬件资源完成,速度快,效率高;组成形式灵活,可以集成外围控制、译码和接口电路。

2019-08-02 06:51:33

` PXDAQ18373E是一款高精度高速率的声发射采集卡,该卡具有真实的18bit采样精度和每通道30M/S的采样率,采用标准的PICE2.0 X 8接口,数据通过率高达2.6GB/s,是迄今为止

2016-09-22 14:17:14

探讨了高速数据采集系统中高速采样缓存的重要性和实现途径,阐述了基于ADSP-21065L的并行多通道数据采集板上高速采样缓存的设计与电路结构,给出了采用FPGA实现通道复用和采样数据

2009-04-23 17:08:09 23

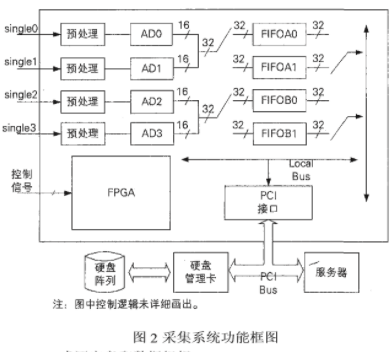

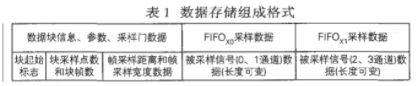

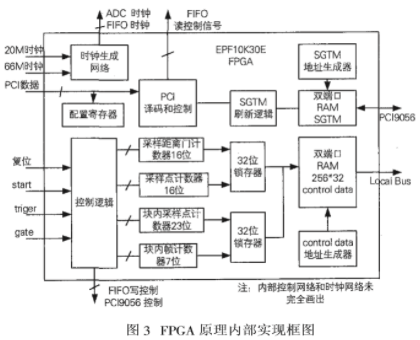

23 本文提出了一种用于雷达回波信号采集的高速数据采集系统。该系统实现了对数十兆赫的回波信号进行连续的采样和存储。系统通过FPGA控制数据连续采集、缓冲,通过PCI9056将缓冲区

2009-08-15 11:45:53 23

23 本文介绍了一种高速双通道遥感卫星信号实时采集处理技术的研究与实现。基于Xilinx Spartan3 150万门高性能FPGA,设计出具有数据海量传输和高速处理能力需求的卫星信号采集处

2009-09-26 15:30:39 25

25 本文介绍了一种基于FPGA 的高速多路数据采集系统的设计方案,描述了系统的主要组成及FPGA 的实现方法。在硬件上FPGA 采用ACEX1K100 器件,用于实现A/D 转换器的控制电路、多路

2009-12-19 16:02:33 50

50 本文介绍了一种能够完成半整数和各种占空比的奇/偶数和的通用的分频器设计,并给出了本设计在Altera公司的FLEX10K系列EPF10K10LC84-3型FPGA芯片中实现后的测试数据和设计硬件的测

2009-12-19 16:25:09 65

65 本文针对磁通门信号采集与处理的具体特点,对基于FPGA的磁通门数字信号处理系统进行了研究。该系统采用A/D转换器对磁通门输出信号进行采样,采样后的数据通过FPGA进行数据

2009-12-23 15:09:09 15

15 本文针对磁通门信号采集与处理的具体特点,对基于FPGA的磁通门数字信号处理系统进行了研究。该系统采用A/D转换器对磁通门输出信号进行采样,采样后的数据通过FPGA进行数据处理,再

2010-07-21 17:24:58 26

26 为解决现有采集存储系统不能同时满足高速率采集,大容量脱机且长时间持续存储的问题,设计了一种基于SATA硬盘和FPGA的数据采集和存储方案。本设计由AD9627转换芯片,Altera Cyclone系列

2011-11-15 11:35:19 170

170 本文一Spartan-3E系列FPGA为核心控制模块,结合AD10242数模转换芯片和MAX-123MD-F光收发模块,实现了告诉数据采集和光纤传输。

2012-05-24 15:38:26 72

72 恒颐基于ARM+FPGA的高速同步数据采集方案,解决了数据采集的同步性问题,与以往的数据采集方案相比,具有高精度、高速率、多参数同步测量、实时处理、网络传输不受区域限制等特点

2012-11-27 10:51:24 1670

1670 高速数据采集系统中的FPGA的设计,下来看看

2016-05-10 11:24:33 15

15 基于FPGA的高速数据采集硬件系统设计.

2016-05-10 17:06:40 48

48 基于FPGA的高速数据采集系统接口设计.

2016-05-10 17:06:40 27

27 基于FPGA的高速数据采集系统的设计,下来看看

2016-05-10 17:06:40 21

21 基于FPGA高速数据采集的解决方案,下来看看

2016-05-11 09:46:01 13

13 基于FPGA的高速数据采集系统设计,用ad芯片和sdram构成高速数据采集系统。

2016-05-17 09:49:51 35

35 基于FPGA的高速图像采集系统的研究与设计

2016-08-30 15:10:14 6

6 变采样率技术在连续波测速雷达中的应用,下来看看

2017-01-08 15:59:09 12

12 基于FPGA实现变采样率FIR滤波器的研究

2017-01-08 15:59:09 19

19 基于FPGA的高速多通道AD采样系统的设计与实现_徐加彦

2017-01-18 20:23:58 12

12 本文针对由FPGA构成的高速数据采集系统数据处理能力弱的问题,提出FPGA与单片机实现数据串行通信的解决方案。

2017-02-11 14:30:00 11728

11728 采用FPGA实现对AD 输出数据的高速采集

2017-08-30 17:16:02 36

36 提出了基于Xilinx公司Virtex-5系列FPGA中RocketIO GTP收发器设计的一个高速串行传输实现方案,详细阐述了硬件设计要点和软件实现概要,系统实测表明,该方案能在某信号处理系统两个板卡之间稳定地进行1.6 Gb/s的数据传输,误码率优于10e-12,传输距离大于1米。

2017-11-21 10:16:00 9094

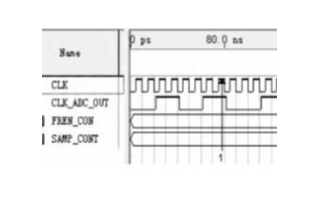

9094 针对机械设备运行中的振动监控,设计振动信号采集系统,提出了一种基于FPGA的振动信号采集系统的设计方案。重点阐述了系统硬件结构组成、信号调理电路和数据采集模块的设计,同时对A/D采样的控制逻辑进行了讨论。经试验验证表明,该系统可达到采样率10 K每秒、采集精度16位,能够满足实时性和精度要求。

2017-11-17 11:04:38 8468

8468

设计了基于FPGA与ARM 芯片的数据采集系统,FPGA 负责控制A/D转换器,保证了采样精度与处理速度,ARM负责逻辑控制及与上位机交互的实现,并将采集到的数据通过USB高速上传至主机进行实时处理。对模拟数据采集的测试结果达到了较高的采样精度和速度,验证了整个系统的高速性和可行性。

2017-11-18 12:47:10 5019

5019

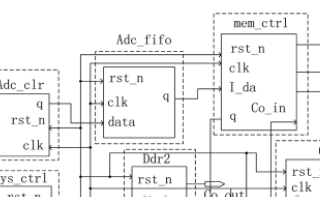

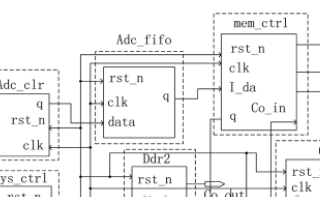

随着测试环境越来越复杂,需要采集的参数种类越来越多,要求采集系统连续采集各种传感器输出的模拟信号,而目前常用的固态存储器件FLASH的写入速率比较低。本文提出一种基于FPGA(现场可编程门阵列)片

2018-07-12 09:06:00 6077

6077

利用AD574A设计基于FPGA的高速数据采集系统,系统包含内嵌双口,在FPGA内部实现的RAM用于写入操作;地址计数器,用于提供存储地址保存采集数据。具备高采样精度、高集成度,并且速度快、灵活性强、可靠性高,易于升级与扩展。

2017-12-18 17:37:20 9294

9294

,常规做法是利用插值和抽取的方法实现数字信号的变采样处理,这种方法实现复杂,硬件成本高。文中提出了一种高速并行成型滤波器的FPGA实现方法,这种基于群延时结构的查找表算法,所需的查找表只需存储单位冲击响应的采样值,

2018-02-23 10:14:22 0

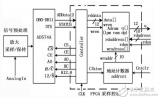

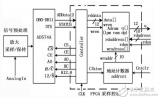

0 数据采集系统的总体架构如图1所示,其中PCI核、DMA控制器与A/D控制器均在FPGA内部实现。为实现多路并行采样,可选用多片A/D器件并行处理的方式,在FPGA的高速状态机控制下,完成模拟信号经过

2018-08-28 10:16:07 14862

14862

为了实现高清晰度油气管道漏磁检测器高精度多通道数据采集的要求,采用AlteraCyclone系列FPGA EPlC6为核心控制模块,结合AD9223模数转换芯片构建了超多通道、高速数据采集系统。利用

2018-10-16 10:34:09 51

51 在嵌入式系统设计中,掌握MCU对FPGA的配置,对系统的设计是十分必要的。根据EPF10K10的配置时序和AVR单片机Atmega128的接口特点,详细介绍了Atmega128对EPF10K10配置的软硬件设计原理。

2018-10-26 15:34:41 9

9 本文提出了一种实现信号采集方案,介绍了由ARM 处理器S3C2410 和EP2C8 FPGA 组成的高速信号采集系统的系统设计,并着重介绍前端硬件的设计,并就ARM 处理器和FPGA 的互联设计进行探讨。利用FPGA 硬件控制A/D 转换,达到了较好的效果,实现了信号的采集与存储。

2018-11-02 15:46:01 12

12 介绍了1种基于FPGA和DSP的高速数据采集系统的设计和实现,其FPGA采用Altera公司ACEX 1K系列的EPIK50Tcl443器件,DSP芯片采用TI公司TMs320系列

2018-11-07 17:18:24 20

20 采用DDR2 SDRAM作为被采集数据的缓存技术, 给出了USB2.0与DDR2相结合的实时、高速数据采集系统的解决方案, 同时提出了对数据采集系统的改进思路以及在Xilinx的Virtex5 LX30 FPGA上的实现方法。

2018-12-07 16:12:39 21

21 在FPGA高速AD采集设计中,PCB布线差会产生干扰。今天小编为大家介绍一些布线解决方案。

2019-03-07 14:52:24 7372

7372 提出了一种基于FPGA+ARM的多路视频采集系统的设计与实现方法。该视频采集系统不仅能对多路快速变化的视频信号进行采集和处理,而且能应用为系统信号发生设备.系统采用FPGA为核心高速时序逻辑控制

2019-11-19 15:51:42 21

21 FPGA是一种可编程逻辑器件,它具有良好性能、极高的密度和极大的灵活性,外围电路简单可靠等特性。因此,该系统设计是由MCU、FPGA、按键等部分组成。60路按键信号进入FPGA单元,以供数据采集

2020-08-11 14:40:36 1164

1164

基于FPGA 在高速数据采集方面有单片机和DSP 无法比拟的优势, FPGA 具有时钟频率高,内部延时小, 全部控制逻辑由硬件完成, 速度快,效率高,组成形式灵活等特点。因此,本文研究并开发了一个

2020-08-21 16:16:00 32

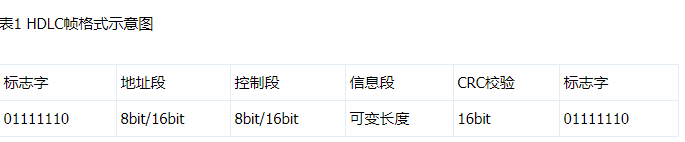

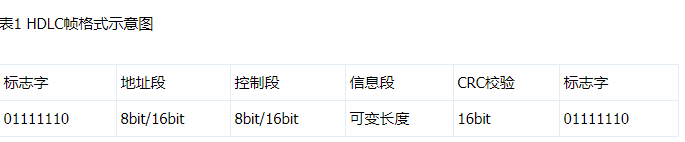

32 .同时它还具有设计开发周期短、设计制造成本低、可实时在线检验等优点,因此被广泛用于特殊芯片设计中.本设计中采用Altera公司的FLEX10K芯片EPF10K20RC240-3来实现HDLC协议控制器.

2020-09-27 21:00:12 1829

1829

本文档的主要内容详细介绍的是基于FPGA的AD采样的实现免费下载。

2021-01-21 15:33:54 32

32 通过FPGA(现场可编程门阵列)时序模型分析得出FPGA门延时的方案,综合利用FPGA各种布局布线EDA工具,摸索出一套人工干预FPGA布局布线的方法,使FPGA门延时能够有效地用于时序调整,调整精度可达到纳秒级。该方法具有不增加任何额外器件,成本低、高效方便的特点。

2021-01-26 16:22:00 13

13 基于图像采集系统高速、大容量的特点,提出了一种以FPGA芯片为核心处理器件的CMOS图像传感器数据采集系统的设计方案。系统将模块化结构设计、LVDS与乒乓存储等多项技术应用于设计过程中,保证了

2021-01-29 15:27:49 9

9 介绍一种基于Actel公司Fusion StartKit FPGA的线阵CCD图像数据采集系统。以FPGA作为图像数据的控制和处理核心,通过采用高速A/D、异步FIFO、UART以及电平转换、放大

2021-02-02 17:12:32 8

8 为了解决图像扫描设备与主机之间海量数据高速传输问题,提出了一种基于FPGA的图像数据采集卡的设计方法。该设计方法对采集卡的原理设计、FPGA的开发以及驱动程序的实现进行了研究;板卡采用

2021-02-03 16:26:11 21

21 针对高速率QPSK数据传输链系统,比较分析了数字中频接收与零中频接收的优、缺点,并提出了一种基于多相滤波的宽带中频正交采样数字零中频接收方案。基于FPGA对此数字零中频正交变换方案进行了实现和验证,同时,对一种全数字零中频QPSK信号的高速解调算法及其FPGA硬件实现进行了介绍。

2021-03-19 17:43:12 11

11 AGM FPGA之AG10K 系列的开发建议(连载二)

2021-12-05 17:21:14 27

27 对速度要求;后者虽然可以实现高速传输,但DSP价格过于昂贵。而利用FPGA和USB接口芯片结合的方案,具有功耗低、时钟频率高、速度快、效率高、组合形式灵活等特点,是单片机和DSP所无法比拟的。 系统总体方案 根据本系统要实现的功能,该系统硬件

2023-10-06 14:55:02 2955

2955

电子发烧友App

电子发烧友App

评论