【安全算法之MD5】MD5摘要运算的C语言源码实现

2022-09-12 16:32:30 5009

5009

代替,比如可以先用除法运算获得整数部分,然后用求余运算获得余数,再对余数进行运算。2、本例实现一个除法运算,所得上的整数部分送P1口显示,小数部分送P0口显示。3、实现方法,本例计算101除以2的结果

2012-03-22 10:47:30

51单片机中B寄存器是SFR,B寄存器仅在乘法、除法指令中为寄存器寻址,在其它指令中为直接寻址。那么它只有在乘除法时看做特殊功能寄存器,其他指令看做通用寄存器。但是直接寻址是访问特殊功能寄存器的唯一方式,为什么B寄存器在乘除法指令中是寄存器寻址?

2019-01-01 09:45:47

使用c6678进行浮点除法运算的时间测试的时候(使用clock),发现(使用c6678evm板)运行时间很长,运算时间达到七百多个时钟周期。请问是什么原因?c6678本身的浮点除法能达到什么样的运算速度呢?

2018-06-21 13:49:31

您好:

不知道TI有没有矩阵矢量算法库,我现在想要实现复数矩阵间的加减乘除,开方,共轭等运算。如果有收费的,我也可以买。

谢谢!

2018-06-21 00:36:43

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8这三种芯片的区别,用哪种芯片较好?买哪种芯片的学习开发板较好? 谢谢大家的求解!!!

2013-07-21 19:46:34

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8这是三种芯片的区别,用哪种芯片较好?买哪种芯片的开发板较好?谢谢大家的求解啊!!!

2013-07-21 19:58:40

EP2S130F1508C4国宇航芯代理EP2S180F1508C5N国宇航芯代理EP2S130F1020C3N国宇航芯代理EP2S130F1020I4N国宇航芯代理EP2S130F1020C4国

2019-09-05 11:36:09

标志实现不可恢复的加-减除法运算,运行的结果存在R3中。如果要做有符号除法,首先应执行DIVS一次,从而得到商的符号位。然后多次执行DIVQ得到商。【 指令周期 】 2 + RW (DIVS) / 3

2009-09-21 09:26:57

实现两个二进制除法运算,并在八个七段数码管上进行显示实现两个二进制除法运算,并在八个七段数码管上进行显示实现两个二进制除法运算,并在八个七段数码管上进行显示

2013-11-01 20:34:01

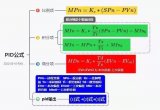

、整数算法

而实际应用时,为了避免低速的浮点运算,所以需要整数算法。

注意到系数都是3位精度的没有,我们可以将它们缩放1000倍来实现整数运算算法:Gray = (R*299 + G*587

2024-05-22 19:02:32

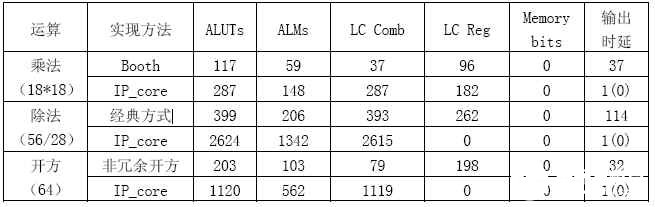

的要求和FPGA芯片设计的灵活性结合起来,采用Alter公司的CycloneⅡ系列FPGA芯片EP2C35F672C8,用VHDL语言编程,最后分别使用Quartus Ⅱ和Matlab软件开发工具验证实现

2010-05-28 13:38:38

在使用verilogHDL编程数据运算时使用了乘除运算不知道会出错不,求指导

2020-05-27 14:20:31

] signal_b;需要注意一点,FPGA将所有有符号数视为二进制补码形式,运算的结果同样为补码。再来看看除法器IP核配置界面。总共就两页,非常简单。需要重点关注的有三个地方:1 算法实现结构

2018-08-13 09:27:32

Newton-Raphson算法

Newton-Raphson算法采用乘法来代替除法运算,即a/b=a(1/b),基本原理如下:

已知曲线方程f(x),我们在xn点做切线,求xn+1

首先我们

2025-10-24 07:53:47

RISC有没有乘除法指令呢?

2023-02-27 13:59:57

求助!STC12C5A60S2无法实现开平方算法(sqrt函数),以及atan2和asin怎么办?我已经包含了相关的头文件了,但是编译通不过。

2020-05-20 09:07:38

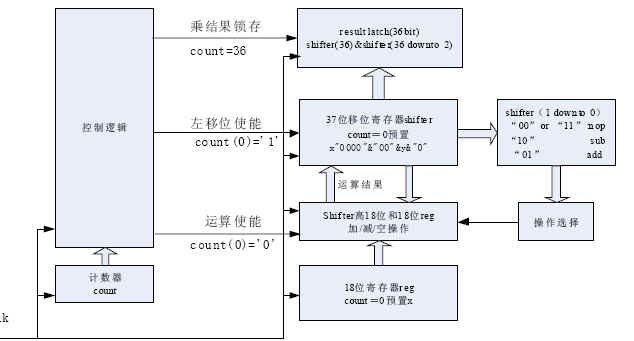

首先我们知道,对于e203的乘除法器,为了实现低功耗,低面积、高资源利用率,乘除法过程复用了alu数据通路,没有设计单独的乘除法器。

其中乘法采用基4booth编码得到部分积,并通过移位相加,复用

2025-10-24 06:37:44

e203内部除法操作使用加减交替迭代法进行运算,除几个特殊运算外,正常的除法操作需要33个周期才能输出运算结果,极大程度地影响了系统的性能。我们对e203的除法器进行了新的算法实现并改进。目前高性能

2025-10-22 07:13:48

e203内部除法操作使用加减交替迭代法进行运算,除几个特殊运算外,正常的除法操作需要33个周期才能输出运算结果,极大程度地影响了系统的性能。我们对e203的除法器进行了新的算法实现并改进。目前高性能

2025-10-22 06:11:27

本帖最后由 liuliwei25 于 2016-1-28 14:44 编辑

请问labview如何实现加减乘除的混合运算,如图所示。谢谢

2016-01-28 14:29:47

数问题。因此,深入理解芯片所基于的算法是国产自主研发的关键。任何算法都是由加减四则运算、滤波器、特殊信号发生器等基本数学方法构成的,熟练掌握这些方法是实现

算法的基础。如果说复杂算法是大厦,那么

2024-11-21 17:05:28

的乘法器和除法器设计,在不同专业芯片领域有着广泛应用的数字信号发生器、复数求模求角度运算器、普通滤波器、E△ADC中使用的抽取滤波器、基于 E△结构实现的小数倍分频器、CRC校验器等。每个电路均给出了算法

2024-11-21 17:14:02

蜂鸟E203内核内建多周期硬件乘除法器

MDV 模块只进行运算控制,并没有自己的加法器

加法器与其他的ALU子单元复用共享的运算数据通路,硬件实现非常节省面积,是一种相当低功耗的实现方式,但

2025-10-27 07:16:56

的C51定点运算库,在乘除相关指令方面,没能充分运用中颖SH79/88/89/F51系列自带的 16位X8位硬件乘法器 和 16位/8位硬件除法器,网上搜了一下,中颖SH79/88/89/F51系列有个

2011-11-22 19:26:19

为什么MCU中的除法运算要比乘法运算的效率低

2023-10-09 07:45:11

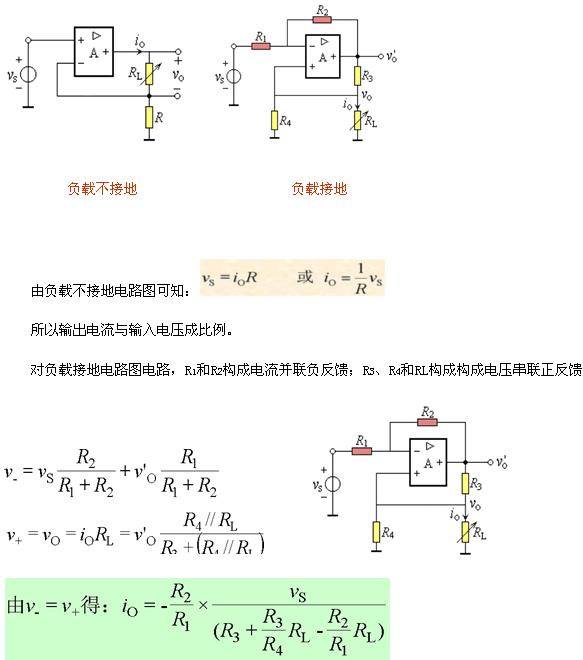

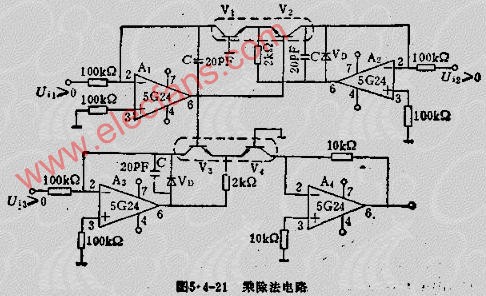

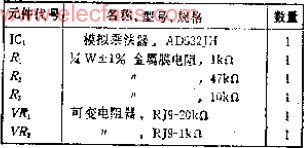

这个是论坛里的一个乘除法电路,但是我不能明白为什么这个电路可以实现U1*U3/U2,并且误差很小。我自己搭建过一个乘除法电路,也是想实现U1*U2/U3,但是结果误差比论坛里的这个电路大。求大神帮我

2019-12-28 17:06:07

最近,做项目时,需要使用开发运算,但是调用标准c库的sqrt函数,发现该函数有2k多大小,当然执行时间也就很长了,根本不适合单片机的运算。故而,网上找了一个简化的算法,编译出来后,只有不到100字节

2021-11-24 08:07:47

:elecfans123)领取书籍进行评测,如在5个工作日内未联系,视为放弃本次试用评测资格!

《从算法到电路——数字芯片算法的电路实现》 是一本深入解读基础算法及其电路设计,以打通算法研发到数字IC设计的实现屏障,以及

2024-10-09 13:43:17

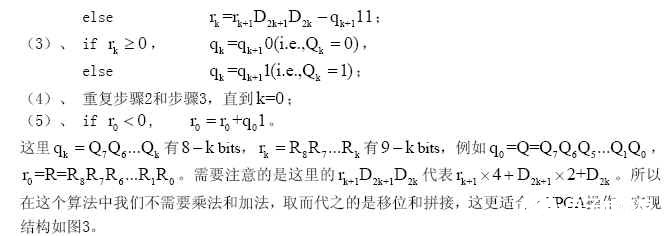

它不需要浮点运算,也不需要乘除运算,因此可以很方便地运用到各种芯片上去。我们先来看看10进制下是如何手工计算开方的。先看下面两个算式,x = 10*p + q(...

2021-07-15 07:03:45

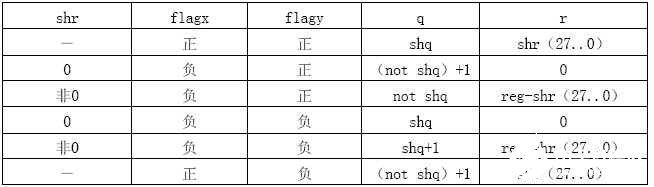

主要的除法运算优化方法是使用基本的SRT-4算法进行除法运算,以模拟SRT-64除法运算:

为了减少时钟周期并提高运算频率,极大基法是SRT算法中提出的一种方法。在该方法中,每次迭代的位数取决于所

2025-10-23 07:23:18

本设计方案采用了一种改进的快速中值滤波算法,成功地在Altera公司的高性能Stratix II EP2S60上实现整个数字红外图像滤波,在保证实时性的同时,使得硬件体积大为缩减,大大降低了成本

2021-04-23 06:00:55

指令流水线的优化、针对寄存器分配进行的优化等。 ARM在硬件上不支持除法指令,编译器是通过调用C库函数来实现除法运算的,有许多不同类型的除法程序来适应不同的除数和被除数。但直接利用C库函数中的标准

2011-07-14 14:48:47

的缺点,能做到真正意义上的实时权向量提取。在这些处理方式中一般采用标准Givens旋转来实现QR分解或MQR分解,标准Givens旋转包含开方和除法运算,保证足够精度及稳定性的开方和除法运算的运算量相当大

2020-11-23 09:15:32

和fifo_dat aiQ可以发现两者并不完全一样,这时由于FPGA编程为定点数作造成的。4 结论该方法基于StratixⅡ系列的EP2S90 FPGA芯片实现了数字稳定校正功能,消除了发射信号的相位

2015-02-05 15:34:43

高端Stratix II系列芯片,型号为:EP2S系列EP2S60-F1020C5, 具有逻辑单元60,440, RAM总数318024Kb,DSP blocks 36个,18-bit × 18-bit

2012-06-13 11:39:49

高端Stratix II系列芯片,型号为:EP2S系列EP2S60-F1020C5, 具有逻辑单元60,440, RAM总数318024Kb,DSP blocks 36个,18-bit × 18-bit

2012-06-13 12:01:23

本文主要描述如何使用恢复算法来实现开平方运算。

简介

开平方的恢复算法其实与除法的恢复算法十分相似。首先我们假设X为输入的操作数(它应该为正数),而他的平方根可以表示为Qn=0.q1q2

2025-10-24 13:33:38

器可以运用各种不同算法来实现除法运算,例如:SRT,Newton-Raphson等。对于不同应用场景,需要选择最适合的算法,从而达到最优的处理器性能表现。

三、总结

蜂鸟E203内核乘除法器的优化是提高

2025-10-24 06:47:29

如何在ALTERA公司的Quartus II环境下用VHDL、Verilog HDL实现设计输入,采用同步时钟,成功编译、综合、适配和仿真,并下载到Stratix系列FPGA芯片EP1S25F780C5中。

2021-04-15 06:19:38

怎么用stm32进行开方运算

2019-10-09 04:35:58

了解或想开发无人机的朋友肯定绕不过姿态解算这茬,花点时间去了解它们原理并不难,这里提供两个原理链接供大家参考:四元数表示旋转的理解四旋翼姿态解算原理而在代码实现方面,我这里写好了姿态解算算法模块供大家学习和参考。

2022-01-11 07:06:21

的四种单片机常用开方根算法: 对于拥有专门的乘除法指令的单片机,可采用以下两种方法: 1、二分法 对于一个非负数n,它的平方根不会小于大于(n/2+1)(谢谢@linzhi-cs提醒)。在[0

2020-11-26 17:01:04

- 例程2,ADC滤波算法04 - 总结1us的误差,足矣改变这个世界 ————CSDN根号301 - 为什么整数位移比乘除法高效 首先,整数位运算要比乘除法要高效。如果学过计算机组成...

2021-12-24 07:33:48

的,和整数长度一致。

2.浮点运算指令实现:蜂鸟E203可以通过在EXU内添加一个与ALU平行的模块:浮点处理单元(float point unit),专用于处理浮点指令。该单元可以更高效地执行浮点数计算

2025-10-22 07:04:49

一起配置硬件除法器和硬件开方器。除法和开方是非常消耗时间的运算,而在电机控制算法中,乘除法和平方根运算在电机运算中使用频率较高。为了提高MCU的工作效率,MM32SPIN2x了内嵌硬件32bit硬件

2018-11-30 09:23:40

编制程序实现计算器功能,包含加减乘除运算。

2016-04-15 22:38:06

小弟最近在用STM32F030C6T6芯片完成电机的SVPWM控制。现在发现算法中,运行速度很慢。打算将所有的除法运算改成移位运算。一般的,无符号数的右移几位和除以2的几次幂是等效的。但是,在STM32里面,有符号数的右移也和除法运算等效吗?

2019-01-22 08:14:26

请问altera芯片EP2C5T144C8和C8N的区别? 谢谢

2012-03-30 22:37:06

Boot到ram中,则除法、开方、sin、cos的执行时间变成2倍了。加法和乘法运算都正常。想不通啊,急急急,求大侠指点~

2018-10-18 10:40:05

六位四则运算计算器(8)算法实现加减乘除雾盈 2016-8-31 一、写在前面今天来讲计算模块,这个模块在我的计算器设计里不是核心项目,只是个计算功能。一般情况下,童鞋写加减乘除运算都使

2016-09-01 09:03:33

基FPGA Cyclone II_EP2C5 EP2C8的频率计

基FPGA_Cyclone_II_EP2C5/EP2C8的频率计

功能描述:按4*4键盘上的1,2,3...号按键可依次测出 25000000Hz ,12500000Hz ....的分

2008-11-30 12:17:01 87

87 在许多定点DSP芯片中,一般不提供单周期的除法指令;而在实际应用中,又常常要用到除法运算,因此如何利用简单的指令来实现除法是一个非常重要的问题。本文对定点除法算法

2009-04-16 14:03:07 48

48 Stratix II EP2S60 DSP Development Board

The Stratix® II EP2S60 DSP development board

2010-04-07 10:54:27 53

53 高精度的乘除法和开方等数学运算在FPGA实现中往往要消耗大量专用乘法器和逻辑资源。在资源敏感而计算时延要求较低的应用中,以处理时间换取资源的串行运算方法具有广泛的应

2010-07-28 18:05:14 37

37 对TMS320C3X中浮点数除法的实现方法进行了详细讨论,并给出汇编子程序。浮点数除法首先利用牛顿迭代法求出除数的倒数,然后再与被除数相乘,从而得出结果。该设计思想已经应

2010-08-05 16:34:51 17

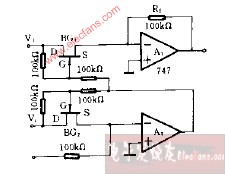

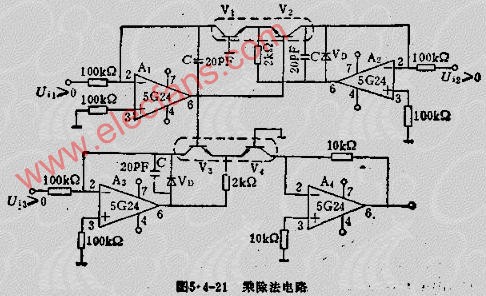

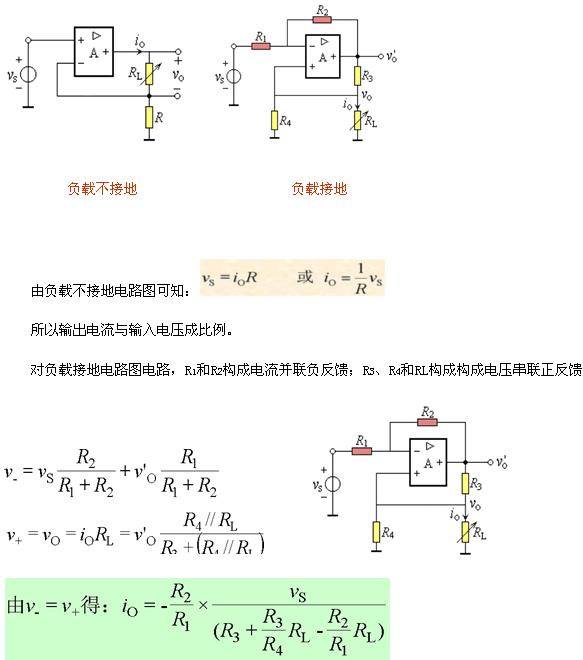

17 模拟乘法器在运算电路中的应用

8.6.1 乘法运算电路

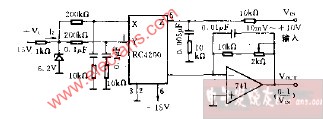

8.6.2 除法运算电路

8.6.3 开方运算电路

2010-09-25 16:28:45 146

146 针对Altera Stratix IV EP4SGX360和EP4SGX530器件的电源参考设计,具体电路如下图:

2010-12-12 10:37:52 64

64 针对Altera Stratix IV EP4SGX70和EP4SGX110器件的电源参考设计,电路图如下:

2010-12-12 10:43:38 41

41 乘除运算电路

基本乘除运算电路,乘法电路

乘法器符号

2008-01-17 12:54:12 3214

3214

乘除运算电路图

2009-07-17 11:26:22 547

547

除法运算电路图

2009-07-20 12:10:07 1027

1027

实现模2除法的线路 循环校验码的核心逻辑线路是实现模2除的线路。按照前面介绍的方法,可将模2除的步骤分解归纳为两种操作:如果被除数或者余数最高位的值为0

2009-10-13 16:57:21 7046

7046

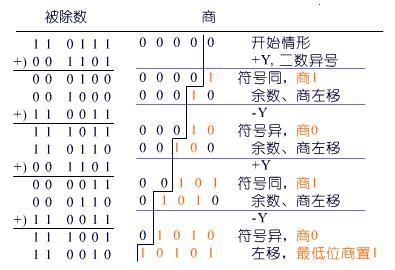

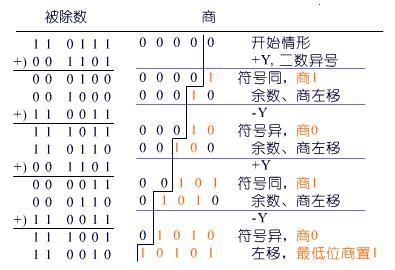

定点补码一位除法的实现方案 与补码乘法类似,也可以用补码直接完成除法运算,即用 [X]补/[Y] 补 直接求得[X/Y]补 。补码除法的规则比原码除

2009-10-13 22:58:39 3829

3829

Altera推出业界密度最大的Stratix IV EP4SE820 FPGA

Altera宣布,40-nm Stratix IV E FPGA高端密度范围增大到业界领先的820K逻辑单元(LE)。Stratix IV EP4SE820 FPGA是业界同类产品中密度最大

2009-11-11 16:50:00 1079

1079 二进制数值数据的编码与运算算法

一、原码、反码、补码的定义

1、原码的定义

2、补码的定义

2010-04-15 14:42:03 3408

3408 除法器对数运算电路的应用

由对数电路实现除法运算的数学原理是:

2010-04-24 16:07:27 3082

3082

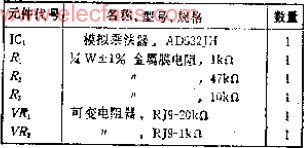

乘除法电路

图5.4-21是乘除法运算实用电路之一。

1、A

2010-04-26 16:11:49 17164

17164

用于比率计算的除法运算电路

电路的功能

本电路是用X除输入信号Z

2010-05-08 15:29:01 2003

2003

S2C Inc.宣布在Altera公司的40-nm StraTIx IV现场可编程逻辑闸阵列(FPGA)基础上发布其第四代快速SoC原型工具,即S4 TAI Logic Module。

Dual S4 TAI Logic Module因配备两个Stratix IV EP4SE82

2010-07-01 08:50:39 1327

1327 介绍一种在 8096 /96 系列单片机上实现的单精度 浮点数 快速除法。该算法采用了预估一修正的数值计算方法,并充分利用了16 位CPU 中的乘除法指令,计算速度快、精度高,有很强的实用

2011-06-03 16:47:06 93

93 FPGA实现铁轨检测算法设计_本文将阐述如何用乘法运算代替除法运算,以及如何使除法的次数最少化。

2011-10-05 16:37:19 12169

12169

EP2C5T144C8-FPGA开发板采用Altera公司推出的CYCLONEⅡ系列芯片EP2C5T144C8芯片作为核心处理器进行设计,CYCLONEⅡ系列芯片可以说是目前市场上性价比较高的芯片,比第一代的EP1C6或者EP1C12等芯片

2011-12-06 10:24:54 671

671 基于FPGA的开方运算实现 ,的技术论文

2015-10-30 10:59:01 5

5 14.2 除法运算 因为ARM体系结构本身并不包含除法运算硬件,所以在ARM上实现除法是十分耗时的。ARM指令集中没有直接提供除法汇编指令,当代码中出现除法运算时,ARM编译器会调用C库函数(有符合

2017-10-17 17:22:29 5

5 本文采用Altera公司Stratix II系列的EP2S90F1508C3芯片,以Quartus II 8.1为开发环境[4],采用硬件描述语言VHDL进行SM3算法的FPGA实现。SM3算法实现

2017-11-24 15:33:59 3108

3108

为确保安全苛求系统中程序执行的正确性,研究人员将差错控制理论用于对计算机指令进行编码,但由于编码大多涉及模运算,导致复杂度大量增加,应用于实时系统有困难。针对复杂度问题对delta码的乘除法运算算法

2017-12-04 16:44:29 0

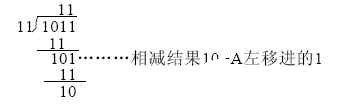

0 单片机中的除法也是二进制的除法,和现实中数学的除法类似,是从被除数的高位开始,按位对除数进行相处取余的运算,得出的余数再和之后的被除数一起再进行新的相除取余的运算,直到除不尽为止,因为单片机中的除法是二进制的,每个步骤除出来的商最大只有1,所以我们实际编程时可以把每一步的除法看作减法运算。

2018-05-31 08:51:02 6660

6660

乘除法很消耗CPU资源,查看汇编代码会发现,一个乘除法运算会编译出10几甚至几10行代码。如果是乘以或除以2的n次方,可以用>来实现,这种移位运算在编译时就已经算好了,所以代码很简洁,运算效率就高。但是需要特别注意运算符的优先级问题。

2018-06-26 16:36:27 7965

7965 开方运算作为数字信号处理(DSP)领域内的一种基本运算,其基于现场可编程门列(FPGA)的工程实现具有较高的难度。本文分析比较了实现开方运算的牛顿-莱福森算法,逐次逼近算法,非冗余开方算法3种算法

2020-08-06 17:58:15 6

6 、加减法、判断和循环实现,因为它不需要浮点运算,也不需要乘除运算,因此可以很方便地运用到各种芯片上去。我们先来看看10进制下是如何手工计算开方的。先看下面两个算式,x = 10*p + q (...

2021-11-11 13:36:10 1

1 汇编实现多字节乘除法乘法单片机的乘法本质是二进制的乘法,而乘法本身是通过加法实现的。多字节的乘法其实就是移位做加法。例如7x11,用二进制竖式表示如下图:可以看到,其实就是判断乘数的每一位是1还是0

2021-11-15 17:21:03 21

21 最近,做项目时,需要使用开发运算,但是调用标准c库的sqrt函数,发现该函数有2k多大小,当然执行时间也就很长了,根本不适合单片机的运算。故而,网上找了一个简化的算法,编译出来后,只有不到100字节

2021-11-16 15:51:01 7

7 FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会。若其中一个操作数为常数,可通过简单的移位与求和操作代替,但用硬件逻辑完成两变量间除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成。因此FPGA实现除法运算并不是一个“/”号可以解决的。

2022-04-27 09:16:03 9041

9041 C语言程序其实用代码将算法的加减乘除实现一下就可以了。

2023-07-23 16:24:44 1726

1726

用移位来解决乘除法问题 a =a* 4 ; b =b/ 4 ; 可以改为: a =a 2 ; b =b >> 2 ; 通常如果需要乘以或除以2的n次方,都可以用移位的方法代替。用移位的方法得到代码比

2023-11-21 11:25:41 1802

1802

电子发烧友App

电子发烧友App

评论