2022 年 4 月 14 日,中国北京讯 - 全球半导体解决方案供应商瑞萨电子(TSE:6723)今日宣布,率先推出符合PCIe Gen6严格标准的时钟缓冲器和多路复用器。作为业内先进的时钟

2022-04-14 15:33:49 1941

1941

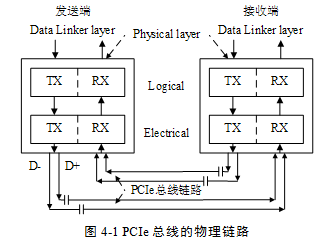

PCIe总线概述 随着现代处理器技术的发展,在互连领域中,使用高速差分总线替代并行总线是大势所趋。与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线,完成之前需要许多

2020-11-21 10:42:13 3562

3562

PCIe 时钟发生器的 PI6CG33xxxC 系列产品与 PCIe 时钟缓冲器的 PI6CB33xxxx 系列产品分别包含八个与九个装置,提供多样选择,例如输出数与输出阻抗。

2020-03-10 11:49:35 964

964 使用自己做的6678的板卡. PCIe参考时钟100MHz. 运行例程中的PCIe测试.pcie_phy_loopback. 当运行完 gpPCIE_app_regs->CMD_STATUS

2019-01-03 11:36:50

_int_cfg.number_tx_MSI = PCIE_16_MSI;这个结构体里面配置了MSI16这个中断向量。然后工程跑的是loopback模式。调用了这个语句KeyStone_PCIE

2018-06-21 03:49:49

1.PCIE的发送和接收数据本工程的目的是在XC7K325tffg的平台上实现pcie的数据发送和接收,速率8通道2.5GB/s,首先看下本工程的PCIE部分的结构:架构各个模块的作用PCIE部分

2019-12-26 10:46:09

1 PCIE基本概念1.1 PCIE拓扑架构图1.2 PCIE Switch内部结构图1.3 PCIE协议结构图2 PCIE枚举原理2.1 Type0&Type1配置头空间2.2 拓扑示例

2022-02-16 06:08:26

我想用C6657的PCIE接口扩展一个WIFI.

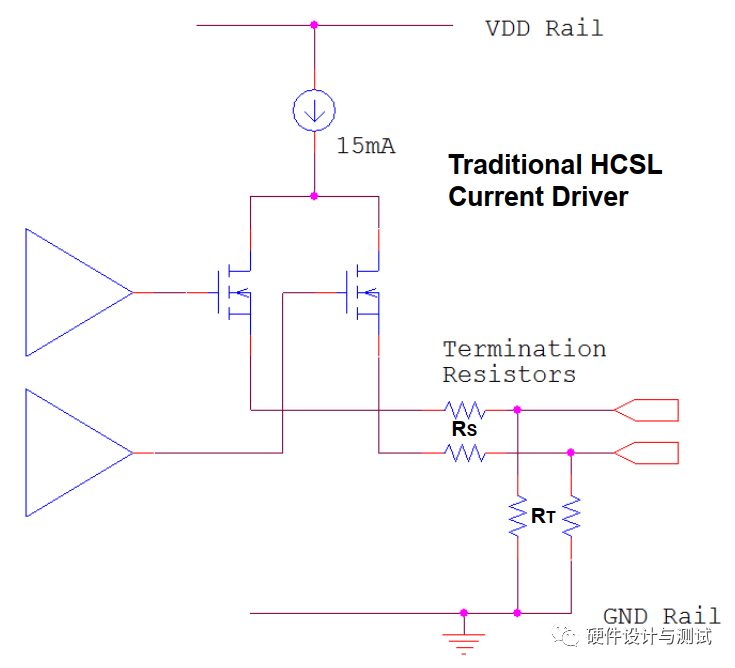

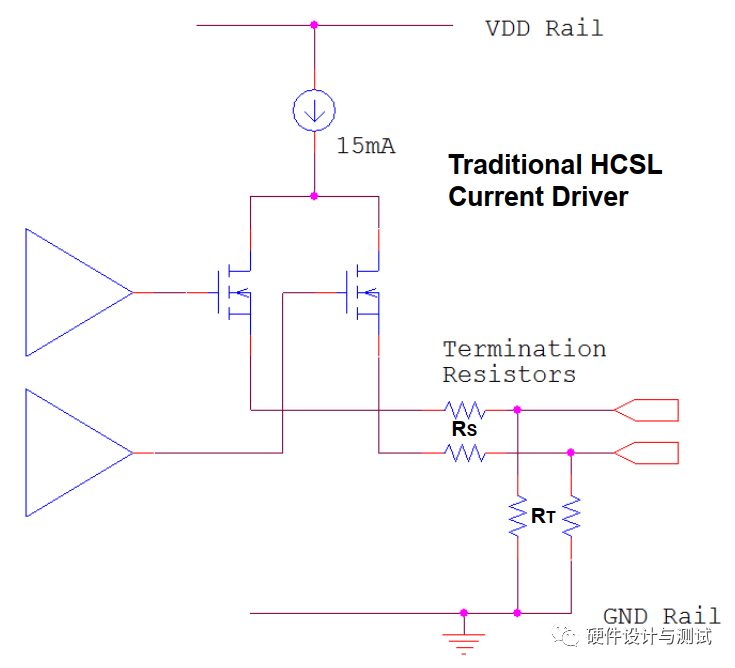

C6657的PCIE需要一个LVDS的参考时钟(PCIECLKP, PCIECLKN), WIFI芯片的PCIE需要一个HCSL的参考时钟

2018-06-21 18:45:06

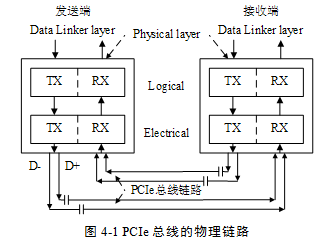

PCIe提供了一种可裁减高速串行I/O点到点的总线连接。PCIe的LAN是一个全双工的通道,由一对接收差分对和一对发送差分对构成。PCIe的带宽可以通过增减LANE数来调整。PCIe规范定义了x1

2019-06-03 07:09:56

”,简写PCIe。2、AC耦合电容:高速差分信号电气规范要求PCIe发送端串联一个电容,进行耦合。3、链路类型与差分信号数量:X1:1对时钟差分信号,1对收发差分信号,单面pin数18pi...

2021-11-11 08:05:11

PCIe总线概述随着现代处理器技术的发展,在互连领域中,使用高速差分总线替代并行总线是大势所趋。与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线,完成之前需要许多单端并行数据信号才能达到的总线带宽。PCI总线使用并行总线结构,在同一条总线上的所有外...

2021-07-29 07:07:06

串行外设接口 (SPI) 是微控制器和外围 IC(如传感器、ADC、DAC、 移位寄存器、SRAM等)之间使用最广泛的接口之一。SPI 是一种同步、全双工、主从式接口。来自主机或从机的数据在时钟上升

2018-10-25 16:32:48

刚入STM32 用了也有一段时间了,先做了中断,CAN,SPI。都是跟着网上的例子直接粘贴外设的初始化代码,看的大概能懂,但是时钟一直迷迷糊糊,不清不楚。 STM32为了实现低功耗,而设计的功能完善

2021-08-11 07:15:27

一文读懂DS18B20温度传感器及编程对于新手而言,DS18B20基本概念仅做了解,最重要的是利用单片机对DS18B20进行编程,读取温度信息,并把读取到的温度信息利用数码管,LCD1602或者上位

2021-07-06 07:10:47

RTC是什么?RTC芯片有哪些应用?RTC芯片的硬件结构是由哪些部分组成的?RTC实时时钟的作用是什么?

2021-08-24 07:39:34

一文读懂中断方式和轮询操作有什么区别吗?

2021-12-10 06:00:50

掌握每种电路结构的工作原理与基本特性。一、20种开关电源拓扑对比常见的基本拓扑结构:■ Buck 降压■ Boost 升压■ Buck-Boost 降压-升压■ flyback 反激■ Forward 正激

2022-04-07 10:56:48

一文读懂什么是NEC协议?

2021-10-15 09:22:14

一文读懂传感器传感器在原理与结构上千差万别,如何根据具体的测量目的、测量对象以及测量环境合理地选用传感器,是在进行某个量的测量时首先要解决的问题。当传感器确定之后,与之相配套的测量方法和测量设备也就

2022-01-13 07:08:26

一文读懂如何去优化AC耦合电容?

2021-06-08 07:04:12

一文读懂接口模块的组合应用有哪些?

2021-05-17 07:15:49

`电感器是能够把电能转化为磁能而存储起来的元件。电感器的结构类似于变压器,但只有一个绕组。电感器具有一定的电感,它只阻碍电流的变化。如果电感器在没有电流通过的状态下,电路接通时它将试图阻碍电流流过它

2018-09-20 11:34:20

要了解它们的主要参数。一般情况下,对电阻器应考虑其标称阻值、允许偏差和标称功率;对电容器则需了解其标称容量、允许偏差和耐压。一文读懂电阻和电容的不同 电阻器和电容器的标称值和允许偏差一般都标在电阻体

2017-11-14 10:25:25

SI53159-EVB,用于PoE无线接入点的100至210MHz时钟发生器评估板。 Si53159是一款九端口PCIe时钟缓冲器,符合PCIe Gen1,Gen2和Gen3标准

2020-08-27 12:20:38

一篇读懂无线充电技术(附方...

2021-09-14 06:00:53

本帖最后由 人间烟火123 于 2018-6-15 09:30 编辑

如题,PCIe Spec是允许EP使用自己的时钟的,不知道8168 可否?不然,就必须要改动硬件。

2018-06-15 07:41:57

查过mini pcie的信号引脚定义,有52个信号(大多引脚无用),X1 LANE 的情况,查看飞思卡尔或INTEL处理器的设计资料,关于这个应用除了主要 的差分收、发和差分时钟信号之外还需要额外

2017-11-29 11:50:51

嗨,在ML605设计中,信号“PCIE_250M_MGT1_P / N”从器件“ICS874001”驱动到PCIe MGT参考时钟。根据以下链接中给出的相位噪声值,http

2020-06-08 15:30:33

我正在使用 i.MX8M Plus。使用 pcie 时,外部时钟参考运行良好。但是当涉及到内部时钟参考时,它变得很奇怪。root@tek3-imx8mp:~# dmesg |grep -E

2023-03-22 06:59:51

你好

作为我们在 ls1028 上努力的一部分

我们通过 pcie 将自定义 fpga 连接到 M.2 连接器(通道 C/2 - j16)

相关uboot日志:

U-Boot

2023-05-09 12:00:30

时钟系统为硬件系统的各个模块提供时钟信号,就像人的脉搏心跳一样不可或缺,而stm32的结构较为复杂,不同的硬件可能对时钟信号有不同的要求,因此在系统中设置多个振荡器,分别提供时钟信号,实际中经常从一

2022-01-11 07:31:55

最近将xilinx官方PCIe end point例子下到VC709中,插上电脑主板时没有任何反应,通过分析原因,发现主板提供的差分时钟在经过IBUFDS_GTE2后无输出时钟(该时钟用于PCIe核

2016-04-08 16:47:28

个典型的小型应用网关不需要各种I/O接口。尽管如此,NUC还是包含了一个PCIe插槽,并提供了一个可用的插头,可以通过它访问USB、SMBus以及电源和地。来源:网络,如侵删

2018-10-01 22:26:01

使用VTT电源。一般情况下,DDR的数据线都是一驱一的拓扑结构,且DDR2和DDR3内部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到较好的信号质量。DDR2的地址和控制信号线如果是多负载的情况下

2018-08-09 22:09:18

的主要参数。一般情况下,对电阻器应考虑其标称阻值、允许偏差和标称功率;对电容器则需了解其标称容量、允许偏差和耐压。一文读懂电阻和电容的不同电阻器和电容器的标称值和允许偏差一般都标在电阻体和电容体上,而在

2017-11-14 15:43:40

COF结构智能屏 单独强大的51系统框架 资源充足,频率高。我对原来工业控制加热设备部分简化一下程序移植,基本达到目的。 实现工业控制加热设备等功能。硬件框架如上图所示,硬件部分基于 迪文COF结构智能

2022-03-31 17:34:45

是将PCIe参考时钟更改为引脚Y4,Y3与ucf文件中的默认P4,P3引脚。我怀疑GTP_DUAL_X0Y4,X0Y3磁贴在X4,X1实现中没有接收时钟。 (我无法让一个LED闪烁,以便

2019-08-15 07:47:42

开发板测试:1、 安装windrive 2、LED状态显示 3、测试读写 PCIE开发板介绍:1、原理图介绍 PCIE TLP协议介绍:1、分析存储器写报文结构 2、分析存储器读报文结构 PCIE

2022-02-14 09:50:22

example例程。紫光的PCIE IP虽然没有像xilinx那样可以直接使用Block Design设计,但是仔细读一遍官方例程的DMA模块,进而开发自己的东西,还是能够很好用起来紫光的PCIE

2023-11-17 14:35:30

小弟最近在研究PCIE的系统结构。有一点想不明白。如果一个CPU外挂一个系统内存DDR,同时一片FPGA通过PCIE接口连接CPU,CPU做为Host主桥,FPGA做为PCIE设备。那么根据PCIE

2016-04-06 16:24:36

本帖最后由 eehome 于 2013-1-5 10:01 编辑

1.一个pciex16插座包含16条pcie通道能拆分使用么或者扩展么 比如构成两个独立的pciex8接口如果能,两个能同时

2012-10-19 00:57:16

的,而且输入噪声与输出噪声无关。缓冲器的抖动输出可通过该公式计算: 。LMK00338 是一款超低附加抖动 PCIe 时钟缓冲器。对于第 3 代 PCIe 应用而言,一般具有 30fs rms 的附加

2018-09-17 16:12:25

如何读懂一份datasheet文档

2017-11-05 14:57:22

学习硬件的第一节课:学习读懂原理图读懂原理图对嵌入式软件工程师和程序员尤为重要。在深入细节之前请注意,对所有的嵌入式设计人员来说、能懂得硬件工程师创建和使用的来描述其硬件设计的原理图和符号是非

2021-12-20 07:14:36

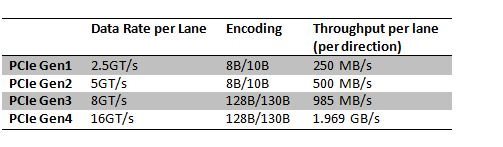

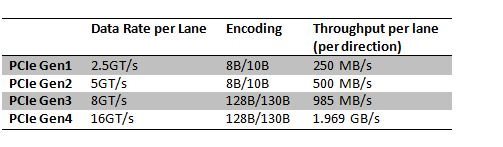

PCI Express® (PCIe®) 是一项业界领先的标准输入/输出 (I/O) 技术,是服务器、个人电脑以及其它应用中最常用的 I/O 接口之一。该标准多年来不断发展,以适应更高的数据速率

2022-11-22 08:04:25

错误的路径约束吗?2. ILA能否以200Mhz或250Mhz的工作频率工作?3. MMCM的输出是否构成一个自由运行的时钟?因为从ipcorem出来的user_clk源于我相信的PCIe时钟。4.

2019-09-25 09:26:14

PCI Express (PCIe)是嵌入式和其它系统类型的背板间通信的一个非常理想的协议。然而,在嵌入式环境中,背板连接器引脚通常很昂贵。因此,采用点对点连接的星型结构的PCIe时钟分配方案就变得

2019-09-26 07:56:41

PCI Express (PCIe)是嵌入式和其它系统类型的背板间通信的一个非常理想的协议。然而,在嵌入式环境中,背板连接器引脚通常很昂贵。因此,采用点对点连接的星型结构的PCIe时钟分配方案就变得

2019-08-30 06:54:47

如何优化PCIe应用中的时钟分配?

2021-05-24 06:44:45

。准备用ARM11来作为移植linux的平台现在在做什么:linux的内核太复杂,牵扯到很多数据结构,我还是刚上大三的本科生,很多数据结构得自己补习。给自己的短期目标就是:读懂一个轻量级的操作系统内核

2014-09-19 13:01:51

。准备用ARM11来作为移植linux的平台现在在做什么:linux的内核太复杂,牵扯到很多数据结构,我还是刚上大三的本科生,很多数据结构得自己补习。给自己的短期目标就是:读懂一个轻量级的操作系统内核

2014-09-19 13:08:39

SI52147-EVB,用于PoE无线接入点的时钟发生器评估板。 Si52147是一款符合PCIe Gen1,Gen2和Gen3标准的9端口PCIe时钟发生器

2020-08-27 14:27:11

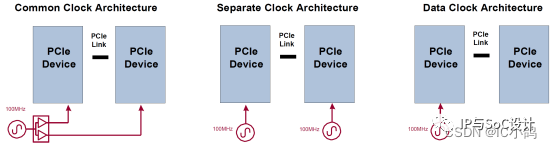

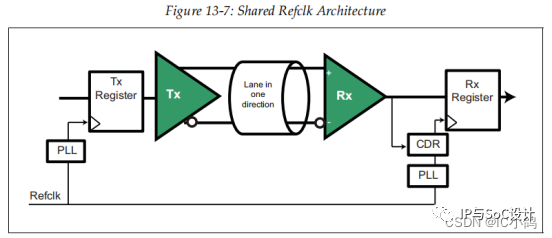

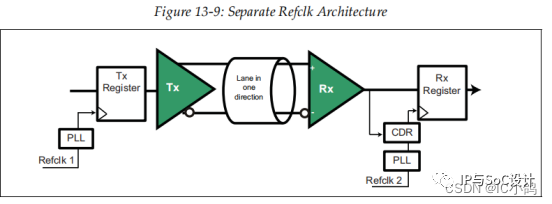

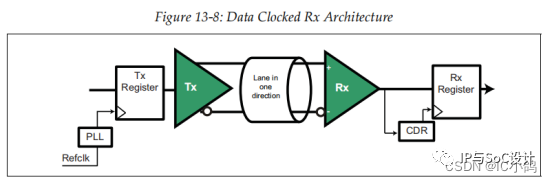

问题描述及复现步骤:PCIE通常采用Common REFCLK Rx Architecture (CC):PCIE Separate Refclk Architecture:请问3588Q pcie3.0 RC和EP端是否支持采用独立的REFCLK时钟。如果支持,有没有特殊要注意的地方。

2023-02-07 15:13:55

我们的设计利用了PCIe内核,该内核遇到了一些时序错误。为了确保设计得到适当的约束,我一直在审查所有输入/输出延迟,输入抖动和系统抖动限制。在我们的设计中,PCIe时钟源是125MHz振荡器。我无法

2020-08-04 10:31:33

PCI Express是一种高性能互连协议,被广泛应用于网络适配、图形加速器、网络存储、大数据传输以及嵌入式系统等领域。文中介绍了PCIe的体系结构,以及利用Altera Cyclone IV GX

2019-05-21 09:12:26

一文读懂驻波比(VSWR)的常识及意义

2021-01-07 07:13:18

COF(chip on FPC)智能屏是基于迪文低功耗双核T5L0 ASIC,将整个智能屏核心电路放到液晶模组

2021-12-28 15:44:28

迪文T5L平台COB结构智能屏是基于迪文自主研发的高性价比双核T5L系列芯片,将整个智能屏核心电路放到PCB板子上,集成整合触摸屏(电阻触摸和电容触摸

2022-06-15 13:49:45

总线时钟结构科利登系统有限公司大部分并行总线和高速串行总线的区别主要在于发送端和接收端不同的同步方式。由于其很高的复杂性,总线时钟结构成为芯片架构的最主要

2009-12-19 15:25:48 17

17 PCIe授时卡时钟板卡支持多种参考输入和输出,可根据需求采用不同的组合为计算机系统提供高精度时间信息,同时也可对外授时。支持GPS/北斗、PTP输入、B码(DC)作为参考源,输出10M、B(DC)码

2024-01-09 13:28:11

Silicon Laboratories (芯科实验室有限公司)日前宣布扩展其PCI Express(PCIe)时钟发生器和时钟缓冲器产品组合。

2012-02-02 09:31:56 1395

1395 基于子树重构的三维时钟树拓扑结构优化_钱晨

2017-01-07 18:56:13 0

0 I DT公司多重市场时序产品部总经理Kris Rausch介绍说:“随着我们9FGL产品系列的发布,IDT公司的低功耗、高性能PCIe时钟发生器产品组合中增加了3.3V器件,所有这些产品都可以满足

2018-04-13 10:09:00 2291

2291 一个简化的PCIe总线体系结构如上图所示,其中Device Core and interface to Transaction Layer就是我们常说的应用层或者软件层。这一层决定了PCIe设备的类型和基础功能,可以由硬件(如FPGA)或者软硬件协同实现。

2018-04-21 09:21:13 5264

5264 LMK0033x是德州仪器(TI)推出的业界最低抖动的PCIe时钟扇形缓冲器。现在就让德仪的工程师向你介绍它的具体情况吧!

2018-06-13 11:52:00 4883

4883 本文档的主要内容详细介绍的是MINI PCIE座子接插件的结构原理图免费下载。

2020-08-10 08:00:00 23

23 具有 16 G 每秒传输 (GT/s) 的比特率。第 4 代的规范预计将在 2014 或 2015 年发布。

表 1:各代 PCIe 的数据吞吐量

随着数据速率的提升,参考时钟需求

2021-11-23 11:07:32 3237

3237

1 PCIE基本概念1.1 PCIE拓扑架构图1.2 PCIE Switch内部结构图1.3 PCIE协议结构图2 PCIE枚举原理2.1 Type0&Type1配置头空间2.2 拓扑示例

2021-12-17 18:29:51 26

26 PCIe 和网络时钟抖动测量之间的另一个显着差异在图 2 中并不明显。数字采样示波器 (DSO) 用于获取时钟周期或波形文件以计算 PCIe 时钟抖动,而不是 PNA。造成这种情况的主要原因是 PCIe 时钟支持扩频,而网络时钟不支持,而且从历史上看,PNA 一直无法使用正在扩频的时钟。

2022-05-05 15:50:44 4513

4513

xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 2592

2592 PCIe 协议指定标准的参考时钟为 HCSL 电平的 100 MHz 时钟,Gen1~Gen4 下要求收发端参考时钟精度在 ±300 ppm 以内,Gen5 要求频率稳定性 ±100 ppm。一颗性能优秀的参考时钟是整个PCIe系统成功的基础。

2022-07-08 14:19:16 5616

5616 如何优化 PCIe 应用中的时钟分配

2022-11-07 08:07:15 0

0 PCIe发展至今已经从最初的1.0升级到了6.0,但很多人对于PCIe只知其然而不知其所以然,小编今天就带大家一起来看一看。

2022-12-01 10:37:49 1025

1025 9ZXL1951D PCIe 时钟发生器评估板用户指南

2023-03-21 19:21:13 0

0 由PCI-SIG发布的PCIe板卡结构规范。Revision 4.0 Version 0.9.

2023-06-19 09:59:44 5

5 极景微发布超小封装PCIe5.0时钟发生器日前,极景微(UltraSilicon)宣布,推出两款支持PCIe5.0接口标准的1输出及2输出时钟发生器,分别为US6D101和US6D102。该芯片具有

2023-02-02 15:25:54 999

999

9ZXL1951D PCIe 时钟发生器评估板用户指南

2023-07-07 19:19:11 0

0 电子发烧友网站提供《PI6CDBL401B低功耗PCIe时钟芯片.pdf》资料免费下载

2023-07-25 14:41:49 0

0 的标准;PCIe时钟采用HCSL这个电平标准使RC(CPU)侧与EP(子卡)侧时钟,在不同生产厂家之间能够保持电平兼容。它需要串行33Ω电阻和驱动源端50Ω电阻下拉到地。HCSL为电流输出驱动,输出结构通过50Ω电阻器下拉接地的15mA开关电流驱动,标称信号摆幅750mV。

2023-09-15 14:39:54 2447

2447

一文读懂,什么是BLE?

2023-11-27 17:11:14 634

634

今天来聊一聊时钟树。首先我先讲一下我所理解的时钟树是什么,然后介绍两种时钟树结构。

2023-12-06 15:23:47 482

482 高性能20路PCIe时钟缓冲器新品推介SQ82100PCI-Express(PCIe)是一种高速串行计算机扩展总线标准,主要用于扩充计算机系统总线数据吞吐量以及提高设备通信速度。目前服务器

2023-12-20 08:19:38 240

240

电子发烧友App

电子发烧友App

评论