本教程是基于FPGA的cy7c68013a的USB双向通信实验。

2023-03-09 09:40:33 8786

8786

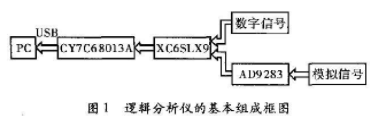

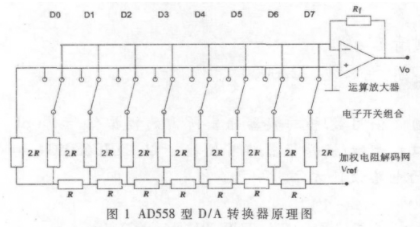

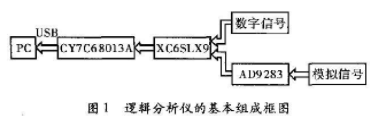

本项目采用CY7C68013A作为USB采集主控芯片,利用XC6SLX9作为数据通道的选择器件,选择输入到CY7C68013A的数据是来源于数字信号还是模拟信号经ADC模块之后的数字信号。由于该逻辑

2020-08-30 09:41:00 5638

5638

我们这边有个客户使用CY7C68013A,客户配置成slavefifo模式,PC端发送数据到FPGA时数据正常,FPGA发送数据到PC则会丢包或者收到的数据对不上。能否帮忙看下客户的配置是否正确。

2024-02-27 07:14:31

”【硬件连接】【实验现象】Ø 可通过上位机软件(USB_LED)来控制FPGA板子上的LED灯的亮灭;-----详细见:USB通信实验3. 附录说明3.1. 模块扩展开发本模块是围绕CY7C68013A

2016-03-28 14:41:24

下载固件后,使用BUS HOUND 抓数据,原端点4 BULK 可传输数据。(数据长度33字节)使用端点2发送数据,BUS HOUND出现参数错误,错误信息如下图所示!问题:CY7C68013A的端点

2017-02-22 14:00:08

各位高手: 我在做一个项目,母版FPGA主要是 Xilinx V5,子板USB2.0是CY7C68013A,USB采用异步slave fifo的bulk传输,主要过程是FPGA处理图像数据,经过

2014-06-28 10:31:09

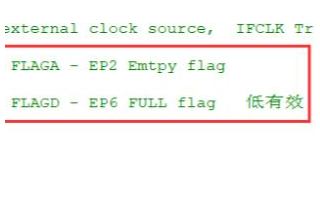

大家好IAM使用CY7C68013A与EP2设置为ISO UouTrink点。FIFO缓冲器的数据由外部同步主机(CPLD)读取。问题是,在随机的时候,FrasaDead配置为Actule低EP2空

2019-05-15 12:07:21

在我们最近的大规模生产中,我们发现该装置的小部分(2%)(使用CY7C68013A)没有。在一定条件下从EEPROM读取固件。只有当用户插入USB电缆时,才会发生这种情况。从设备到设备的电源,并快速

2018-09-14 14:54:50

我通过cycontrol将.IIC文件下载到24lc64中,但是再次启动时无法加载到CY7C68013A中,必须再使用cycontrol将hex文件下载到ram中才能使用,这是为什么?

2025-06-03 14:07:06

我通过cycontrol将.IIC文件下载到24lc64中,但是再次启动时无法加载到CY7C68013A中,必须再使用cycontrol将hex文件下载到ram中才能使用,这是为什么?

2024-02-28 06:52:36

CY7C68013A 的windows 10 驱动现在支持吗?如何获取?

2025-05-12 07:56:19

(24C128)时,CySalk无法识别我们的板。所以,我们剪掉一些代码,重试前面的步骤,哦……它可以识别我们的棋盘!我们对此一无所知!为什么?CY7C68013A限制了代码大小?但是,EZ-USB

2019-03-20 06:11:15

CYPRESS的USB外设控制器CY7C68013A是一款广泛应用于USB打印机,手机,存储设备,USB测试等多个领域的经典产品。该产品符合USB2.0协议规范,支持full speed和high

2015-03-01 16:38:30

你好,我需要在CY7C68013A USB高速微控制器上工作。我开始为小型测试应用设计我自己的硬件,因此我手中没有评估工具包。在开发Cy7C68013A控制器的应用程序时,应该使用编译器和开发IDE

2019-04-29 14:01:53

` 本帖最后由 IFLabs 于 2015-6-21 16:34 编辑

大家使用Cypress公司的USB接口芯片CY7C68013A觉得资源够用吗?我们知道CY7C68013A系列USB接口

2015-06-21 00:51:54

我希望在我的项目中由FPGA生成iFCLK,但是当我设置IFCONFIG= 0x03H,CPUCS= 0x10H时,CY7C68013A芯片不能工作。所以我希望你能告诉我IFCONFIG和CUPUC的价值。

2019-10-09 13:36:36

CY7C68013A使用外部24M晶体,这个负载电容一定要用12pF吗?我们用的24pF,测量时钟摆幅只有400mV,这个正常不?如果用12pF正常摆幅大概多大?

2022-07-27 14:51:35

一直在Windows系统下使用Cy7c68013A芯片,现在需要使用在Linux系统下,请教官方有Linux系统的驱动吗?或者有没有可以替代的芯片?谢谢各位

2019-10-06 10:15:30

大家好,USB芯片CY7C68013A和FPGA进行通信,从EP6读取512字节是正常的,但是读取2个字节失败(fpga端一直在发)Bulk IN failed,谢谢

2025-05-30 07:12:24

我现在正在使用CY7C68013A开发一个摄像头产品,首先PC上位机传输300K左右的配置数据传输给FPGA(通过CY7C68013A的端口6,端口位OUT),然后FPGA开始采集图像并把采集到图像

2024-02-27 08:00:01

您好,我使用这个CY7C68013A在我做的板上,但是当我把它连接到PC时,我得到“USB设备不被识别”。附在这台计算机上的一个USB设备出现故障,Windows无法识别它。“我尝试了来自

2019-03-04 16:12:52

亲爱的各位我们在项目中使用CY7C68013A芯片。它在高速模式下运行良好,但是当我们以全速模式和读取端点0x86-它返回PID停滞错误。在接通电源后,由于接收00000000,SETUP命令函数

2018-12-10 15:46:10

cy7c68013a的固件已经配置成异步slave模式,是否有MCU用IO口控制cy7c68013a通过数据总线来实现与PC的USB口通信,这样应用的示例程序或教程?

目的就是在现有的MCU系统中增加一个USB通信接口,或者您有其他的建议,非常感谢。

2024-02-27 08:14:49

cy7c68013a的datasheet好像很复杂

2012-11-21 14:37:44

cy7c68013a和FPGA采用同步slfifo模式通讯,当上位机使用control center发送2个字节时,FPGA收到数据正确,当发送4个以上字节时会出现头两个字节丢失,后两个字节重复的现象,百思不得其解?固件使用官网的slavefifo的固件未更改。

2024-02-28 08:25:09

cy7c68013a和FPGA采用同步slfifo模式通讯,当上位机使用control center发送2个字节时,FPGA收到数据正确,当发送4个以上字节时会出现头两个字节丢失,后两个字节重复的现象,百思不得其解?固件使用官网的slavefifo的固件未更改。

2025-06-03 10:44:01

fpga通过cy7c68013a将数据经过USB传输至电脑,采用slave FIFO模式 同步写入,每一次计划传输520字节的数据,我通过SLWR这个信号控制写入数据字节个数,现在发现每次电脑接收

2024-02-27 06:18:36

ADI提供许多锁相环芯片,也同时出售对应的评估板和评估板软件,他们的评估软件看上去非常方便,不需要编程,就可以生成我们想要的寄存器值,并写入。首先,构建我们自己的CY7C68013A芯片的最小系统,在ATF4158的评估板指南中有CY7C68013A芯片的最小系统,如下图

2019-07-18 07:46:33

我使用的是 FX2 CY7C68013A 芯片。 我知道 CyUSB.NET 库中有我需要的 LoadEEPROM 函数。 请问如何在 C++ 环境而不是 C#/CLR 环境中使用该函数? C++ 是否有类似的函数,或者我如何自己编写?

2024-05-31 06:59:19

cy7c68013a的固件已经配置成异步slave模式,是否有MCU用IO口控制cy7c68013a通过数据总线来实现与PC的USB口通信,这样应用的示例程序或教程?

目的就是在现有的MCU系统中增加一个USB通信接口,或者您有其他的建议,非常感谢。

2025-05-30 06:32:33

你好,Windows 10的CY7C68013A的驱动程序是否支持?如何获得?非常感谢。

2019-10-08 08:22:22

你好,只要我们已经有了产品的头…该产品有CyPress CY7C68013A(USB控制器),并在Windows上工作。我们正计划增加对Linux发行版的支持。关于这个要求的几个问题:1)我们有没有

2019-01-28 10:32:22

我想把这样使用 CY7C68013A 的GPIF 和 FIFO功能:

1. 两路数据传输,CY7C68013都作为从机接收数据

2. 每一路都数据格式为:1个clock pin,8个数据pin

3.

2025-06-03 13:35:24

我们最近尝试使用CY7C68013A-56LTXC捕获并行的8位MPEG TS,并将这些MPEG TS送到USB端口。为此,我们参考了设计FX2LPYDBMH THZTVTIGLE,并准备了我们自己

2018-11-23 15:11:22

指示灯都没有亮,但是OVER_RANGE指示灯亮了,请问这是什么原因呢?

再请教一个问题,使用wavevison5软件时,FPGA中的程序是在线加载的,CY7C68013A中的固件也是在线加载的吗?

2024-12-27 08:11:21

我想这样使用CY7C68013A的CLKOUT输出37.125KHz的时钟,

请问能输出这种频率吗?

如果能,怎么样才能输出这个频率呢?

如果不能,其它pin可以输出这个频率吗?怎样输出?

2025-06-03 10:05:55

标签:基于USB芯片CY7C68013A的上位机C基于USB芯片CY7C68013A的上位机C程序在国标《质量管理体系 基础和术语》GB/T19000—2008/ISO9000:2005中第

2021-08-06 09:58:59

你好,我是新的CY7C68013A,并尝试做例子BulkLoad开始。在我把BulkLoop.HEX加载到我的板的RAM之后,“USB控制中心”再也找不到板了。但我仍然可以通过Windows设备管理器找到我的板“CyPress FX2LP示例设备”。有人能帮忙吗?谢谢。NNI装置27.1 K

2019-10-24 10:04:54

CY7C68013A USB 微控制器的新手。 我打算在我的设计中使用这些 IC,但是,我不知道当 PCB 通过 USB 连接到笔记本电脑时,需要什么来访问该芯片或对其进行编程。 所以,

1. 我的笔记本电脑需要安装哪些软件或驱动程序才能使用 CY7C68013A 芯片?

2025-05-20 06:41:47

我应该如何使用 EZ-USB FX2LP CY7C68013A 开发大容量存储设备,我找不到允许在 FX2LP 上开发大容量存储设备的文档,请帮帮我,谢谢

2025-05-29 06:15:56

。但是,我发现丢弃的大小不是很大。因此,如果68013的FIFO大于2K(例如4K),则会更好。所以,我想知道“如何在CY7C68013A中扩展FIFO的数量和大小”。 以上来自于百度翻译 以下

2019-07-11 07:59:30

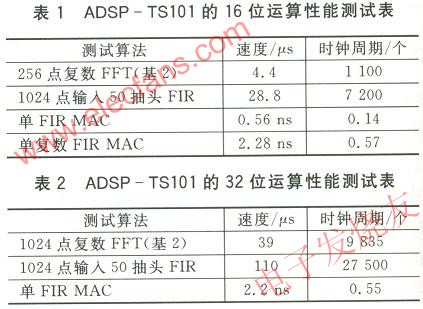

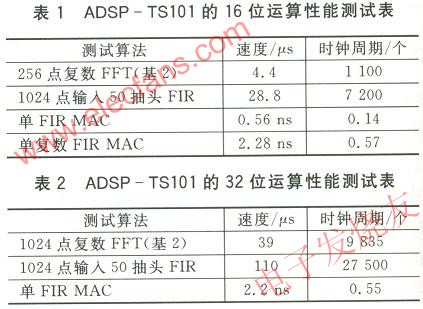

求一个解决系统中主处理器在较高工作频率300 MHz下稳定工作的问题,以及在两个主芯片之间和主芯片与数据存储芯片之间数据高速互联的问题,提高系统的性能,满足设计要求的基于ADSP-TS101高速信号处理系统。

2021-04-12 06:39:56

您好,我有一个问题,USB摄像头,使用芯片CY7C68013A 56PVXC:相机没有响应,当连接到PC & GT时,我替换了XTAL -没有变化。我在PCB上没有看到损坏的部件或轨道

2019-04-17 08:01:01

你好,我在CY7C68013A 56PIN CyPress USB控制器上工作。我没有使用开发板,而是为我自己的应用程序定制了设计。后来,我在某处读到56针不支持调试。对吗?有没有办法,我可以做任何

2019-05-05 06:32:42

我的高级工程师负责完成CY7C68013A的C代码,以便在AD ADAU1442 DSP与Windows XP系统之间的接口,然后是Android。所以,我必须接管并重新开始。这个CyPress

2019-03-21 07:59:51

USB2.0特点是什么CY7C68013A的主要特点求一中基于CY7C68013A的USB控制系统设计

2021-04-09 06:03:27

求CY7C68013A,问下芯片程序下载软件是什么

2012-12-22 18:21:31

求一个avalon总线和CY7C68013A的接口转换模块verilog代码

2014-05-15 13:06:30

本帖最后由 Razer 于 2013-10-17 10:11 编辑

FPGA+CY7C68013A,两个片子都没程序,觉得在无程序的情况下上电,插上USB数据线,如果线路正确,PC应该能反应出

2013-10-17 09:52:42

, FD15对应D3,但是问题是这块板子居然是工作的,照样可以成功的通过USB把程序下载到FPGA里面完成配置。这让人非常困惑。难道X2 (CY7C68013A)和Spartan 6的数据总线不应该是按照顺序一一对应的吗?有没有人做过类似的板子?求指点。

2016-04-04 07:21:34

用Labview和NI-VISA做Cypress cy7c68013A的驱动 在安完驱动后 cypress官方固件下载器就识别不到USB了~求大神帮忙

2013-03-13 20:29:08

新作了一块CY7C68013A的核心板,但是插上无法识别,对照原理图和手册,各个主要引脚的电平应该没有问题,但是怎么搞都是USB无法识别。插上现成的开发板立即就能识别出来。估计是USB阻抗

2012-11-19 11:15:32

因为FPGA管脚不太够,想问下CY7C68013A-56PVXI可以使用8bit FIFO数据接口吗?可以的话,FPGA连接的是低8bit(FD0~FD7) 还是高8bit(FD8~FD15)呢?

2024-02-27 08:18:39

因为FPGA管脚不太够,想问下CY7C68013A-56PVXI可以使用8bit FIFO数据接口吗?可以的话,FPGA连接的是低8bit(FD0~FD7) 还是高8bit(FD8~FD15)呢?

2025-05-30 07:20:35

CY7C68013A用于我的板上的I2C通信,在数据表中最大的I2C请求是400千赫,我不知道CY7C68013A是否能支持1MHz I2C以及如何实现?谢谢。

2019-09-04 06:28:09

请问CY7C68013A高速模式如何配置?手册里只有提到了中断和ram

2024-02-23 08:09:59

请问CY7C68013A高速模式如何配置?手册里只有提到了中断和ram

2025-05-28 07:14:26

我需要Linux(Raspberry PI)的CY7C68013A驱动程序。这个驱动程序对于这个设备是可用的吗?谢谢。 以上来自于百度翻译 以下为原文I need driver for Linux

2019-07-04 09:46:18

破译芯片CY7C68013A,把里面的程序读出来,可以直接用到其他的芯片上。

2016-04-19 20:51:28

请问有谁做过cy7c68013a的Linux驱动,可不可以给一个参考下

2022-01-11 07:55:48

。EZ-USB FX2LP芯片是在Cypress公司第一款USB接口微处理器(EZ-USB FX2)基础上进行优化设计的结果。EZ-USB FX2LP系列芯片包括多种型号,例如CY7C68013A

2015-03-28 17:44:19

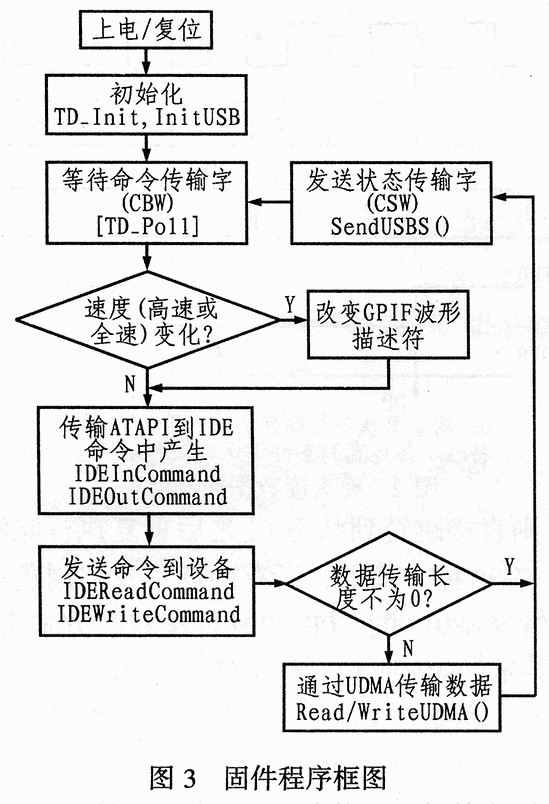

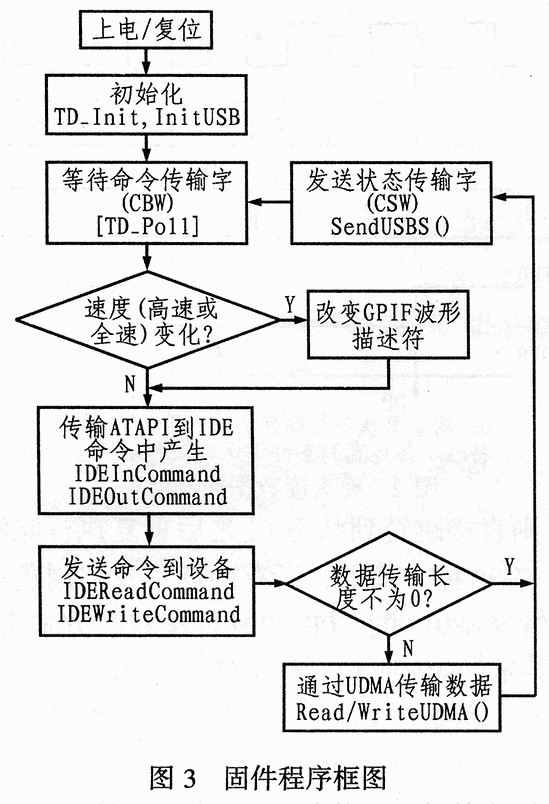

每个处理帧将预观测的变量结果以DMA的方式打包向上位机发送。FPGA实现ADSP-TS101的Linkport接口与CY7C68013A之间的双向数据缓冲和接口协议转换。考虑到CY7C68013A中

2019-05-31 05:00:04

ADSP-TS101 是ADI 公司新一代高性能浮点DSP,开始应用在高速数据采集和处理系统中。TS101 外部总线接口可编程,方便和各种总线外设接口。本文结合TS101 与同步FIFO、SDRAM 和FPGA 的接

2009-08-11 09:49:31 28

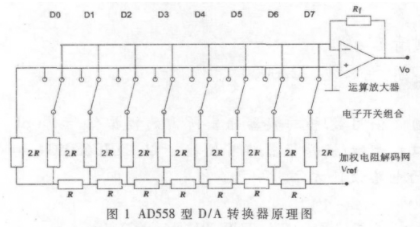

28 本文介绍了高速USB2.0芯片CY7C68013的特点。设计出一种主要由CY7C68013与Altera公司EP1C6芯片构成的USB2. 0数据采集系统.首先介绍了系统硬件设计部分,重点介绍了利用CYPRESS公司FX2系列的CY7C6

2009-09-14 14:33:36 133

133 USB2.0控制器CY7C68013的接口设计实现

1 引言 USB (Universal Serial Bus)接口以其速度快、功耗低、支持即插即用(Plug & Play)、使用安装方便等优点而得到

2010-01-21 10:00:23 1662

1662

Adsp-TS101性能比ADSP21160有显著提高,且与之兼容,使得以ADSP21160开发的产品升级快速、简捷。Adsp-TS101是64位处理器,工作在250 MHz时钟下,可进行32位定点和32位或40位浮点运算,

2010-09-23 09:57:25 2059

2059

CY7C68013A开发板的第一个程序应当从点亮数码管开始,这样感觉起来相当不错。数码管是用PCF8574驱动的,PCF8574与CY7C68013A是用I2C总线连接的,实际上这个实验主要是学习I2C总线的,后面要

2011-05-25 10:26:35 347

347 介绍一种基于USB接口芯片(CY7C68013A)和FPGA实现的ADSP-TS101扩展USB接口的设计方法,该方法利用DSP的Link-port接口,以DMA方式进行高速数据交换,目前该设计已成熟、可靠地应用于某弹载信号处

2011-08-22 16:02:13 4105

4105

设计了一个以 CY7C68013A 为接口芯片的并口转USB口的数据采集系统,讨论了CY7C68013A的性能及传输方式,给出了该系统的硬件设计方案,设计实现了USB2.0数据传输模块,阐述了系统的硬件设

2011-08-29 14:26:54 0

0 利用USB2.0接口芯片CY7C68013实现了语音信号处理系统中DSP与PC机的高速通信,简要介绍了CY7C68013的功能结构以及与TMS320C6203B的接口设计,深入研究了该芯片的固件、设备驱动和应用程序开

2011-09-08 17:59:56 69

69 利用USB2.0接口芯片CY7C68013实现了语音信号处理系统中DSP与PC机的高速通信,简要介绍了CY7C68013的功能结构以及与TMS320C6203B的接口设计,深入研究了该芯片的固件、设备驱动和应用程序开

2011-09-21 11:41:32 177

177 电子发烧友网为大家提供了CY7C68013A, CY7C68014A, CY7C68015A, CY7C68016A .pdf 免费下载,希望对您有所帮助!

2012-01-09 16:22:29 438

438 本文基于ADSP-TS101高速信号处理系统采用了集成系统设计,硬件部分引入信号完整性分析的设计方法进行高速数字电路的设计,解决系统中主处理器在较高工作频率300 MHz下稳定工作的问题

2012-09-06 17:15:51 7943

7943

为了同时实现计算机对FPGA进行在线配置和高速数据传输,提出了一种基于CY7C68013A芯片的USB2.0接口设计方案。介绍了以CY7C68013A芯片为核心的系统硬件电路设计和软件编程,详细分析了

2013-09-23 17:57:41 175

175 基于CY7C68013A的USB接口系统设计.

2016-01-22 14:26:58 43

43 基于CY7C68013A和FPGA的4路数据采集系统设计_智丹

2017-01-13 21:40:36 26

26 CY7C68013A是Cypress公司的EZ-USB FX2LP系列低功耗版本单片机,具有和8051兼容的CPU和指令系统,同时包括USB接口和完整的USB 2.0协议引擎,并且提供了完善的固件

2018-07-20 08:06:00 3987

3987

由于具备传输速率高、体积小等特点,USB接口广泛地应用于计算机外部硬件设计。针对此介绍了Cypress公司的CY7C68013A芯片的基本原理,以及使用CY7C68013A芯片进行USB键盘设计的方法。

2017-12-26 09:32:19 23272

23272

CY7C68013A 高速USB通信模块 USB mini接口

高速USB接口模块

型号 CY7C68013A USB Board (mini)

2019-12-30 11:12:06 3957

3957

Cypress公司推出的EZ-USB FX2LP系列USB接口芯片是集成了USB2.0协议的微处理器,其中应用最普遍的是低功耗芯片CY7C68013A,它具有高性能、低功耗的优点。

2020-08-25 15:19:40 6585

6585

EE-157:解释ADSP-TS101上的分支目标缓冲区

2021-04-15 21:33:37 13

13 EE-143:了解ADSP-TS101上的DMA

2021-04-24 11:29:52 7

7 ADSP-TS101 TigerSHARC处理器编程参考

2021-05-13 17:11:14 9

9 ADSP-TS101 TigerSHARC处理器硬件参考

2021-05-22 10:59:30 4

4 电子发烧友网站提供《基于CY7C68013A芯片的CMMB网络测试接收机的设计方案.pdf》资料免费下载

2023-10-23 10:13:47 3

3 电子发烧友网站提供《EE-157:ADSP-TS101上的分支目标缓冲器说明.pdf》资料免费下载

2025-01-14 15:05:56 0

0

电子发烧友App

电子发烧友App

评论