设计背景: 二进制转十进制在设计应用中十分的广泛。尤其在AD转化中是必须所用到的一个小知识点,学习二进制转十进制的方法显的非常的重要。今天就和笔者来学习二进制转十进制的方法,通过简单的学习来掌握这么

2018-09-20 09:38:39 15588

15588

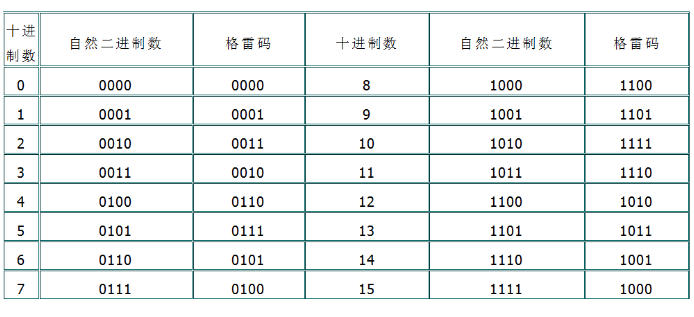

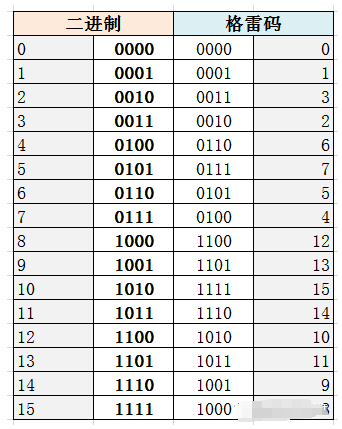

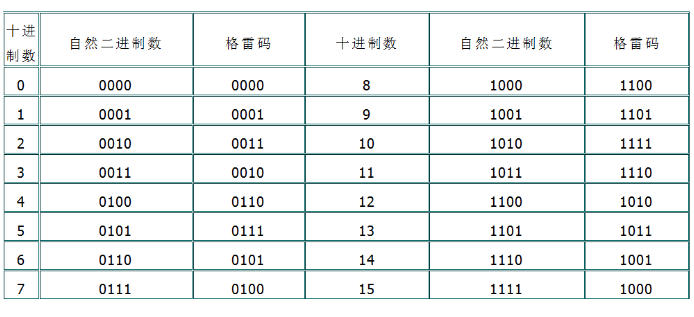

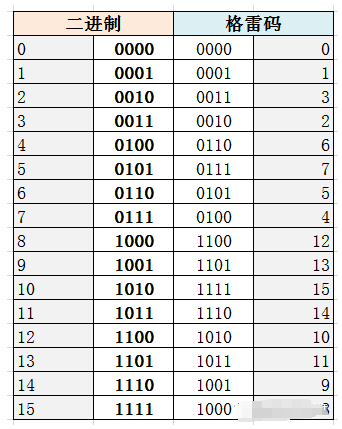

其中采用循环二进制编码的绝对式编码器,其输出信号是一种数字排序,不是权重码,每一位没有确定的大小,不能直接进行比较大小和算术运算,也不能直接转换成其他信号,要经过一次码变换,变成自然二进制码。

2020-09-23 16:23:04 6149

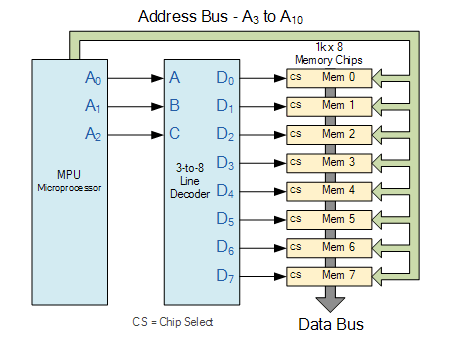

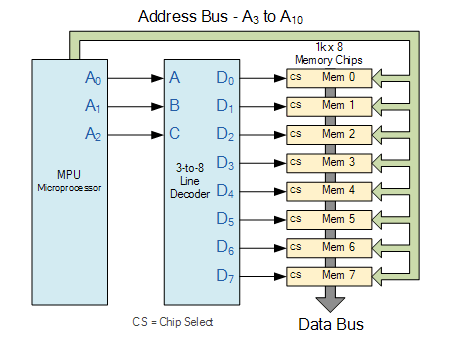

6149 二进制解码器是由单独的逻辑门构成的另一种组合逻辑电路,与编码器完全相反。名称“解码器”是指将编码信息从一种格式转换或解码为另一种格式,因此二进制解码器使用2 n个输出将“ n”个二进制输入信号转换

2020-12-29 12:10:32 8355

8355

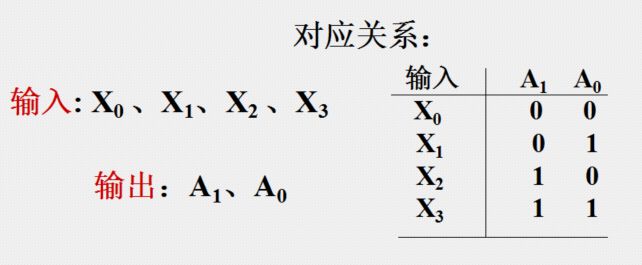

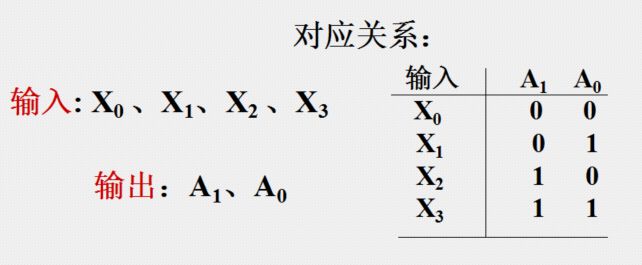

的逻辑电路称为编码器。编码器有若干个输入,在某一时刻只有一个输入信号被转换成为二进制码。如果一个编码器有N个输入端和n个输出端,则输出端与输入端之间应满足关系N≤2n。例如8线—3线编码器和10线—4线编码器分别有8输入、3位二进制码输出和10输入、4位二进制码输出。

2023-10-27 09:29:49 2051

2051

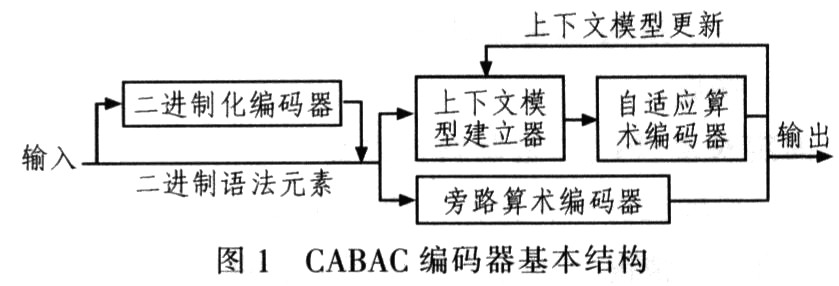

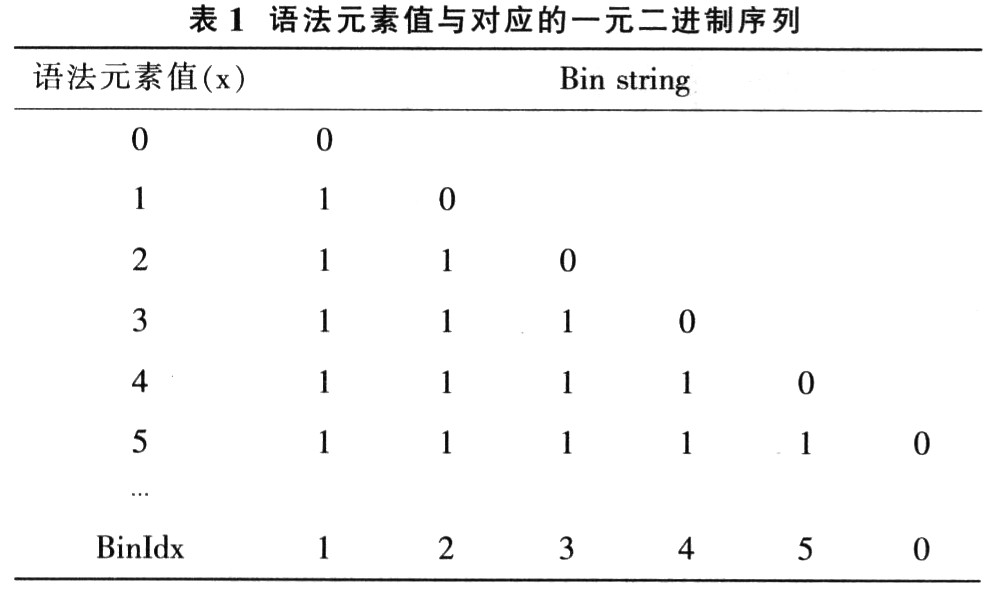

2003年发布的H.264视频压缩编码标准在一定程度上解决了要在尽可能低的码率下获得尽可能好的图像质量这一问题。在相同的重建图像质量下,H.264能够比H.263节约50%左右的比特率。此外

2020-03-05 07:05:07

H.264编码器流程图说明:1.参考代码版本为jm61.流程图中有些地方直接引用已经修改过的代码,未作说明.2.代码经过删减,但是整个流程没有变化. 看该流程图时可能用得到的约束

2008-06-25 11:43:55

物体的形状,于是,在每个宏块中可包含有1、2、4、8或16个运动矢量。 多参数帧估计 在H.264中,可采用多个参数帧的运动估计,即在编码器的缓存中存有多个刚刚编码好的参数帧,编码器从其中选择一个给出

2008-06-04 14:29:02

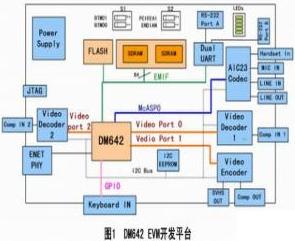

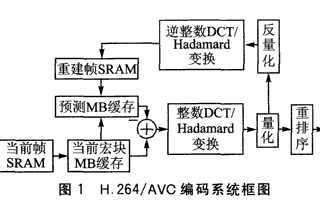

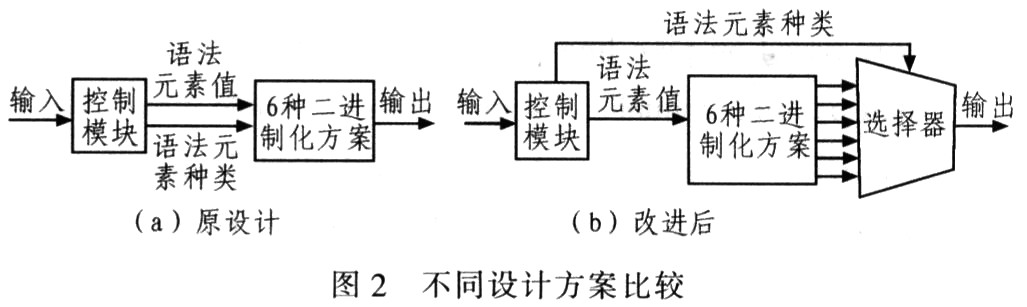

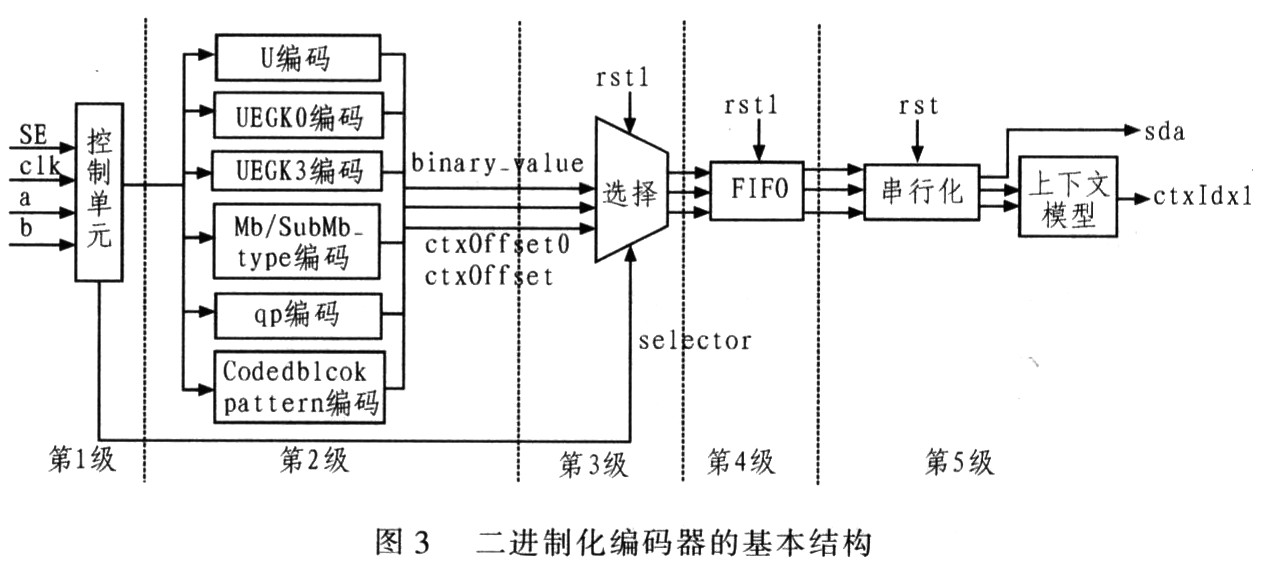

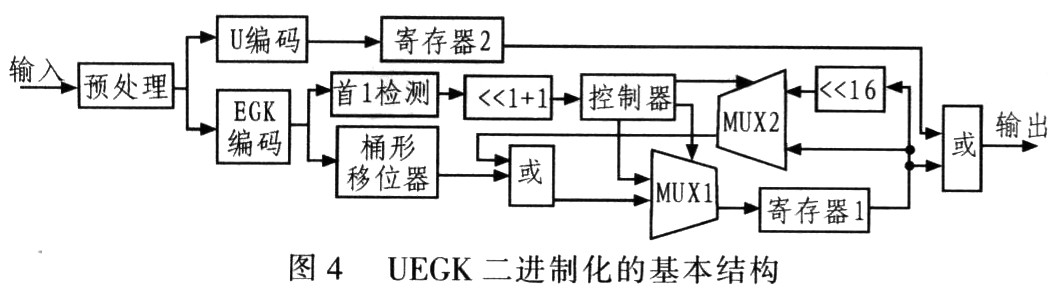

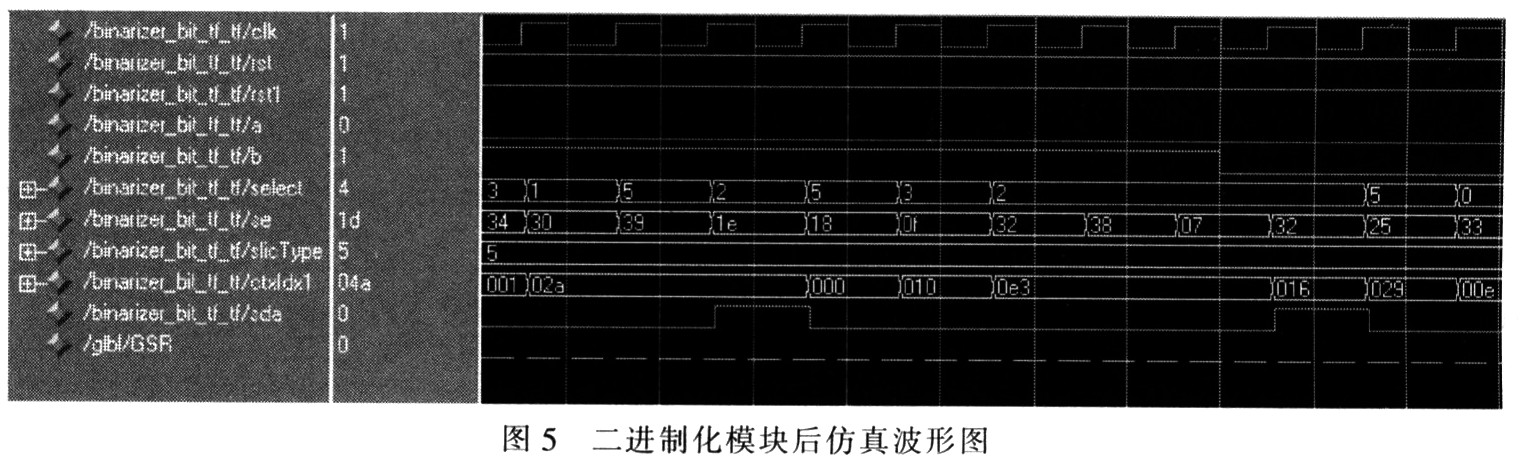

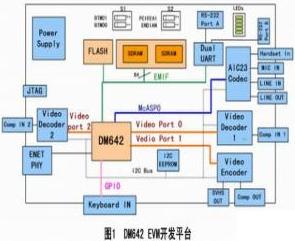

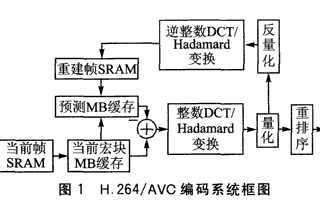

减小算法的存储器需求,减少中间结果的存储需求,可缩减片外存储器访问次数,提高应用的实时性能。下面主要讨论降低H.264 INTRA帧编码的运算复杂性和存储器需求的方法。图1 H.264编码器的结构流程图 图2

2019-08-06 06:37:38

各位大神有做过H.264 CABAC Verilog HDL实现的吗?小弟急求源代码,希望做过的大婶们给予指导,定重重酬谢@@

2015-01-14 14:13:25

×2160)和8K(8192×4320)超高清视频。可以说,H.265标准让网络视频跟上了显示屏“高分辨率化”的脚步。 H.264 H.264,同时也是MPEG-4第十部分,是由ITU-T视频编码

2020-12-11 15:45:33

什么是编码技术?H.264编码技术在视频会议中的应用是什么?

2021-06-02 06:17:58

h.264协议中文版下载 访问单元:AC变换系数:自适应二进制算术解码过程:自适应二进制算术编码过程...中英文版,直接翻译的。。还能让你学习学习英语。。。不错哦。。。。下了记得顶一顶了

2008-05-30 17:48:51

。而绝对式编码器是直接输出数字量的传感器,它是利用自然二进制或循环二进制(格雷码)方式进行光电转换的,编码的设计一般是采用自然二进制码、循环二进制码、二进制补码等。特点是不要计数器,在转轴的任意位置

2011-03-08 14:16:59

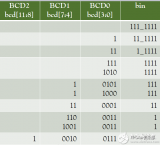

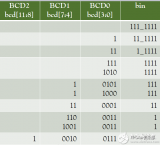

Binary-Coded-Decimal,二进制编码的十进制码。 这种编码仅仅使用4位二进制数来表示十进制数中的0~9十个数码。二进制数码每位的值称为权或位权。 其中b0位的权为20=1,b1位

2009-04-06 23:55:36

在LabVIEW中,如何实现一个十六进制的数取反后加1,如FFFFFFCB表示为二进制是11111111111111111111111111001011,取反后

2014-03-15 00:32:43

实现两个二进制除法运算,并在八个七段数码管上进行显示实现两个二进制除法运算,并在八个七段数码管上进行显示实现两个二进制除法运算,并在八个七段数码管上进行显示

2013-11-01 20:34:01

编码器的实现 H.264视频编码器的实现有多种方法,不过大部分都是进行移植、优化的操作。H.264代码要在DSP的软件平台CCS环境下运行,需要注意几个问题:如配置文件、库文件的改动、数据类型

2011-08-10 14:54:09

小妹在做一个心电信号发生器 其中从ACCESS数据库中需要读一个WaveData.data 的长二进制数据 这是心电图波形的数据 每个图500个点每个点2字节。怎么才能读出这个长二进制数据?用变体么?

2014-10-26 20:51:14

`各位大神,我想把一张图片通过变成二进制通过TCP传输,现在我把图片转换成二进制文件,但文件只有1KB大小。我想读取但是不知道二进制的图片数据类型。能否帮我画一个简易的读取二进制图片的程序,谢谢`

2017-12-29 09:26:42

SUNNISKY ENC264HD是一款实用的、且符合H.264标准的ASI-TS IP实时视频/音频的高清HD压缩编码或转码设备,其功能是将一路模拟视音频(或Y/PB/PR)输入的信号/或数字

2011-03-06 19:27:12

/davinciedu.html成都宇鸿科技是一家在TI DAVINCI 平台专注3G和视频编解码算法优化和实现的公司,是国内少数能整体提供嵌入式3G, H.264超低码率编码器,基于VPN的视频联网传输平台的公司之一

2009-12-02 14:10:03

每一个元素都是复数,类似这样的-59.4184087630243-2.62712122987465i。 小弟想实现这个Levinsondurbin的功能仿真,首先把向量实部虚部给导入,该怎么操作这样的浮点数变成有符号的二进制表示呢。

2020-07-21 16:10:48

用verilog实现变量flag为1表示变量a的数值中二进制1的个数是奇数,flag为0表示变量a的数值中二进制1的个数是偶数,比如:a为8’b1111_0000,则二进制1的个数为4,即偶数

2023-08-15 10:42:24

的设计中会经常遇到。转换原理对于一个8位二进制码,其在十进制编码方式下的值为:把上式写出套乘的形式:式中的每项乘2,相当于将寄存器中的二进制码左移1位,这就意味着利用移位寄存器可以完成二进制

2017-01-09 14:38:01

文件名 -coding 7 -t 2 -w 320 -h 240其中-t 2是表示进行编码动作。这是编译好的二进制文件,可以直接push进系统测试。你猜对了,这个文件也一样具有之前帖子提到的裸码流解码功能。

2015-02-10 18:02:25

在LABVIEW中使用二进制读写节点时,遇到一个奇怪的问题,当我通过新建文件创建二进制文件(见第一张图),之后将数据写入到二进制文件中(见第二张图),最后读取二进制文件(见第三张图)。现在问题是当我

2017-09-30 15:03:01

,其余的用0代替,最后得到的二进制数为10011011。 需要指出的是,多数计算机或数字系统中只处理4、8、16、32位的二进制数据,因此,数据的位数需配成规格化的位数,如例题1.3.3种转换结果为

2009-04-06 23:54:14

字逻辑设计课程中,我们已经学过了BCD码的相关知识,它用4位二进制数来表示1位十进制数中的09,是二进制编码的十进制代码,常见的BCD码有8421BCD码,2421BCD码,5421BCD码,余3码以及格雷

2022-07-12 16:41:42

制。递归算法,如 IIR 滤波、MPEG 1/2/4 中的变长编码(VLC)、上下文自适应变长编码(CAVLC),以及 H.264/AVC 中的上下文自适应二进制算术编码(CABAC),当映射到这些可编程

2008-06-25 11:33:26

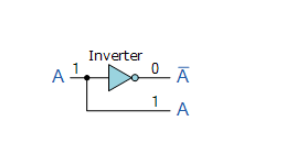

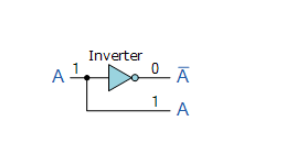

,有时候需要将输入的数据信息变换为某种特定的编码输出,编码器便是实现这一编码功能的逻辑电路。编码器的逻辑功能是将输入的高低电平信号转换为二进制编码输出,通常是将多比特的输入数据转换为少比特的二进制编码

2022-08-04 17:39:32

在C语言中二进制表示是0bxxx开头的,

为什么给寄存器赋值GpioCtrlRegs.GPAMUX2.bit.GPIO16 = 0b00; 会出错 ?

2018-05-14 07:02:41

创建前面板,该前面板有8个led指示器和一个8位无符号十进制整数的垂直滑动条控件。显示滑动条带有数字指示器,确保led均匀分布并且排列在底部。要求实现8个led的亮灭状态与滑动条中的十进数的数字的二进制相对应。(即十进制向二进制转换)

2015-09-19 10:06:39

平台总体框架图 图3 H.264编码模块图 2 H.264编码器的优化 2.1 总体优化 [td] 总体优化主要包括两部分内容:程序模块化的设计及数据结构的设计。 程序模块化设计时,既要考虑

2011-07-13 17:12:01

一个8位二进制数经过二进制LDPC编码器编码后等到一个几位二进制的数,怎么计算的?

2017-03-14 13:07:56

系统的硬件结构 视频编码器的硬件结构如图1所示。从摄像头输出的原始视频流通过USB接口进入PXA255芯片进行h.264压缩,压缩后的码流由网口(ETHERNET)传到主机进行显示,Flash中烧写了

2011-08-24 08:59:17

应用程序 : 示例代码演示了如何丢弃函数的二进制代码, 然后填入 SRAM 的二进制代码, 然后调用它 。

BSP版本:M451系列BSP V3.01.001

硬件: 任何 M451 系列板块

2023-08-23 06:34:10

我想制作一个以8个LED的形式实现二进制计数器。该计数器通过USART发送一个8位二进制数,并让8个LED显示数字(如果位为0,则指示灯熄灭,当位为1时指示灯亮)。这样做的最佳方法是什么?

2018-10-08 14:07:42

。如何判断接收到的数据是二进制的0还是二进制的1?电路原理图:源码下载链接:工程项目结构如下图所示:其中画红色方框部分为重要函数来进行讲解DHT11.c#include "DHT11/DHT11.h"#include "DELAY/Delay.h"/**

2022-02-22 06:24:51

什么是H.264视频编码技术?如何去实现并优化一种H.264视频编码器?

2021-06-03 07:00:52

在Nios II中,我们可以通过Nios II 中的flash烧写功能往FPGA中固化程序和系统参数,如果我们想单独烧写系统参数呢?就是想在flash或者EPCS的空闲区域写入二进制数据。在软件

2012-03-08 15:33:17

二进制运算规则二进制的运算算术运算二进制的加法:0+0=0,0+1=1 ,1+0=1, 1+1=10(向高位进位);二进制的减法:0-0=0,10-1=1(向高位借位) 1-0=1,1-1=0 (模

2019-12-11 17:49:02

在DSP平台上进行视频产品开发有什么优势?怎么实现基于ADSP-BF561的H.264编码器设计?

2021-06-07 06:46:01

我正在使用Labview来控制网络分析仪E5072A。我想从VISA输出中获取二进制数据,而不是默认的字符串格式。在这种情况下,我想速度会更快,因为我们直接获得机器语言,因此CPU不需要

2019-01-07 15:49:29

足H.264标准的编解码运算速度要求。因此,在稳定的媒体处理器平台上实现H.264标准有着较好的工程意义和应用前景。

2019-09-04 06:19:09

一种基于NiosII的低码率实时H.264视频编码器设计

2021-06-07 07:06:49

增加了NAL层,负责将编码器的输出码流适配到各种类型的网络中,从而提供了友好的网络接口。H.264之所以能够达到以上性能,是因为采用了以下一些先进的技术:首先是帧内预测编码,充分利用图像空域相关性,来降低

2008-06-25 10:35:31

最新视频编码标准H.264及其核心技术H.264是ITU-T和ISO联合研究制定的编码效率高、网络适应性强的最新数字视频编码国际标准.H.264是面向视频电话、视频会议等实际应用的标准,它能以低

2008-06-25 11:42:03

用FPGA 怎么实现BCD码转换成二进制啊!新手求指教PCB打样找华强 http://www.hqpcb.com 样板2天出货

2013-03-15 12:00:01

、8或16个运动矢量。 多参数帧估计 在H.264中,可采用多个参数帧的运动估计,即在编码器的缓存中存有多个刚刚编码好的参数帧,编码器从其中选择一个给出更好的编码效果的作为参数帧,并指出是哪个帧被

2008-05-28 16:28:11

量化的功能有哪些?量化的算法是什么?怎样用Verilog语言实现H.264的量化?如何运用Modelsim对H.264进行仿真?

2021-04-28 06:12:51

请问在FPGA上如何去实现H.264/AVC视频编码标准?

2021-05-07 07:27:02

H.263和MPEG一4可以节省20%~50%的码率。就其基本档次而言,编码器的复杂度是H.263的10倍左右。H.264良好的网络亲和性和优异的压缩性能使其成为视频应用的首选,但其巨大的运算量

2019-07-29 06:52:57

针对硬件实现的H.264视频编码算法改进,不看肯定后悔

2021-06-04 06:25:51

Changes for Version JM7.3 to JM 7.2h.264编码器源代码,带有H.264编码器流程图。Bug fixes- encoder: DPB for field

2008-06-25 11:46:18 164

164 H.264三大开源编码器之评测报告Peter Lee 2005.6.19 Outline1、三大开源编码器介绍2、实验条件3、实验结果4、实验结论plus:增加t264 high quality mode的实验结果note: 新

2008-08-25 13:07:10 51

51 阐述H.264/AVC 二进制算术编码的原理,论述此编码的IP 核设计方案及其FPGA 验证。整个设计使用VerilogHDL 语言描述,在 ALDEC 的Active_HDL6.2 平台上进行时序仿真,在 Synplicity 的Synplify7.0平

2009-09-03 09:11:20 25

25 设计并实现了基于DSP 芯片TMS320DM642 的H.264 编码器。详细介绍了H.264 算法在DSP上的移植和优化。为使编码器达到实时应用的要求,采用基于C64x CPU 的软件优化技术,对H.264的一些核

2009-09-03 14:30:34 23

23 H.264 实时编码器的研究和实现是目前视频通信研究领域的一个热点问题,本文介绍了基于TMS320DM642 平台的H.264 编码器的优化,重点介绍了基于DM642 的整数DCT 变换、量化和匹配

2009-12-18 12:13:37 19

19 为了在改进的H.264 上实现无再损帧内编码,该文提出了一种新的基于整数线性规划的优化clip 算法及改进算法,解决了H.264 多次编码中由当前clip 模块和帧内预测运算引入的视频畸

2010-02-09 14:28:11 35

35 基于ADSP-BF561的H.264视频编码器的实现

H.264/AVC是ITU-T VCEG和ISO/IECMPEG联合制定的最新视频编码国际标准,是目前图像通信研究领域的热点技术之一。H.264的视频编码层(VCL)

2008-12-26 14:43:44 706

706 二进制

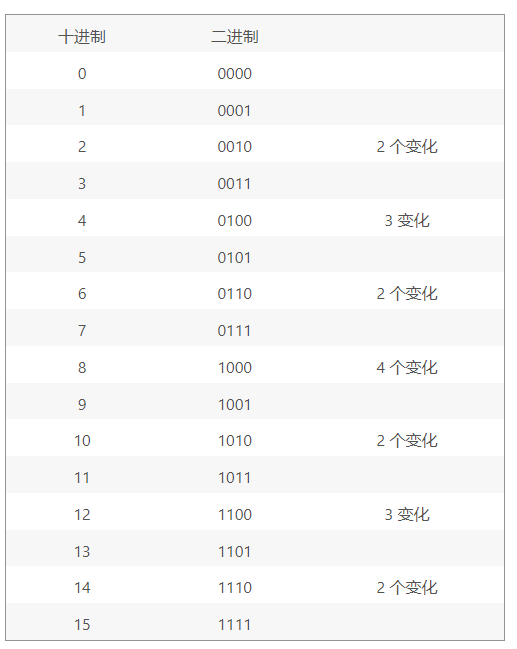

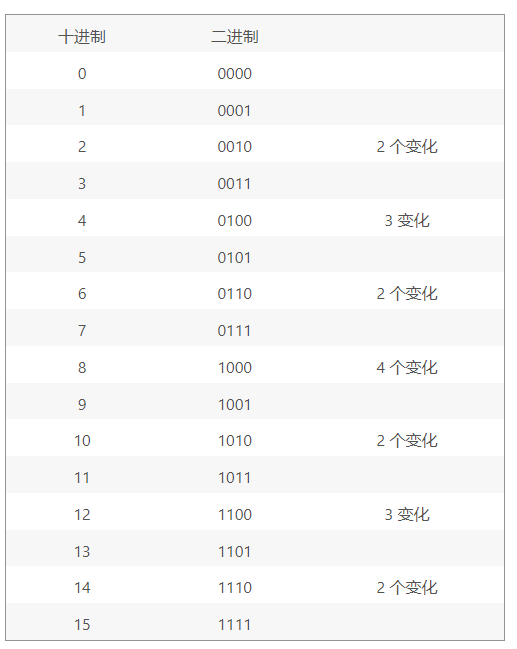

二进制与十进制的区别在于数码的个数和进位规律有很大的区别,顾名思义,二进制的计数规律为逢二进一,是以2为基数的计数体制。10这个数在二进

2009-04-06 23:48:01 7548

7548

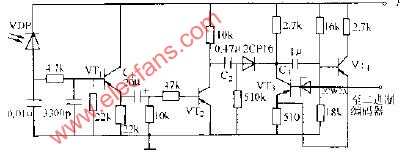

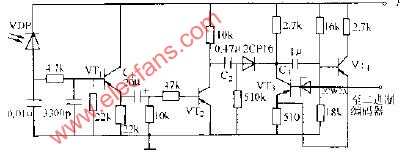

配用二进制编码器的光控电路图

2009-06-06 09:30:38 645

645

二进制编码和二进制数据

二进制编码是计算机内使用最多的码制,它只使用两个基本符号"0"和"1",并且通过由这两个符号组成的

2009-10-13 16:22:51 4459

4459 基于TMS320DM6446的H.264编码器实现与优化

1 引言

H.264是ITU-T的视频编码专家组(VCEG)和ISO/IEC的活动图像专家组(MPEG)联合制定的视频压缩标准。

2010-02-10 09:20:11 1311

1311

什么是二进制计数器,二进制计数器原理是什么?

计数器是数字系统中用得较多的基本逻辑器件。它不仅能记录输入时钟脉冲的个数,还可以实现

2010-03-08 13:16:34 30352

30352 二进制电平,什么是二进制电平

在二进制数字通信系统中,每个码元或每个符号只能是“1”和“0”两个状态之一。若将每个码元可能取的状态增

2010-03-17 16:51:58 2255

2255 十进制数的二进制编码

在人机交互过程中,为了既满足系统中使用二进制数的要求,又适应人们使用十进制数的习惯

2010-05-02 19:04:06 8947

8947 Jointwave发布的H.264编码器可实现1080p

Jointwave发布的H.264编码器技术提供了单芯片HD和超低功耗广播级视频— 针对65nm处理器60mW可实现1080p。

正如在强调Jointwave的H.26

2010-01-04 08:41:20 1116

1116 摘要:在DM642 EVM平台上实现了 H.264视频编码器,并从内存分配、Cache优化、代码优化以及汇编程序级优化等几个方面对编码

2011-01-10 14:12:14 3202

3202

介绍了基于嵌入式平台PXA255的h.264视频编码器的实现。在描述了视频编码器的硬件结构设计及视频采集软件的实现的基础上,详细介绍了h.264对视频编码标准的一些改进以及基于PXA2

2011-09-02 16:41:57 87

87 为了实现基于DSP的H.264视频编码器的实时性能,提出了一系列优化实现方法。首先结合TMS320DM6437硬件特点,描述了X264代码向TMS320DM6437平台的移植过程和优化方法,重点介绍了整数DCT变换

2012-05-22 15:10:25 63

63 基于PowerPC的H.264编码器中断处理程序解析

2016-01-04 15:26:58 6

6 格雷码,又叫循环二进制码或反射二进制码,格雷码是我们在工程中常会遇到的一种编码方式,它的基本的特点就是任意两个相邻的代码只有一位二进制数不同,这点在下面会详细讲解到。格雷码的基本特点就是任意两个相邻的代码只有一位二进制数不同。

2018-03-02 15:48:53 16613

16613

BCD码亦称二进码十进数或二-十进制代码。用4位二进制数来表示1位十进制数中的0~9这10个数码。它是一种二进制的数字编码形式,用二进制编码的十进制代码。BCD码这种编码形式利用了四个位元来储存一个十进制的数码,使二进制和十进制之间的转换得以快捷的进行。

2018-03-14 10:15:42 6149

6149 目前的视频监控行业,基于DSP的H.264编码器解决方案占有绝对优势的市场份额,这是由DSP方案开发周期相对较短的特性决定的。在ASIC或FPGA方案仍处于研发阶段时,DSP方案已捷足先登,并较好地解决了视频监控行业中H.264编码器方案从无到有的过程,为H.264在监控应用中走向成熟立下了汗马功劳。

2018-10-29 08:21:00 12470

12470 二进制解码器是另一种由各个逻辑门构成的组合逻辑电路,与编码器完全相反。

2019-06-22 09:41:36 8521

8521

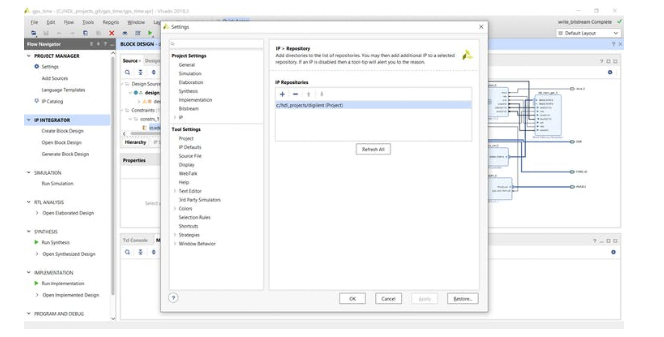

目前高清H.264 摄像机的核心SoC基本上都是ASIC,而FPGA作为近年来发展迅速的可编程器件,在高清H.264 摄像机的SoC领域如何能有一席之地?这是我们的设计需要实现的目标。

2020-07-27 10:50:01 12

12 二进制解码器是由单独的逻辑门构成的另一种组合逻辑电路,与编码器完全相反。名称“解码器”是指将编码信息从一种格式转换或解码为另一种格式,因此二进制解码器使用2 n个输出将“ n”个二进制输入信号转换为等效代码。

2021-01-03 17:42:00 5675

5675

根据H.264/AVC编码器原理及结构,同时考虑到现有硬件资源的限制以及该设计的应用需求,设计了图1所示的H.264/AVC编码系统结构。

2021-03-16 14:12:54 2117

2117

基于FPGA的二进制相移键控设计方案

2021-05-28 09:36:50 11

11 绝对编码器中的传感器输出格雷码序列,需要一些复杂的转换方法才能正确使用。本文展示了如何获取绝对编码器使用的格雷码并将其转换为二进制。

2022-05-05 15:41:49 5409

5409

本方案是一个基于FPGA的二进制时钟,使用GPS作为时间参考。

2022-05-13 17:41:31 1786

1786

将二进制数视为元胞自动机可能有助于数字二进制计数器的设计和实现吗?

2022-07-28 11:47:10 1181

1181

格雷码是一种循环二进制编码,特点是相邻数变化时只有一位数据跳变。

2023-01-17 11:15:17 3292

3292

将信息(如数和字符等)转换成符合一定规则的二进制代码。

2023-03-21 11:55:48 7723

7723

二进制最佳接收原理 二进制最佳接收机的实现形式有哪两种? 二进制最佳接收原理是计算机通信中的重要概念,它是指在二进制通信中通过一定的方法,使接收机在信号传输过程中能够准确、可靠地接收到发送端传输

2023-11-27 16:19:07 429

429 如何实现二进制和BCD码数据的相互转变? 二进制码是将十进制数字表示为二进制数和十进制数的一种表示方法。在计算机系统中,二进制数是最基本的数制表示方法,而BCD码则是用于将数字直接转换为二进制

2024-02-18 14:51:58 215

215

电子发烧友App

电子发烧友App

评论