德国慕尼黑,2022 年 6 月——可定制RISC-V处理器硅知识产权(IP)的领导者Codasip日前宣布,其Codasip Studio平台现已支持苹果公司macOS Monterey(当前

2022-06-28 14:06:36 1037

1037

,RISC-V®嵌入式处理器IP的领先供应商Codasip在捷克布尔诺和德国汉堡宣布,嵌入式电机和运动控制集成电路及微系统领域的全球领导者Trinamic选择了Codasip的Bk3处理器用于其下一代产品系列。

2018-03-01 16:23:47 9764

9764 ,以进行全面和彻底的处理器测试。Codasip不断在处理器验证方面投入巨资,以再接再厉为业界提供最高质量的RISC-V处理器半导体知识产权(IP)。 Siemens EDA的OneSpin工具提供了一个先进且无比强大的验证平台,用以解决关键的芯片完整性问题。OneSpin是极为先进的形式验证工具,适用于汽车

2022-05-07 13:55:42 6483

6483

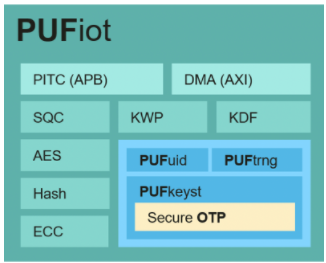

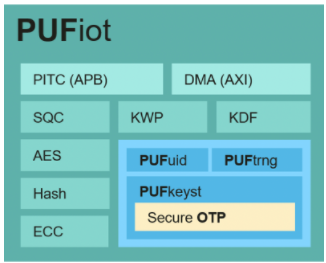

为了保护 IoT 应用程序,PUFsecurity 利用芯片指纹技术来强化信任根,并开发了 PUFiot,这是一种具有广泛安全边界的安全协处理器,可以轻松地集成到安全的 RISC-V 系统中。

2022-08-16 09:31:11 1427

1427

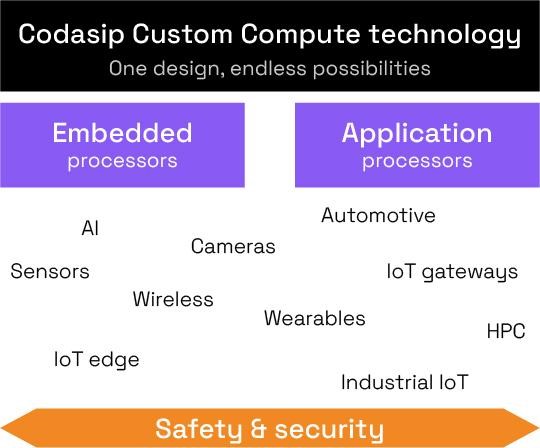

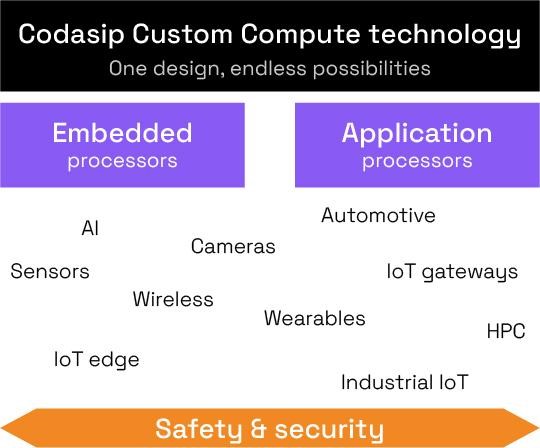

推出高度灵活的700系列,以实现无限创新 德国慕尼黑,2023年10月17日 ——RISC-V定制计算领域的领导者Codasip®今日宣布:推出一款全新的、高度可配置的RISC-V基准性处理器系列

2023-10-24 17:25:33 339

339

RISC-V ISA 命名规范RISC-V ISA 采用模块化的方式进行组织,每一个模块使用一个英文字母表示,其命名格式可以参考如下:RV[字宽][指令集模块]RV:RISC-V字宽(处理器寄存器

2021-12-09 06:31:44

计算机指令的微处理器,起源于80年代的MIPS主机(即RISC机),RISC机中采用的微处理器统称RISC处理器。

这样一来,它能够以更快的速度执行操作(每秒执行更多百万条指令,即MIPS)。因为

2024-03-12 10:25:21

, 64位Linux兼容版U2,U7处理器。并着手于简化芯片设计领域的技术鸿沟,提供云端的模块化设计和验证程序。SIFIVE目前也是RISC-V领域产品系列最全,技术相对领先的公司。其它芯片设计公司

2020-06-22 16:51:57

RISC-V处理器是开源的,那开发环境需要厂商自己开发还是沿用传统的开发环境呢?比如keil

2024-01-13 19:18:35

精简指令集计算机。RISC-V是基于RISC原理建立的免费开放指令集架构(ISA),V是罗马字母,代表第五代RISC(精简指令集计算机),可读作RISC-FIVE。通过开放式标准协作实现处理器创新的新时代

2020-08-13 15:13:41

我有兴趣在深度睡眠时使用 risc-v 协处理器通过 i2c 获取传感器读数,大概每 10 分钟左右一次。我有兴趣通过不唤醒 esp 来读取传感器来潜在地节省电量。我被推迟在基于堆栈的协处理器上执行

2023-03-02 09:03:59

RISC-V和开源处理器之间是什么关系?

2023-03-09 10:06:52

的并行编程框架)的支持引入RISC-V处理器。AMD没有回应有关其是否参与将ROCm移植到RISC-V的评论请求。

2023-08-11 18:20:57

在2019年时就推出了RISC-V内核的MCU产品、乐鑫在2020年发布了搭载RISC-V处理器的WiFi+蓝牙模组、GreenWaves 发布了其超低功耗GAP9音频芯片、中科蓝讯有多款RISC-V

2021-06-18 20:57:35

本期文章目录一个小型RISC-V开源处理器核介绍!#SOC#FPGA#RISC-V点击阅读数字积木从零开始写RISC-V处理器(超详细)#RISC-V点击阅读数字积木为什么说模拟工程...

2021-07-23 09:42:00

RISC-V是什么?有哪些特点?如何去设计RISC-V处理器?

2021-06-18 09:24:03

RISC-V是什么?它与ARM架构相比有何优势和劣势?哪些市场应用和产品将会成为RISC-V架构快速发展的驱动力?RISC-V对半导体产业的发展会带来哪些影响?

2021-06-16 06:44:17

回顾过去几年的集成电路产业里,RISC-V是一个绕不过去的热词。作为一项以“开源”为卖点的技术,RISC-V自面世以来,就在相对古板的处理器设计领域激起了不小的浪花。由于RISC-V的开源特性造就了

2020-06-22 16:55:03

50条指令,可以用于实现一个具备定点运算和特权模式等基本功能的处理器。 RISC-V的三大特点 第一点是完全开源,对指令集使用,RISC-V基金会不收取高额的授权费。开源采用宽松的BSD协议,企业

2020-08-25 11:17:39

)、RISC-V 主管二进制接口(SBI)、RISC-V 统一可扩展固件接口(UEFI)规格,以及 RISC-V Zmmul纯乘法扩展。 核心观点: 技术层面,RISC-V由于其开源、灵活的技术架构

2023-04-03 15:29:09

的Risc-V内核高精度AI 处理器。K510-CORE是核心模组,板载一颗K510芯片,CPU采用双核64bit RISC-V架构,K510搭载自主研发的第二代神经网络处理器KPU2.0,采用独创计算

2022-11-18 14:15:24

64bit RISC-V架构,K510搭载自主研发的第二代神经网络处理器KPU2.0,采用独创计算数据流技术,算力较上一代提升3倍同时降低功耗。板载内存为512MB LPDDR3@1600MHz。支持两路

2022-11-18 15:10:22

公司从成立之初就一直坚持使用自主产权的内核和MCU所需要的各种IP。虽然通过技术研发创新来实现微处理器的自主可控十分艰难,但坚持下来的价值和优势也十分明显。针对目前RISC-V MCU的发展痛点,爱普特

2023-04-05 12:16:42

RISC-V架构秉承简单的设计哲学。体现为:在处理器领域,主流的架构为x86与ARM架构。x86与ARM架构的发展的过程也伴随了现代处理器架构技术的不断发展成熟,但作为商用的架构,为了能够保持架构的向后兼容性

2021-06-18 19:41:21

本帖最后由 闲散子 于 2021-4-25 13:40 编辑

RISC-V的迷人之处之一是它是如此……灵活。作为开源处理器规范,绝对任何人都可以使用它,对其进行修改并将其商业化。没有许可费

2021-04-25 06:29:31

10 月 19 日,2021 云栖大会上,平头哥开源了玄铁RISC-V系列处理器,并开放了工具及系统软件。这次的开源对国内的RISC-V生态圈具有非常重要的意义。关注了一下这次开源发布的东...

2022-02-28 08:15:04

如何?Alessandro: 没错。定制化是开源RISC-V内核的主要优势,拥有开源硬件是定制化成功的关键,要付出的主要代价是软件需要与硬件一起进行验证,但是,这对于处理器的特定用途而言不是问题。相反,对于

2020-08-02 11:58:14

,届时我国企业有望在全球RISC-V新生态中取得领先优势,打通芯片领域国内国外双循环,实现我国高端处理器芯片产业自立自强。

芯来科技也是国内较早参与RISC-V CPU IP核研发的创业公司

2023-05-30 14:11:59

所创造过的辉煌。 和Sparc处理器相比,Intel的386处理器基于CISC技术,传统的X86指令不仅长度较长,且长短不一。 究竟是采用全新的RISC架构,还是走兼容+改进的技术道路?Intel

2023-03-30 16:34:57

,便可以生成当前硬件条件下的最佳代码。 RISC-V诞生的背景 ISA霸权 微处理器的开放指令集有望重塑计算,并引入新的、更强大的功能。 现代计算机依靠许多元件来提供高速和高性能,但是很少

2023-03-30 16:40:41

逻辑、算术等运算,CPU只处理寄存器中的数据。同时由于这个原因,包括ARM在内的很多RISC架构处理器都有很多寄存器来存放指令及数据。为了方便指令的解码,虽然ARM处理器不是单周期指令,但是其绝大多数

2021-04-25 09:13:19

1.1简介FreeRTOS中面向RISC-V的接口是易于拓展的,其提供了一系列基本的接口,用于操作适用于所有RISC-V实现中的通用寄存器,以及一系列的宏来处理特定的硬件实现中涉及到的特性以及拓展

2023-04-09 09:26:41

去年破产,并于上周以一个新名称出现:其收购的技术MIPS。向新的MIPS打个招呼。 MIPS处理器体系结构的开发现已停止,MIPS(该公司)将开始制造基于RISC-V的芯片。这是业务模式的完全改变,而

2021-03-09 19:30:07

由欧洲航天局支持,由苏黎世联邦理工学院和博洛尼亚大学的工程师开发的 Occamy 处理器现已流片。它使用了两个 216 个 32 位 RISC-V 内核的 chiplet 小芯片、未知数量的 64

2023-05-13 08:44:36

的处理器指令集,是构建芯片生态和发展芯片技术的核心部分,其重要性不言而喻。在此背景下,RISC-V有望成为新的选择。尽管具有通用、开放与免费的先期优势,但相比已经成熟的Arm和Intel x86,国内

2020-11-14 09:26:41

具备与多种处理器架构协同工作的潜质,其B系列更是可以达到最高6TFLOPS的算力,对于视觉计算优异但3D图形处理仍然偏科的RISC-V来说,可以说是一个很好的辅助,尤其是对于图形性能有一定要求的消费类

2022-03-24 15:53:12

⼒。 前云天励飞市场中心总经理;前SiFive China市场开发总监;前国科微电⼦副总裁;前全志科技营销总监等。议题四扩展RISC-V 的芯边界-Andes最新的处理器核介绍RISC-V国际协会自

2023-01-06 14:27:42

,然后返回到内存中。RISC-V 和 ARM 都支持 32 位或 64 位指令集。

二、RISC-V 和 ARM 的区别

尽管 RISC-V 和 ARM 处理器技术的功能相似,但也有显着区别。

1.

2023-06-21 20:31:32

RISC-V是一种开放式ISA(指令集体系结构),为处理器体系结构的创新开创了新纪元。RISC-V基金会由325多家成员公司组成。这是该技术的主要优势。软件架构师/固件工程师/软件开发

2020-07-27 17:38:30

siFive搞RISC-V

赛昉搞RISC-V

香山搞RISC-V

到底什么是RISC-V?

先不问有什么用,RISC-V目前的能力来说,工业有没有可能?

2024-02-02 10:41:21

什么是RISC-V?RISC-V指令具有哪些特点应用?自己怎么才能设计出设计一套指令集?

2021-10-14 09:05:03

并不多,也就是晚上下班后和周末玩玩,自己照着芯片手册写了几个例程在板子上跑跑而已。再后来发现网上已经有如何设计RISC-V处理器的书籍卖了,并且这个处理器是开源的,于是果断买了一本来阅读并浏览了它的开源

2022-08-22 18:25:55

都是跨平台、轻量级的工具。iverilog用来编译verilog代码,gtkwave用来查看波形。验证一个处理器,首先是能跑通各个指令,RISC-V官方提供了指令兼容性测试程序,这些程序是用汇

2022-08-23 15:05:44

、禁用和暂停计数器,无法使用任何可编程计数器和事件采样。不仅如此,RISC-V的perf不仅无法处理计数器溢出,也不支持溢出中断。虽然市面上很多RISC-V处理器已经考虑到了这一点,采用定制的形式来

2021-12-27 08:00:00

采用RISC-V架构的100亿颗处理器中,已有一半来自中国,这标志着中国RISC-V生态已初步形成。中国机构和开发者在RISC-V技术、应用及体系融合方面作出巨大贡献,得到了RISC-V国际基金会和全球开发者的肯定。

2023-05-28 08:45:58

RISC-V的软件生态快速推出市场。研发新的开源处理器项目,设定开源主线,获得更多技术和生态上的优势,对提升国内RISC-V各企业在国际RISC-V产业界的话语权和主导权,至关重要[6]。五、引用及参考材料[1] RISC-V董事长摊牌了: RISC-V不是开源处理器;

2020-06-22 16:47:55

0 RISC-V和其他开放架构有何不同如果仅从“免费”或“开放”这两点来评判,RISC-V架构并不是第一个做到免费或开放的处理器架构。在开始之前,我们先通过论述几个具有代表性的开放架构,来分析

2021-07-26 06:58:42

基于 RISC-V 处理器的开发板。LoFive FE310 开发板GroupGets LLC 的 LoFive-R1 开发板正是其中之一(图 1)。首先,LoFive R1 包含的 RISC-V

2020-08-21 18:35:32

CSR简介RISC-V 架构的控制和状态寄存器(Control and Status Register, CSR),用于配置或记录一些处理器核的运行状态。CSR寄存器是处理器核内部的寄存器,使用其

2022-08-25 15:51:38

RISC-V指令集体系结构(ISA)易于扩展,并且没有指定关于特定RISC-V微控制器或片上系统(SoC)实现的所有内容。因此,FreeRTOS RISC-V移植也是可扩展的-它提供了一个处理所有

2019-11-29 15:54:41

,并涌现了众多开源处理器及SoC采用RISC-V架构,这些处理器既有标量处理器,也有超标量处理器,既有单核处理器,也有多核处理器,本文接下来将简单介绍RISC-V架构的基本设计,随后将详细描述目前采用

2020-07-27 18:09:27

来源:内容来自「芯来科技 」,谢谢。日前,芯来科技的创始人胡振波发表了一场主题为《面向物联网的开源 RISC-V 处理器设计和开发》。直播中吸引了来自华为海思、紫光展锐、中兴微电子、中天微、AMD

2020-07-27 17:50:25

开发出商用的RISC-V处理器还需要哪些开发工具和环境?

处理器是软硬件的交汇点,所以必须有完善的编译器、开发工具和软件开发环境(IDE),处理器内核才能够被用户顺利使用起来。目前RISC-V具有

2023-11-18 06:05:15

使用,同时也容许企业添加自有指令集拓展而不必开放共享以实现差异化发展。 架构简单 RISC-V架构秉承简单的设计哲学。体现为: 在处理器领域,主流的架构为x86与ARM架构。x86与ARM架构的发展的过程

2023-03-19 10:52:16

比科奇宣布采用晶心科技32位RISC-V处理器核心AndesCore™ N25F,并搭配其AE350周边平台,打造5G小基站分布式单位(Distributed Unit)系统级芯片。比科奇为5G

2020-10-13 16:39:24

协处理器进行gpio操作,执行完成后 ULP RISC-V 协处理器退出,等待下一个ULP唤醒周期。可当在主MCU程序中使能 esp_sleep_enable_ulp_wakeup() 函数后,每当

2023-02-09 06:52:26

收授权费了,其价格也不低。RISC-V的流行对ARM来说就很尴尬了。传统的处理器IP公司,ARM还能通过商业运营扩大自己的优势,获取更大市场份额。RISC-V与其说是一种指令集,不如说是一种宗教。这种

2018-09-11 17:44:01

, 64位Linux兼容版U2,U7处理器。并着手于简化芯片设计领域的技术鸿沟,提供云端的模块化设计和验证程序。SIFIVE目前也是RISC-V领域产品系列最全,技术相对领先的公司。其它芯片设计公司

2020-08-02 11:50:33

修改不断添加新指令后,其指令编码中的寄存器索引位置变得非常的凌乱,给译码器造成了负担。得益于后发优势和总结了多年来处理器发展的教训,RISC-V的指令集编码非常的规整,指令所需的通用寄存器的索引

2020-07-27 17:47:26

`芯来科技为方便客户进行基于鸿蒙生态的RISC-V软件开发,在Nuclei RISC-V 32位处理器上移植并适配了鸿蒙LiteOS-M内核。目前该内核已可支持Nuclei Demo SoC

2021-04-08 13:59:02

我非常想了解如果想设计一个类似risc-v的处理器,整个开发流程是怎样的?

2023-12-09 18:39:01

如题,现在risc-v发展的如此迅猛,不知道这些处理器主要应用在哪些行业比较多呢?

2023-12-09 18:37:01

我在ULP RISC-V协处理器的例程中,没有发现有对ADC的操作,请问RISC-V协处理器目前还不支持吗?使用的IDF版本为4.4.2。我想在ULP模式下,通过ADC来读取外部器件的数据。

2023-02-13 06:34:36

我在ULP RISC-V协处理器的例程中,没有发现有对ADC的操作,请问RISC-V协处理器目前还不支持吗?使用的IDF版本为4.4.2。我想在ULP模式下,通过ADC来读取外部器件的数据。

2023-03-06 06:33:44

是由美国伯克利大学的 Krest 教授及其研究团队提出的,当时提出的初衷是为了计算机/电子类方向的学生做课程实践服务的。由于这是伯克利大学研究并流片的第五代RISC架构处理器,因此就命名为RISC-V

2023-09-28 11:58:35

开发的一种开放、免费且可定制的指令集架构,其目标是为各种应用提供高效、灵活的计算能力。玄铁处理器是由平头哥开发的一种高性能、低功耗的处理器,其基于RISC-V架构,并采用了自主研发的多核技术

2023-04-12 11:16:58

了RISC-V 联盟,这将加速RISC-V 芯片的研发。

可以看到RISC-V架构将成为芯片产业发展的重要组成部分,将为不同应用场景提供高性能、低功耗的处理器解决方案。

2023-05-14 09:05:11

芯来科技助力道生物联发布基于RISC-V内核的TurMass™标准无线终端SoC芯片—TK8610。该芯片产品采用芯来科技RISC-V N200系列处理器内核。

2022-03-22 15:00:19

面临应用碎片化、开发效率低、软硬件适配难等问题,软硬件生态尚未成熟。玄铁RISC-V系列处理器采用自研技术,覆盖从低功耗到高性能的各类场景,支持AliOS、FreeRTOS、RT-Thread

2021-10-20 14:09:00

https://github.com/JiaoXianjun/XiangShan谈到RISC-V,应该都会想到香山处理器。其经历了几代的演进,性能越来越高。采用Chisel Rocketchip框架,能够方便的定制属于你的RISC-V处理器。对此,你有什么看法?

2023-04-14 15:51:59

香山是什么2019 年,在中国科学院支持下,由 中国科学院计算技术研究所 牵头发起 “香山” 高性能开源 RISC-V 处理器项目,研发出目前国际上性能最高的开源高性能 RISC-V 处理器核

2022-04-07 14:20:44

随着这些年的发展,RISC-V的受重视程度与与日俱增。这主要因为它是免费的、灵活的,并且速度很快。这使RISC-V成为许多开发人员的安全便捷选择。但是您会认为RISC-V是通用RISC处理器还是定制的随心所欲处理器?

2020-11-17 16:11:56 3167

3167 IAR Systems专业的开发工具IAR Embedded Workbench for RISC-V现已能够支持Codasip的低功耗嵌入式处理器。

2021-12-02 13:46:59 1379

1379 芯来科技将正式采用芯华章自主研发的新一代智能验证系统穹景 (GalaxPSS)及数字仿真器穹鼎 (GalaxSim)等系列EDA验证产品,加速新一代复杂RISC-V处理器IP的设计研发。

2022-03-03 10:32:25 1968

1968 Imperas 产品组合以及来自快速发展的 RISC-V 生态系统的其他工具,为您今天开始自己的开放式处理器设计提供了足够的资源。

2022-06-01 10:00:27 1330

1330

Codasip 已在其 DV 测试平台中包含 Imperas 黄金参考模型,以确保有效的验证流程能够适应各种灵活的功能和选项,同时在未来内核的整个路线图中进行扩展,以实现对功能质量的严格确认。

2022-06-01 10:11:36 847

847 功能支持Codasip的RISC-V处理器。在固件加载到Codasip处理器上时,Veridify的安全算法就会对其进行验证,以使RISC-V开发人员确信嵌入式系统是安全可用的。 Veridify的安全

2022-07-06 16:06:07 985

985 德国慕尼黑 , 2022 年 8 月 31 日 – 处理器设计自动化和可定制RISC-V处理器知识产权(IP)的领导者Codasip日前宣布,将通过 Intel Ò Pathfinder

2022-09-02 15:36:02 374

374

该计划的开展也不只是英特尔一家来推动,英特尔还找了一批RISC-V生态伙伴来加入这个计划,比如SiFive、晶心科技、Codasip、MIPS、Cadence、Imperas和意法半导体等,他们都会为这个计划提供自己的解决方案。

2022-09-05 09:28:39 906

906 可定制RISC-V处理器知识产权(IP)的领导者Codasip日前宣布:已任命胡征宇(Julian Hu)为该公司大中华区总经理,以进一步满足区域内客户对可定制RISC-V处理器的强劲需求,并通过更完善的技术支持组织架构来助力本地区客户取得成功。

2022-10-20 09:43:49 687

687 SiliconArts光线追踪解决方案将采用Codasip的RISC-V处理器IP。Codasip Studio工具将支持客户为其图形应用实现高度优化。

2022-11-04 12:06:14 471

471 “ Codasip通过收购Cerberus增强RISC-V的安全性能,而业界需要对RISC-V的安全性足够重视 ” 2022年11月,德国慕尼黑 - 处理器设计自动化和可定制RISC-V处理器

2022-11-12 09:15:31 626

626 Codasip通过收购Cerberus增强RISC-V处理器设计的安全性 RISC-V的安全性问题需要得到高度重视 德国慕尼黑市,2022年11月 - 处理器设计自动化和RISC-V处理器硅知识产权

2022-11-16 19:37:05 486

486 在业界屡获奖项的Codasip L31是一个小型、高效的32位嵌入式RISC-V处理器核,针对低功耗的AI/ML应用,如物联网边缘设备等。凭借3级流水线、32个通用寄存器以及对谷歌

2023-02-28 10:45:30 390

390 处理器验证是一个全新的领域。我们知道 Arm 和 Intel 对处理器质量的期望设置了很高的标准。在 RISC-V 中,我们必须尝试并遵循这一点。

2023-03-22 15:19:32 380

380 转型RISC-V,大家才发现处理器验证绝非易事。新标准由于其新颖和灵活性而带来的新功能会在无意中产生规范和设计漏洞,因此处理器验证是处理器开发过程中一项非常重要的环节。

2023-06-01 09:07:01 370

370

随着RISC-V处理器的快速发展,如何保证其正确性成为了一个重要的问题。传统的测试方法只能覆盖一部分错误情况,而且无法完全保证处理器的正确性。因此,基于形式验证的方法成为了一个非常有前途的方法,可以更加全面地验证处理器的正确性。本文将介绍一种基于形式验证的高效RISC-V处理器验证方法。

2023-06-02 10:35:17 976

976 的客户现在可以根据同一授权协议和合同去购买一系列精选的SmartDV外设IP的授权。这一合作伙伴关系支持使用Codasip RISC-V处理器的芯片设计人员,通过使用已验证过兼容性和集成便捷性等特性

2023-07-03 16:13:04 464

464 在本文中,我们将以西门子EDA处理器验证应用程序为例,结合Codasip L31这款广受欢迎的RISC-V处理器IP提供的特性,来介绍一种利用先进的EDA工具,在实际设计工作中对处理器进行验证的具体方法。

2023-07-10 10:28:41 300

300

RISC-V的开放性允许定制和扩展基于 RISC-V 内核的架构和微架构,以满足特定需求。这种对设计自由的渴望也正在将验证部分的职责转移到不断壮大的开发人员社群。然而,随着越来越多的企业和开发人员转型RISC-V,大家才发现处理器验证绝非易事。

2023-07-10 09:42:08 413

413

RISC-V定制计算领域领导者 Codasip 今天宣布推出全新高度可配置的RISC-V基准处理器系列,旨在实现无限创新。该"700家族系列"包括应用和嵌入式处理器内核。700

2023-10-18 10:03:55 320

320 2023年10月19日, 思尔芯(S2C) 宣布 北京开源芯片研究院(简称“开芯院”) 在其历代“香山” RISC-V 处理器开发中采用了思尔芯的 芯神瞳 VU19P 原型验证系统

2023-10-24 16:28:17 317

317 2023年10月19日,思尔芯(S2C)宣布北京开源芯片研究院(简称“开芯院”)在其历代“香山”RISC-V处理器开发中采用了思尔芯的芯神瞳VU19P原型验证系统,不仅加速了产品迭代,还助力多家企业

2023-10-25 08:24:04 302

302

电子发烧友App

电子发烧友App

评论