数字化技术正在极大地改变着我们的生活和体验。作为数字化技术的基石,数字信号处理(DSP)技术已经、正在、并且还将在其中扮演一个不可或缺的角色。DSP的核心是算法与实现,越来越多的人正在认识、熟悉和使用它。因此,理性地评价DSP器件的优缺点,及时了解DSP的现状以及发展趋势,正确使用DSP芯片,才有可能真正发挥出DSP的作用。

DSP器件与算法

DSP(数字信号处理器)作为一种微处理器,其设计的出发点和通用CPU以及MCU等处理器是不同的。DSP是为完成实时数字信号处理任务而设计的,算法的高效实现是DSP器件的设计核心。DSP在体系结构设计方面的很多考虑都可以追溯到算法自身的特点。我们可以通过考察一个FIR滤波器的I/O关系,即,来了解这两者之间的对应关系,如表1所示。

通过表1,可看出DSP器件和算法之间的必然联系。这不仅是芯片设计人员必须考虑的问题,也是芯片使用者必须了解的。

图1 C62x和C64x DSP内核的数据路径图

图2 C64x DSP的两级Cache机制

现代数字信号处理器的特点和发展趋势

DSP器件的发展,必须兼顾3P的因素,即性能 (performance) 、功耗 (power consumption) 和价格 (price)。总的来说,随着VLSI技术的高速发展,现代DSP器件在价格显著下降的同时,仍然保持着性能的不断提升和单位运算量的功耗不断降低。下面我们主要以TI公司的DSP为例来说明现代DSP芯片的一些特点和发展趋势。

通过并行提升DSP芯片的性能

传统的DSP芯片通过采用乘加单元和改进的哈佛结构,使其运算能力大大超越了传统的微处理器。一个合理的推论是:通过增加片上运算单元的个数以及相应的连接这些运算单元的总线数目,就可以成倍地提升芯片的总体运算能力。当然,这个推论有两个前提条件必须满足:首先是存储器的带宽必须能够满足由于总线数目增加所带来的数据吞吐量的提高;另外,多个功能单元并行工作所涉及的调度算法其复杂度必须是可实现的。

1997年,TI发布了基于VLIW (超长指令字) 体系结构的C62x DSP内核。它在片内集成了两组完全相同的功能单元,各包括一个ALU(算术及逻辑单元)、一个乘法单元、一个移位单元和一个地址产生单元。这8个功能单元通过各自的总线与两组寄存器组连接。理想情况下,这8个功能单元可以完全并行,从而在单周期内执行8条指令操作。VLIW体系结构使得DSP芯片的性能得到了大幅提升。在此基础上,TI又发布了C64x DSP内核,其主要改进之处在于进一步加宽了寄存器组与内存之间的总线宽度,以及改善了单个功能单元对于SIMD (单指令多数据) 操作的支持等。图1分别给出了C62x和C64x DSP内核的数据路径示意图。

VLIW结构对功能单元采用静态调度的策略,DSP内部只完成简单的指令分发,调度算法的实现可以由编译器完成,用户也可以通过手工编写汇编代码的形式实现自主调度。其好处是DSP芯片的使用难度大大降低。通过使用高效的C语言编译器,普通用户也可以开发出具有较高效率的DSP运行程序。

存储器构架的变化

随着芯片主频的不断攀升,存储器的访问速度日益成为系统性能提升的瓶颈。在现有的制造工艺下,片上存储单元的增加将导致数据线负载电容的增加,影响到数据线上信号的开关时间,这意味着片上高速存储单元的增加将是十分有限的。为了解决存储器速度与CPU内核速度不匹配的问题,高性能的CPU普遍采用Cache(高速缓存)机制,新的DSP芯片也开始采用这种结构。以TI的C64x DSP为例,它采用两级Cache的结构,如图2所示。L1 Cache分为独立的程序缓存 (L1P) 和数据缓存 (L1D) ,其大小各为16KBytes,访问速度与DSP内核的运行时钟相匹配,L2 Cache则采用统一的形式管理,其大小从256KB到1MB不等,访问速度相比L1 cache大大降低。L2 Cache通过DMA与外部低速的存储器件进行数据交换。为增加Cache的命中率,C64x的Cache还采用了多路径的结构形式。研究表明,在很多情况下,采用这种多级缓存的架构可以达到采用完全片上存储器结构的系统约80%的执行效率。但是,采用Cache机制也在一定程度上增加了系统执行时间的不确定性,其对于实时系统的影响需要用户认真地加以分析和评估。

Cache对于DSP芯片还是一个比较新的概念。DSP开发人员需要更深入地了解Cache的机制,相应地对算法的数据结构、处理流程以及程序结构等做出调整,以提高Cache的命中率,从而更有效地发挥Cache的作用。

SoC的趋势

对于特定的终端应用,SoC (系统芯片) 可以兼顾体积、功耗和成本等诸多因素,因而逐渐成为芯片设计的主流。DSP器件也逐渐从传统的通用型处理器中分离出更多的直接面向特定应用的SoC器件。这些SoC器件多采用DSP+ARM的双核结构,既可以满足核心算法的实现需求,又能够满足网络传输和用户界面等需求。同时,越来越多的专用接口以及协处理器被集成到芯片中,用户只需添加极少的外部芯片,即可构成一个完整的应用系统。以TI公司为例,其推出的面向第3代无线通信终端的OMAP1510芯片等,面向数码相机的DM270芯片等,面向专业音频设备的DA610芯片等,面向媒体处理的DM642芯片等,都是SoC的典型例子。

DSP器件的应用

世界上没有完美的处理器,DSP不是万能的。DSP器件的特点使得它特别适合嵌入式的实时数字信号处理任务。

实时的概念

实时的定义因具体应用而异。一般而言,对于逐样本 (sample-by-sample) 处理的系统,如果对单次样本的处理可以在相邻两次采样的时间间隔之内完成,我们就称这个系统满足实时性的要求。即:tproess>tsample,其中,tproess代表系统对单次采样样本的处理时间,tsample代表两次采样之间的时间间隔。举例来说,某个系统要对输入信号进行滤波,采用的是一个100阶的FIR滤波器,即。假设系统的采样率为1KHz,如果系统在1ms之内可以完成一次100阶的FIR滤波运算,我们就认为这个系统满足实时性的要求。如果采样率提高到10KHz,那么实时性条件也相应提高,系统必须在0.1ms内完成所有的运算。需要注意,tproess还应当考虑各种系统开销,包括中断的响应时间,数据的吞吐时间等。

正确理解实时的概念是很重要的。工程实现的原则是“量体裁衣”,即从工程的实际需要出发设计系统,选择最合适的方案。对于DSP的工程实现而言,脱离系统的实时性要求,盲目选择高性能的DSP器件是不科学的,因为这意味着系统复杂度、可靠性设计、生产工艺、开发时间、开发成本以及生产成本等方面不必要的开销。从这个角度而言,即使系统开发成功,整个工程项目可能仍然是失败的。

嵌入式应用

嵌入式应用对系统成本、体积和功耗等因素敏感。DSP器件在这些方面都具有可比的优势,因此DSP器件特别适合嵌入式的实时数字信号处理应用。反过来,对于某一个具体的嵌入式的实时数字信号处理任务,DSP却往往不是唯一的,或者是最佳的解决方案。我们看到,越来越多的嵌入式RISC处理器开始增强数字信号处理的功能;FPGA厂商为DSP应用所做的努力一直没有停止过;针对某项特定应用的ASIC/ASSP器件的推出时间也越来越快。开发人员面临的问题是如何根据实际的应用需求客观地评价和选择处理器件。表2对给出了这些器件之间的一些简要对比。

从表中可以看出,DSP实际上是一种比较折衷的解决方案。以媒体处理应用为例,现行的国际标准较多,包括MPEG1/2/4、H261/3/4等,各种标准在一段时间内共存,新的标准还在不断涌现。如果系统设计需要兼顾实现性能和多标准的适应性,DSP可能是一个较好的选择。但是,如果应用比较固定,对价格又特别敏感,采用专用的ASIC芯片可能就会更加合适。

算法是DSP应用的核心

随着DSP器件的发展,DSP系统开发的主要工作已经转向软件开发,软件开发将占据约80%的工作量,必须引起足够的重视。另外,在目前的现状条件下,算法是我们核心知识产权的主要体现,也是产品竞争力的主要因素。因此在最后,笔者仍然希望强调:算法是DSP应用的核心。

DSP器件的特点及其应

DSP的五大发展趋势

CRM软件发展趋势预测?

Multicom发展趋势如何?它面临哪些挑战?

PCB发展趋势,六大趋势

PLC的未来发展趋势的三个方向

TPMS技术与发展趋势

WIFI技术原理及发展趋势

为什说数码产品的发展趋势决定晶振的发展趋势

传感器将会有哪些发展趋势?

先进封装技术的发展趋势

光伏并网逆变器的发展趋势

单片机的发展趋势

单片机的发展趋势

大功率IGBT驱动的技术特点及发展趋势分析

工业电机行业现状及未来发展趋势分析

广电业务发展趋势与业务捆绑技术

开关电源发展趋势及发展前景

开关电源的发展趋势和方向

您看好电动汽车的未来发展趋势吗?

我国智能传感器发展趋势分析!

数字电源的定义、分类及发展趋势

智能制造中木工机械发展趋势怎样

未来触控产品发展趋势3

物联网未来发展趋势

物联网未来发展趋势如何?

电源管理技术的三大创新发展趋势

直流充电桩的发展趋势

磁传感器未来发展趋势特点分析

DSP未来发展趋势分析

27

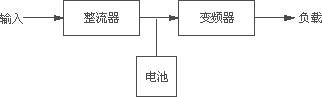

27UPS及EPS的应用技术与发展趋势

1641

1641

DSP技术应用现状以及发展趋势

19

19dsp数字处理芯片的原理、特点、应用和发展趋势

8519

8519 电子发烧友App

电子发烧友App

评论