大咖简介: 胡振波是上海交大本科研究生,具有超过10年处理器研发经验。 在Mavell和Synopsys等知名企业领导多款高性能和低功耗处理器研发工作。 是国内RISC-V社区领袖,以及蜂鸟E203

2020-11-10 15:17:21 3036

3036 胡振波老师的E203处理器让小编受益匪浅,十分感激!E203 CPU的设计非常经典且精简,大量逻辑复用,追求极低功耗、极小面积。

2022-09-27 10:21:19 1788

1788 一、队伍介绍

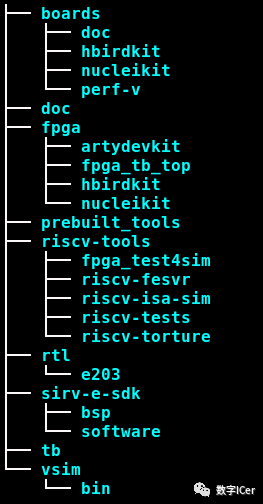

本篇为蜂鸟E203系列分享第五篇,本篇介绍的内容是E203 代码结构梳理。

二、层次图

三、模块具体功能

2025-10-30 06:56:37

/e203_subsys_top.v(your_e203)/vsim/install/rtl/e203/soc/e203_soc_top.vFilelist文件可以嵌套使用。完成上述工作后,正常进行编译仿真即可。

2025-10-24 07:02:48

/subsys/e203_subsys_perips.v中例化了sirv_icb1to16_bus,sirv_icb1to16_bus.v在e203/rtl/fab中,是⼀个有16外设的总线包装

2025-10-24 07:14:07

的system.v文件以及引脚约束文件,和rtl文件夹内的源码,我们参考源码绘制了E203在MCU200T的时钟树,方便我们团队对E203源码的时钟进行修改,分享如下:

2025-10-29 07:25:15

笔者参照原 E203 的代码增加了实现浮点指令的电路,因此会将原 E203 的代码与自己的思路对比着讲。

1. OITF 分配 tag 的时序

《手把手教你设计CPU——RISC-V处理器篇》讲到

2025-10-24 13:28:31

哪些代码。程序亦可以改写 CSR 使得机器进入某些状态。

按照 RISC-V 的规定,浮点指令的实现需要另外设置一个32位的控制状态寄存器。由于 E203 已经实现了 32 位的整数部分的控制状态寄存器

2025-10-24 13:25:02

RISC-V 指令手册来写,格式上可以参照原 E203 的 decode 模块的代码。这些代码并不复杂,但很繁琐,因此写的时候需要有一定的耐心。

由于 minidec 例化了 decode 模块

2025-10-24 13:54:29

《在手把手教你RISC-V CPU上》

3.F拓展的软件实现

为实现对蜂鸟E203的F拓展,笔者未采用蜂鸟E203中遗存的FPU端口,选择NICE接口完成蜂鸟E203浮点运算指令拓展,在NICE端口

2025-10-20 09:23:24

,如何让E203能够在软件仿真的环境下运行自己编写的C语言代码呢?

以下是我们的方案。

首先,hbird-sdkapplicationbaremetal目录下放置着一些测试程序,以helloworld为

2025-10-20 09:38:28

本文将分享我们团队提高E203软核主频的办法。

查阅芯来科技官方出版的《手把手教你设计CPU——RISC-V处理器篇》教材,我们发现,原本设计的E203主时钟域应该是100MHZ

2025-10-29 06:19:19

RISC-V 手册 一本开源指令集的指南

本书是由 RISC-V 设计者 DAVID PATTERSON等亲自写的书。书写的非常精彩,和Risc-V一样非常简洁明了,没有废话,书本身也不厚,114页也就把Risc-V的指令架构给讲清楚了。由包云岗等几位老师翻译成中文了。

2022-04-22 18:04:26

B扩展简介

RISCV B扩展指的是RISCV用于位运算加速的一个扩展指令集,目的是使用一条指令实现原本需要2-3条指令才能实现的位操作指令。具体包含内容如下:

B扩展就是RISC-V一个可选

2025-10-21 13:01:45

。RISC-V指令集有RV32I、RV32E、RV64I、RV64E、RV64I等等,RV代表RISC-V,32/64代表32位或64位,I和E都是基本指令集,在I和E的基础上,可以添加D(双精度浮点扩展

2023-04-14 10:18:23

2023 年 RISC-V 中国峰会上,倪光南院士表示,“RISC-V 的未来在中国,而中国半导体芯片产业也需要 RISC-V,开源的 RISC-V 已成为中国业界最受欢迎的芯片架构”。大家怎么看呢?

2023-08-26 14:16:43

具体方法

这篇分享中RISC-V 蜂鸟E203平台是在Arty A7 100T上进行的搭建,ddr 200t的板子上是有2块qspi flash的,所有FPGA的bitstream烧录在了

2025-10-28 07:47:08

具体方法

E203的源码请参考链接:

https://github.com/riscv-mcu/e203_hbirdv2

E203的overview链接:

https

2025-10-28 06:26:05

,一步到位哟。overview就是对E203的整个平台做了整体介绍,有什么样的外设,如何烧录等等。最主要看第四节的交叉编译环境的安装,安装RISC-V GNU toolchain、Nuclei

2025-10-28 06:16:38

本期文章目录一个小型RISC-V开源处理器核介绍!#SOC#FPGA#RISC-V点击阅读数字积木从零开始写RISC-V处理器(超详细)#RISC-V点击阅读数字积木为什么说模拟工程...

2021-07-23 09:42:00

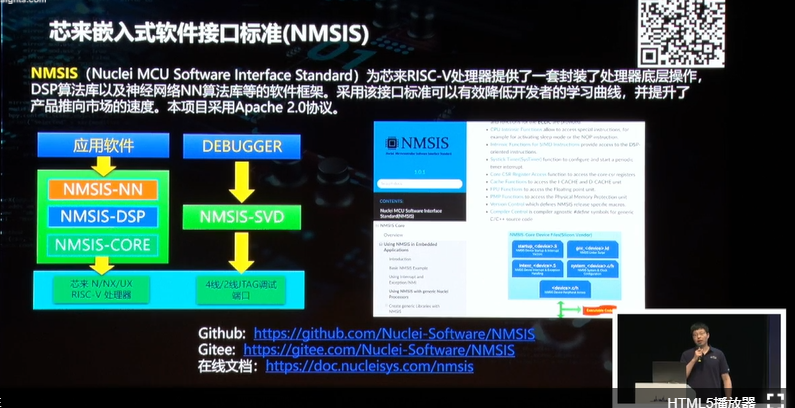

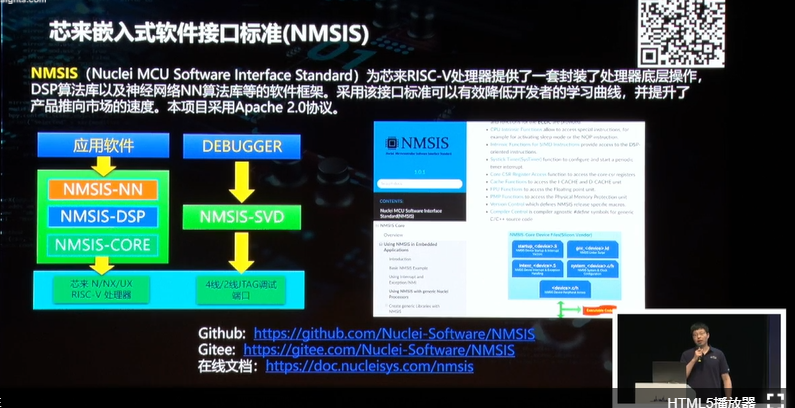

由于RISC-V对外是开源的,各个厂家定制个性化内核,各厂家研发的产品能否兼容,做到一个生态中呢?

2023-04-21 10:06:08

很多公司觉得ARM收费太高,决定一起搞RISC-V架构,是不是这种开源的是不是不收费的;那和ARM有啥区别,能发展起来吗

2023-10-30 06:38:57

请问RISC-V开源项目有哪些?

2023-04-14 15:38:03

RISC-V单片机仿真器是通用 的么

2023-09-22 07:18:03

RISC-V和开源处理器之间是什么关系?

2023-03-09 10:06:52

RISC-V在MCU中有哪些知名的开源项目?

2024-12-30 19:48:08

RISC-V嵌入式开发准备篇2:嵌入式开发的特点介绍随着国内第一本RISC-V中文书籍《手把手教你设计CPU——RISC-V处理器篇》 正式上市,越来越多的爱好者开始使用开源的蜂鸟E203

2021-11-08 08:33:47

成熟流行商业内核架构在于,RISC-V是属于开源的内核架构,并且最为重要的一点是,发布RISC-V的基金会和研发机构,允许商家在RISC-V架构上进行非标准的指令扩展,同时不需要对外公开。这样有利于...

2021-07-23 06:06:39

RISC-V是什么?有哪些特点?如何去设计RISC-V处理器?

2021-06-18 09:24:03

RISC-V有没有类似ARM的CMSIS-DAP,比较好的开源仿真器硬件项目?

2023-04-03 17:50:35

回顾过去几年的集成电路产业里,RISC-V是一个绕不过去的热词。作为一项以“开源”为卖点的技术,RISC-V自面世以来,就在相对古板的处理器设计领域激起了不小的浪花。由于RISC-V的开源特性造就了

2020-06-22 16:55:03

RISC-V作为一种开源的指令集架构(ISA),具有一系列显著的优点和潜在的缺点。以下是RISC-V的主要优点和缺点概述:

优点 :

开源与开放性 :RISC-V是开源的,这意味着任何人都可以获取

2024-04-28 08:51:42

RISC-V架构 RISC-V(发音为“risk-five”)是一个基于精简指令集(RISC)原则的开源指令集架构(ISA)。 与大多数指令集相比,RISC-V指令集可以自由地用于任何目的

2023-04-03 15:29:09

集(RISC)原则的开源指令集架构(ISA)。与大多数指令集相比,RISC-V指令集可以自由地用于任何目的,允许任何人设计、制造和销售RISC-V芯片和软件而不必支付给任何公司专利费。R...

2021-07-28 07:46:13

1 完全开源对指令集使用,RISC-V基金会不收取高额的授权费。开源采用宽松的BSD协议,企业完全自由免费使用,同时也容许企业添加自有指令集拓展而不必开放共享以实现差异化发展。2 架构简单

2021-06-18 19:41:21

一.设计背景RISC-V,第五代开源 RISC 指令集架构,作为近年来开源芯片技术的突出代表,受到国内外各领域的广泛关注。为了进一步促进 RISC-V 在嵌入式等领域的应用,江苏省计算机学会、单片机

2021-12-09 08:05:37

RISC-V简介 RISC-V 是一个自由和开放的 ISA(开源指令集架构),通过开放的标准协作实现处理器创新的新时代。RISC-V ISA在架构上提供了一个新的自由、可扩展的软件和硬件自由级别

2023-02-27 19:56:30

刚开始接触学习e203,仿真的第一步就遇上问题。按照手册在linux环境下跑仿真遇到如图错误:

有人说是e203版本问题,遂下载了更早的版本:

https://github.com

2025-11-05 13:39:04

E203写回逻辑的基础上,在原本的基础上增加关于FPU的通路。自行增加输出仲裁。

csr模块

csr主要负责储存系统运行的一些信息和控制系统的某些状态。依照RISC-V官方手册,扩展FPU的csr主要需要增加csr_mstatus 中的fs寄存器的一些控制功能,以及一个32位的fcsr寄存器。

2025-10-21 11:51:02

1.简述

这里就不详细介绍risc-v和蜂鸟e203,大家应该都比较了解了。蜂鸟e203工程比较完善,也有一本书介绍,讲解还是非常详细的,如果以后想从事数字IC或者想学习risc-v,蜂鸟e203

2025-10-31 08:07:44

1.简述

经过不懈的努力,终于成功运行hello word程序,这是一个极低成本的学习方案,感兴趣继续往下看。

2.准备

修改e200工程,这部分可以参考:开源RISC-V处理器(蜂鸟

2025-10-31 06:04:21

1.简述

首先感谢芯来开源了蜂鸟E203 risc-v处理器,提供了比较完整的工程环境、配套的软硬件。但是配套的FPGA板卡实在太贵,对于自费学习的来说是不小的学习成本,而且我也认为完备环境

2025-10-31 08:46:40

除了tinyrisc-v有没有代码比较清晰,移植性比较好,且比较简单,适合学习的开源risc-v

2023-05-06 19:24:39

开源的蜂鸟E203可以直接用来流片吗

2023-08-12 08:11:15

环境:Ubuntu20.04、Iverilog12.0、gtkwave3.3.103

内容:Iverilog仿真e203_hbirdv2跑RISC-V指令测试用例

要点:

下载安装

2025-10-27 08:24:00

下载蜂鸟E203源码

https://gitee.com/riscv-mcu/e203_hbirdv2?_from=gitee_search

新建个文件夹

把rtl/e203下面所有的文件放到

2025-10-27 07:35:50

队伍编号:CICC1304

系统:win10/Ubuntu20.02 NucleiStudio:2022.12

FPGA:AX7050B

在将E203的比特流下载到FPGA上后,我们

2025-10-20 09:24:17

与 CPU 龙头老大的 Intel、ARM 三分天下,谈何容易,可偏偏这个在 2010 年才诞生的 RISC-V 就有这样的势头。作为目前为数不多的开源硬件,RISC-V 完全开放,基于广泛使用且

2023-02-27 20:02:18

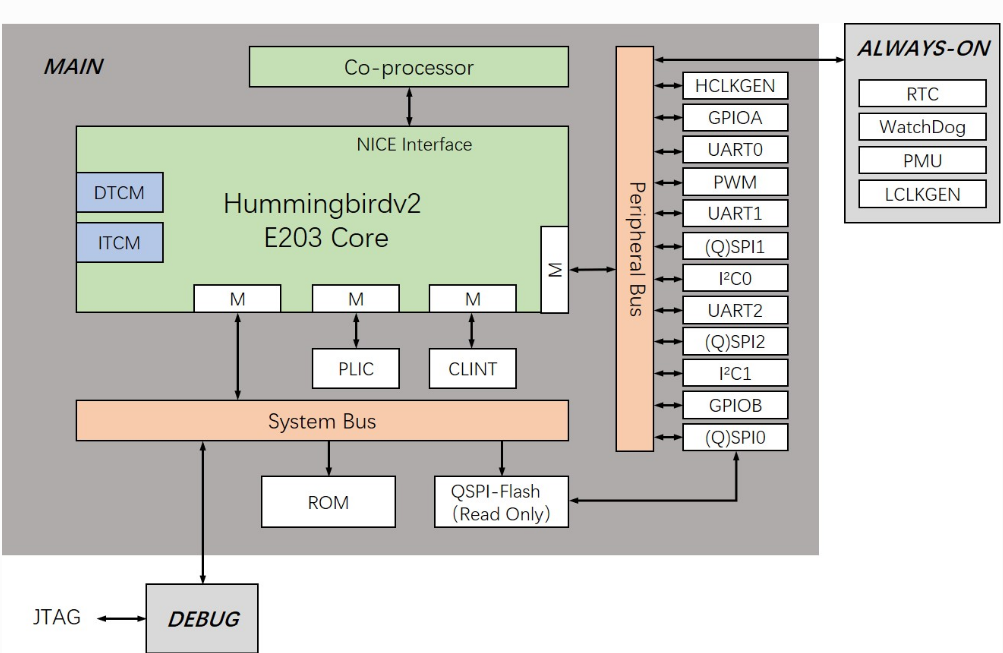

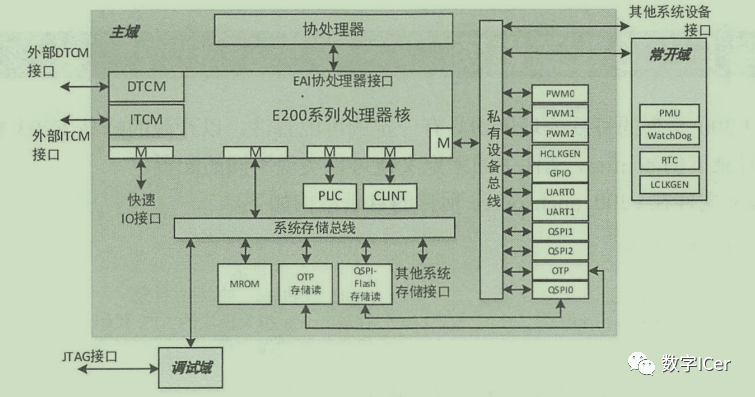

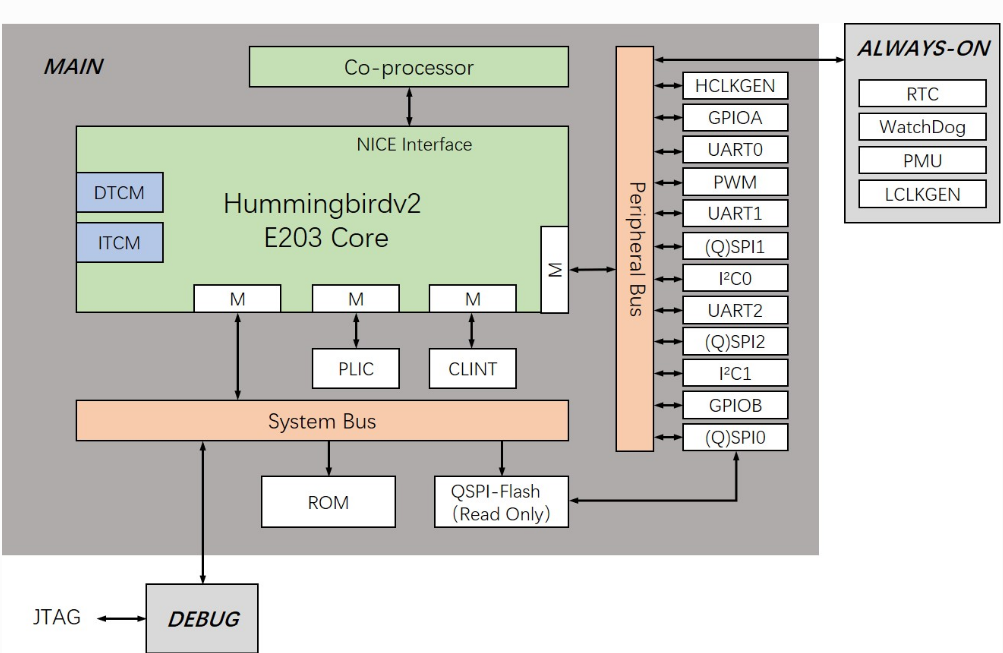

予以介绍。完整的 FPGA 开发板原型(包括 FPGA 开发板和MCU调试器)如下图所示:蜂鸟E203开源SoC对于一个处理器核,还需要配套的 SoC 才能具备完整的功能。蜂鸟 E203 内核不仅仅

2022-07-26 22:00:29

siFive搞RISC-V

赛昉搞RISC-V

香山搞RISC-V

到底什么是RISC-V?

先不问有什么用,RISC-V目前的能力来说,工业有没有可能?

2024-02-02 10:41:21

什么是RISC-V?RISC-V指令具有哪些特点应用?自己怎么才能设计出设计一套指令集?

2021-10-14 09:05:03

E203的SOC的模块图中的这个模块是FLASH的控制器吗?

如果我想完成FLASH的读写控制的话,在SOC的代码层面(.v文件)该如何实现波形仿真呢?

2023-08-11 12:38:55

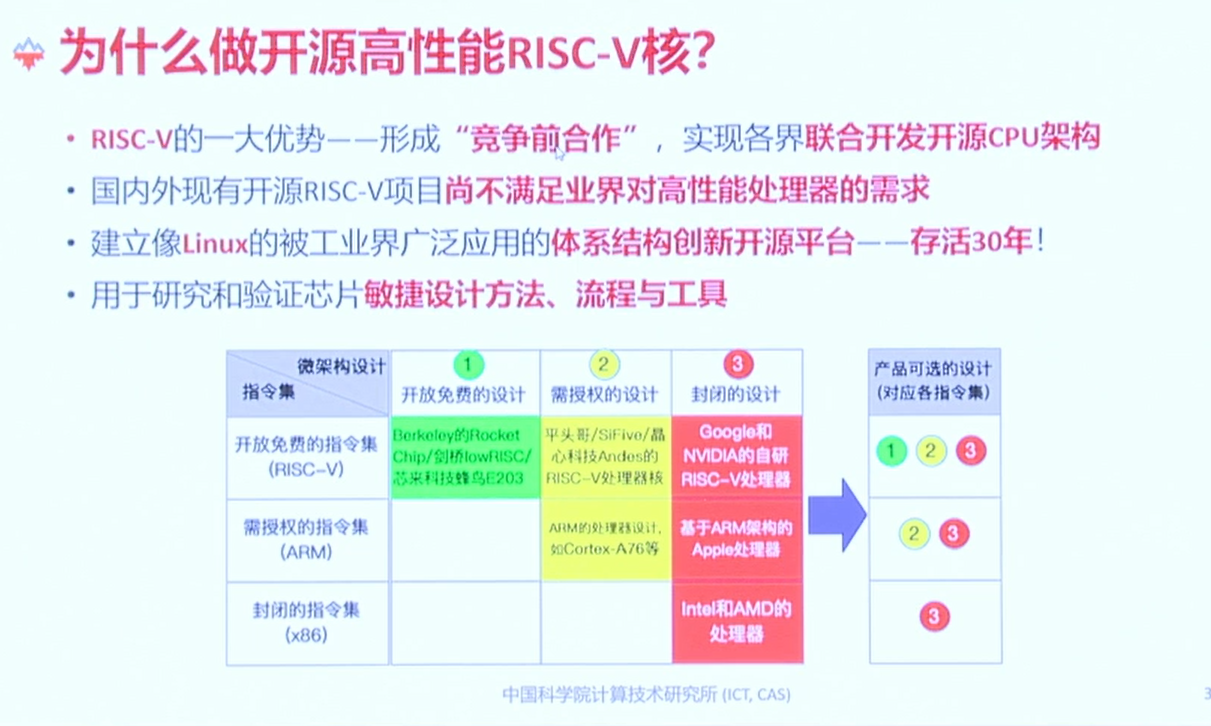

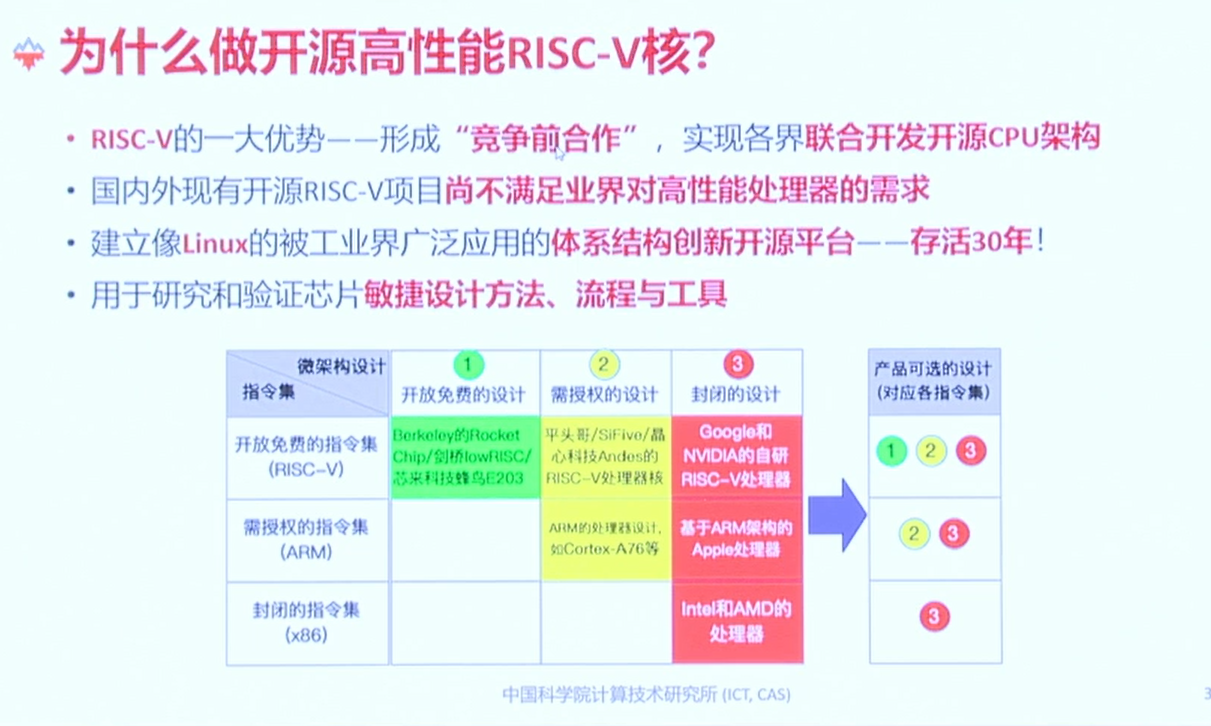

存在三种不同的商业模式,分析图3第一行,开放免费的指令集(RISC-V)包含了三种模式的微架构设计[5]:开源模式,Berkeley的Rocket Chip、剑桥大学的lowRISC、蜂鸟E203等

2020-06-22 16:47:55

RISC-V芯片作为一种基于精简指令集计算(RISC)原则的开源指令集架构(ISA)芯片,近年来在多个领域展现出了广泛的应用潜力和显著优势。以下是对RISC-V芯片应用的总结。

RISC-V芯片

2025-01-29 08:38:00

本人发现还有许多朋友在寻找如何仿真蜂鸟E203的方法,并且目前论坛内还没出现过一代蜂鸟E203(基于hbirdkit和nucleikit)仿真教程,由于本人使用的板子便是hbirdkit,因此特来

2025-10-31 06:14:34

请问在开源的E203的AXI总线支持burst传输吗?在sirv_gnrl_icb2axi.v模块中看到了

请问如何使用呢?相应的在NucleiStudio中的代码中需要做什么修改呢?有大佬指点一下想要使用AXI做burst传输具体需要做那些步骤呢?

2023-08-12 06:13:08

的默认证书就可以正常使用了。 首先我们需要把FPGA变成一块RISC-V的开发板,因此需要烧录蜂鸟E203的bitstream,接下来就是把它当做单片机一样使用,上传固件了。 下载源码 为了方便

2022-09-16 16:15:39

在Ubuntu 虚拟机中使用verilator对蜂鸟E203内核进行仿真

蜂鸟E203是一款基于RISC-V架构的嵌入式处理器核,在开发中需要进行仿真操作来验证其功能性。本教程将介绍如何利用

2025-10-27 08:22:44

指令蜂鸟E203借鉴了开源RISC-V处理器Rocket Core的协处理器接口RoCC,为了与原始接口进行区分,命名为EAI(Extension Accelerator Interface)接口

2025-10-28 06:18:41

采用了握手信号进行传输;而在e203的内部也给我们提供了一份icb转换为axi的示例,其位于/subsys/ e203_subsys_mems.v文件中,我们可将其层层引出直至顶层当作一个

2025-10-23 06:22:22

由于e203内部DTCM空间较小,所以本队针对DDR200T开发板进行针对e203的DDR3存储器扩展。

论坛中所给出的e203扩展DDR的方法大致分为两种,一种是直接将DDR存储器的接口使用ICB

2025-10-21 12:43:40

蜂鸟E203是一款基于RISC-V架构的微处理器,其指令集包含RV32I的基本指令集,RV32M的乘法扩展指令集,以及一些常用的定点指令和控制指令。如果需要扩展其指令集,可以考虑使用RISC-V的可

2025-10-21 09:38:47

,具体的移植感兴趣也可以对照仓库代码详细看。2. Picorv32首先介绍一下 picorv32,它也是一个 Verilog 实现的开源 RISC-V 软核这里流程和蜂鸟E203略有区别,因为

2022-04-01 11:48:28

蜂鸟E203是一款基于RISC-V指令集的多核处理器,内置了乘法和除法运算单元,这些运算单元的性能直接影响到整个处理器的性能表现。因此,优化乘除法器是提高整个处理器性能的重要手段之一。

一、原理介绍

2025-10-24 06:47:29

,另一方面得益于日渐成熟的软件生态,UCB提供了针对RISC-V的开源编译器GCC、LLVM,还提供了开源仿真器Spike、QEMU,社区还移植了FreeBSD、Debian、Gentoo、Yocto

2020-07-27 18:09:27

爱好者和初学者快速上手 RISC-V,所以我开发了一个使用工业级 Verilog 标准开发的开源 RISC-V 内核(蜂鸟 E203)上传至 Github,希望能够为国内的科教领域提供一个简单易上手

2020-07-27 17:50:25

其实很早以前就知道RISC-V,但是从来都没有接触过,因为当时做的人还比较少,自从开源了之后,国内国外很多的厂家都开是使用RISC-V来研发自己的芯片,包括国内的很多厂家,比如平头哥,北京兆易创新

2023-03-19 10:52:16

请问有哪些RISC-V和GPU结合的开源项目

2023-04-14 15:41:52

首先讲一下我的操作过程吧。

首先,我下载了开源的蜂鸟E203处理器,新建了一个自己的vivado工程,并将rtl目录里的所有.v文件和fpga目录里的一个system.v文件加入到我的工程里,并添加

2023-08-16 08:23:26

RISC-V相对于ARM的优势主要体现在以下几个方面:

开源与免费:

RISC-V是一个完全开源的指令集架构(ISA),其规范公开且可以免费使用。这意味着任何人都可以基于RISC-V设计、制造和销售

2024-06-27 08:45:28

的RISC-V处理器内核IP和解决方案公司,并创造了我国第一颗开源RISC-V处理器项目蜂鸟E203。2019年1月芯来科技完成了千万级人民币的天使轮融资。有数据显示,中国有300家以上公司在关注

2020-08-02 11:50:33

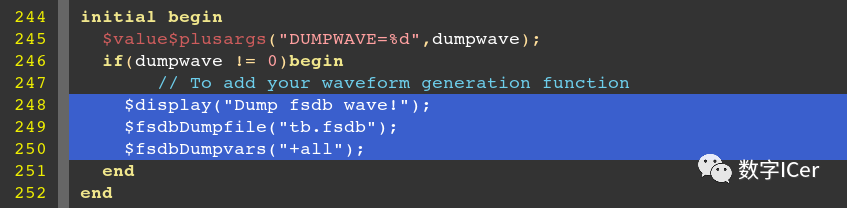

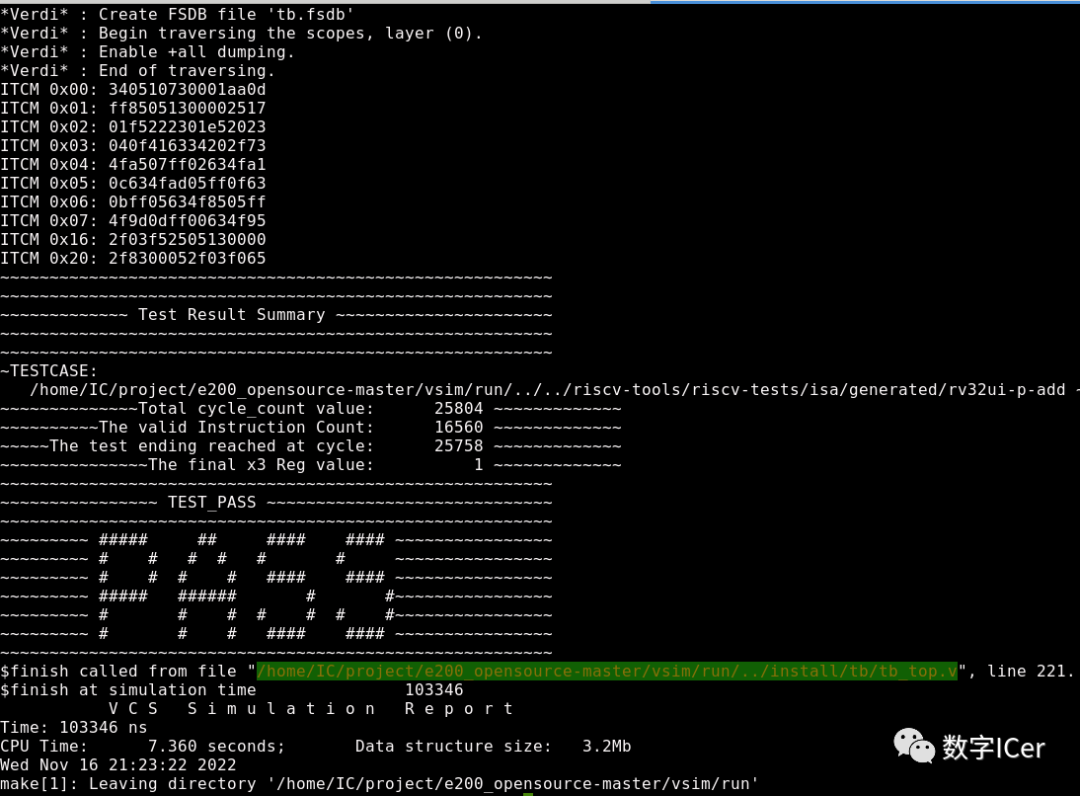

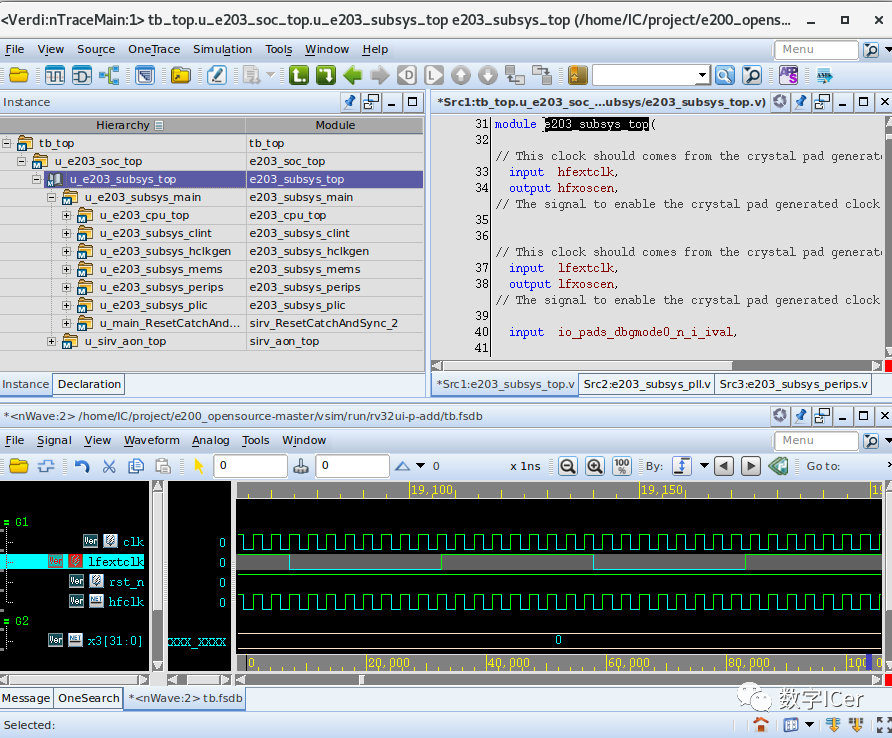

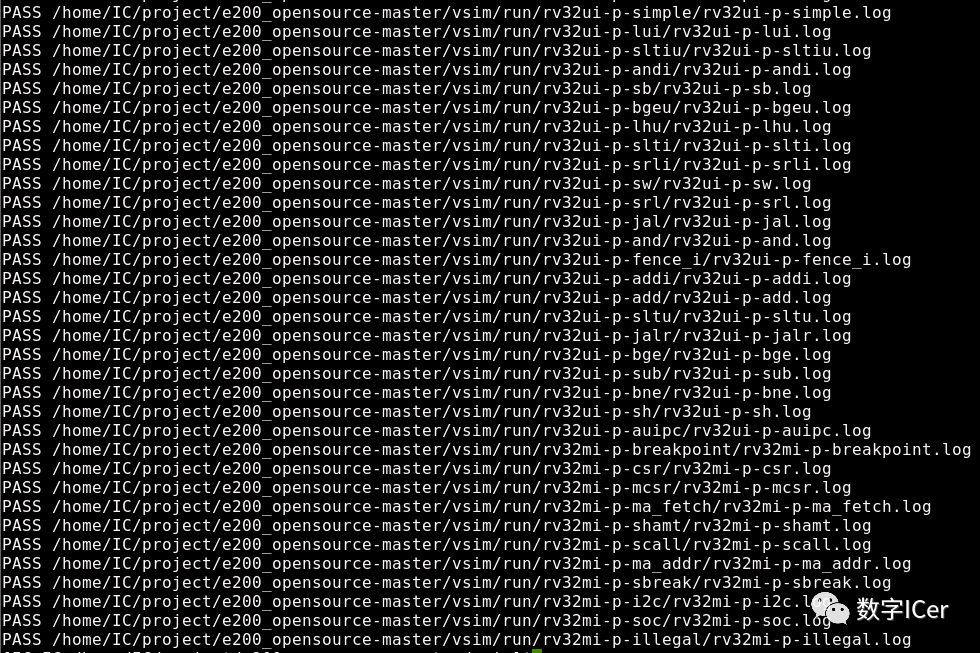

根据上次的分享,已经把e203成到verdi与vcs仿真环境下。这次简单介绍一下e203的仿真文件与itcm固化程序的仿真。

仿真文件

简单分析一下e203的自带的仿真文件,跟着上次的分享,我们

2025-10-27 06:04:31

芯片春秋 开源架构RISC-V前世今生

2020-05-21 10:04:10

64MBit SDRAM,丰富的LVDS引脚,内置12-bit 1MSPS ADC ,这为荔枝糖提供了无限的可能性:FPGA可以模拟“HummingbirdE200/E203 RISC-V软核”来帮助

2018-10-18 14:02:31

周期。

总结

本文介绍的内容是为了完成基础功能:对蜂鸟E203 RISC-V内核的微架构实现进行一定优化,在添加F拓展的过程中的一些记录。

2025-10-24 08:57:20

我想基于e203处理器进行指令集扩展,可是e203的EAI模块并没有开源,请问有没有好的例子、教程或者代码可以参考,因为如果自己写的话感觉需要考虑的东西太多了,需要修改的代码也太多了。谢谢!

2025-11-07 07:42:19

科技有限公司发起成立,负责openKylin社区中桌面操作系统上RISC-V架构平台的开源多媒体框架(FFMPG/Gstreamer/OpenMax)集成及应用开发工作。01 SIG目标创建并负责

2023-04-03 18:33:36

,如何让E203能够在软件仿真的环境下运行自己编写的C语言代码呢?

以下是我们的方案。

首先,hbird-sdkapplicationbaremetal目录下放置着一些测试程序,以helloworld

2025-10-20 06:44:14

开放生态的想象力。目前,玄铁系列处理器出货超25亿颗,拥有150余家客户、超500个授权数,已成为国内应用规模最大的国产CPU。此次开源的玄铁系列RISC-V处理器,包括玄铁E902、E

2021-10-20 14:09:00

为了便于初学者能够快速地学习RISC-V CPU设计和RISC-V嵌入式开发,蜂鸟E203开源MCU原型SoC定制了基于Xilinx FPGA的专用开发板和专用JTAG调试器。

2018-11-12 17:10:02 22353

22353 RISC-V 在冥冥之中似乎注定会走开源路线。

2020-04-27 10:04:40 1501

1501 RISC-V的关注度越来越高,开源的理念也正在被越来越多的开发者和公司接受。对于尚不成熟的RISC-V而言,无论是规范和技术的演进还是生态的建设,还有人才和专利都还有不小挑战。2021年RISC-V

2021-02-11 10:10:00 3975

3975 RISC-V是一个基于精简指令集原则的开源指令集架构,那么为什么做开源高性能RISC-v核?

2021-06-22 14:25:40 3289

3289

本文从RISC-V软件开源基础平台、RISC-V多样化软件生态以及RISC-V开源社区等三个方面详细介绍了如何建设RISC-V软件生态。

2021-06-23 11:21:04 3996

3996

RISC-V嵌入式开发准备篇2:嵌入式开发的特点介绍随着国内第一本RISC-V中文书籍《手把手教你设计CPU——RISC-V处理器篇》 正式上市,越来越多的爱好者开始使用开源的蜂鸟E203

2021-11-03 14:06:02 53

53 该存储库托管开源 Hummingbirdv2 E203 RISC-V 处理器内核和 SoC 项目,由中国大陆领先的 RISC-V IP 和解决方案公司Nuclei System Technology

2022-03-17 16:52:43 11

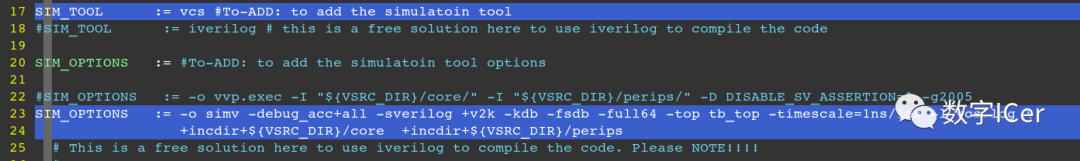

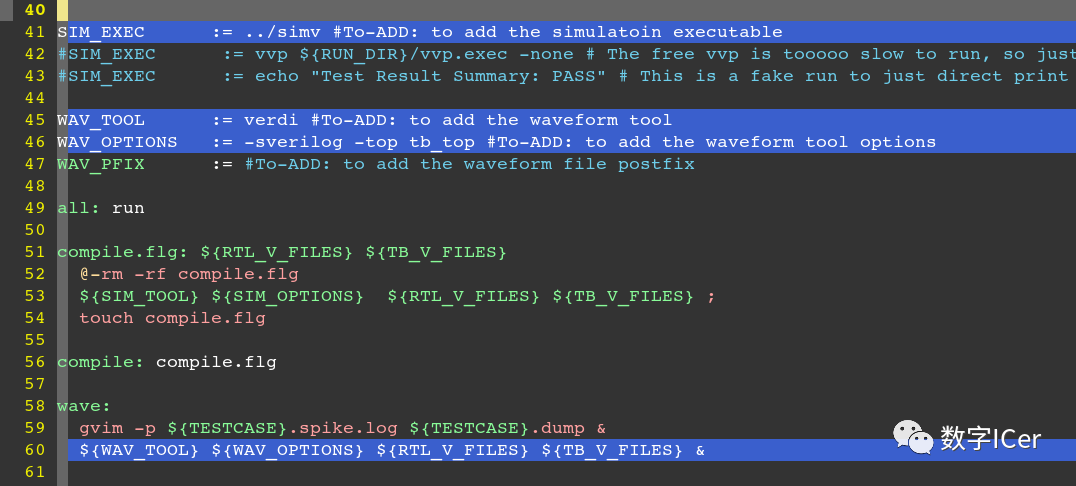

11 开源RISC-V Hummingbird E203(蜂鸟E203)的仿真工具是开源的iverilog,这里利用vcs+verdi仿真工具进行仿真;

2022-11-17 10:28:36 4147

4147 HBird v2 E203是芯来的RISCV的开源(https://github.com/riscv-mcu/e203_hbirdv2)SoC项目,Apache 2.0 License 。主要功能如下框图:

2023-05-05 15:33:57 1849

1849

RISC-V开源创新中心/建设进展“芯片设计正走向开放,灵活、开源的RISC-V有望成为改变一切的芯片设计。”RISC-V将掀起新一轮芯片设计产业变革浪潮,在这股浪潮中,全球首家【RISC-V开源

2024-07-25 08:36:36 1257

1257

电子发烧友App

电子发烧友App

评论