开源RISC-V Hummingbird E203(蜂鸟E203)的仿真工具是开源的iverilog,这里利用vcs+verdi仿真工具进行仿真;

蜂鸟 E200 主要面向极低功耗与极小面积的场景,非常适合于替代Cortex-M 系列内核应用于IoT或其他低功耗场景。

E200系列处理器核使用Verilog语言,采用两级流水线结构,通过一流的处理器架构设计CPU的功耗与面积均优于同级ARM Cortex-M核, 实现业界最高的能效比与最低的成本;

E200 系列处理器核能够运行RISC-V指令 ,支持RV321/E/A/M/C/F/D 等指令子集的配置组合,支持机器模式(Machine Mode Only);

E200 系列处理器核提供标准的JTAG调试接口以及成熟的软件调试工具;

E200 系列处理器核提供成熟的GCC编译工具链;

E200 系列处理器核配SoC提供紧耦合系统 IP 模块,包括中断控制器、计时器UART,QSPI,PWM等,即时能用(Ready-to-Use)的soc平台与PPGA原型系统。

E200系列处理器Soc示意图

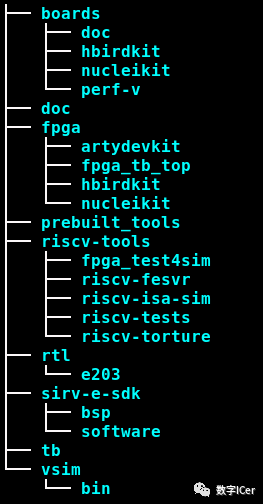

目录:

项目目录

修改

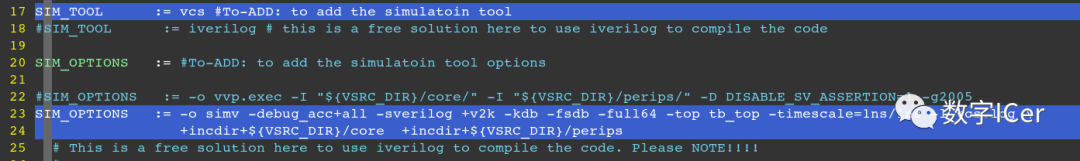

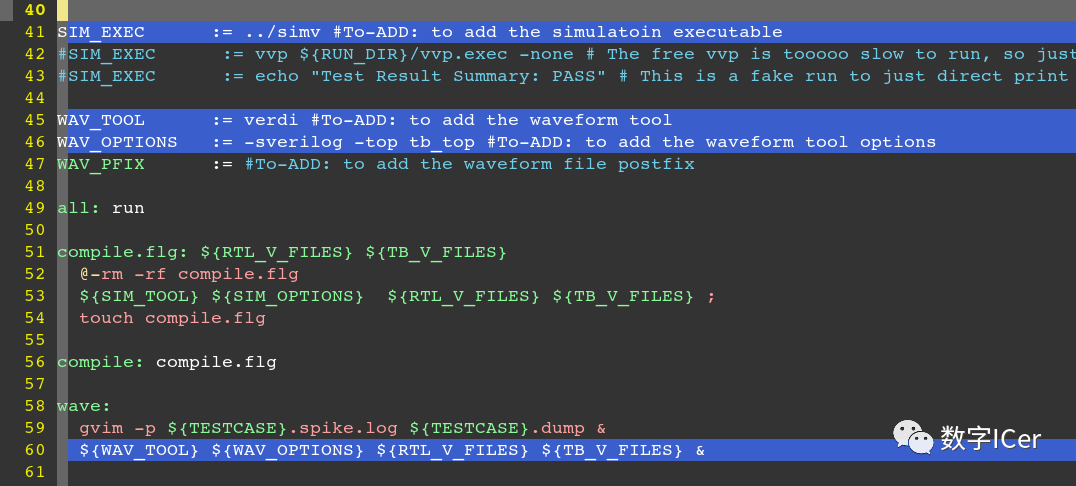

1.修改e200_opensource-master/vsim/bin文件中的run.makefile,修改vcs,verdi仿真工具和仿真选项,如下:

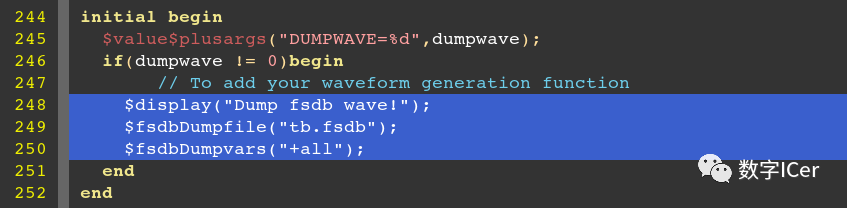

2.e200_opensource-master/tb/tb_top.v增加dump波形

仿真

步骤1:编译 RTL 代码,使用如下命令:

进入到 e200_opensource 目录文件夹下面的 vsim 目录。

make install CORE=e203

运行该命令指明需要为e203进行编译,该命令会在vsim目录下生成一个install子文件夹,在其中放置所需的脚本,且将脚本中的关键字设置为e203。

make compile

运行该命令编译Core和 SoC的RTL代码

步骤2:运行默认的一个testcase(测试用例),使用如下命令:

make run_test

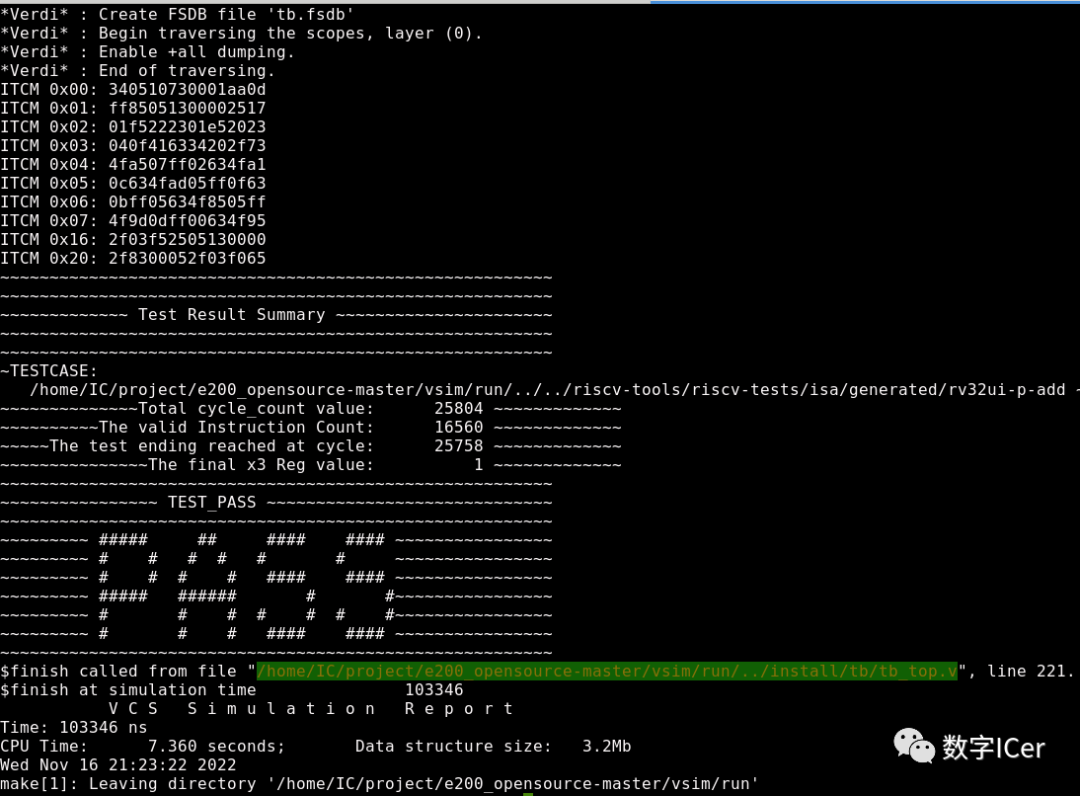

make run_test将执行e200_opensource/riscv-tools/riscv-tests/isa/generated目录中的一个默认testcase,如果测试用例运行通过则打印PASS,并生成波形,如下图,

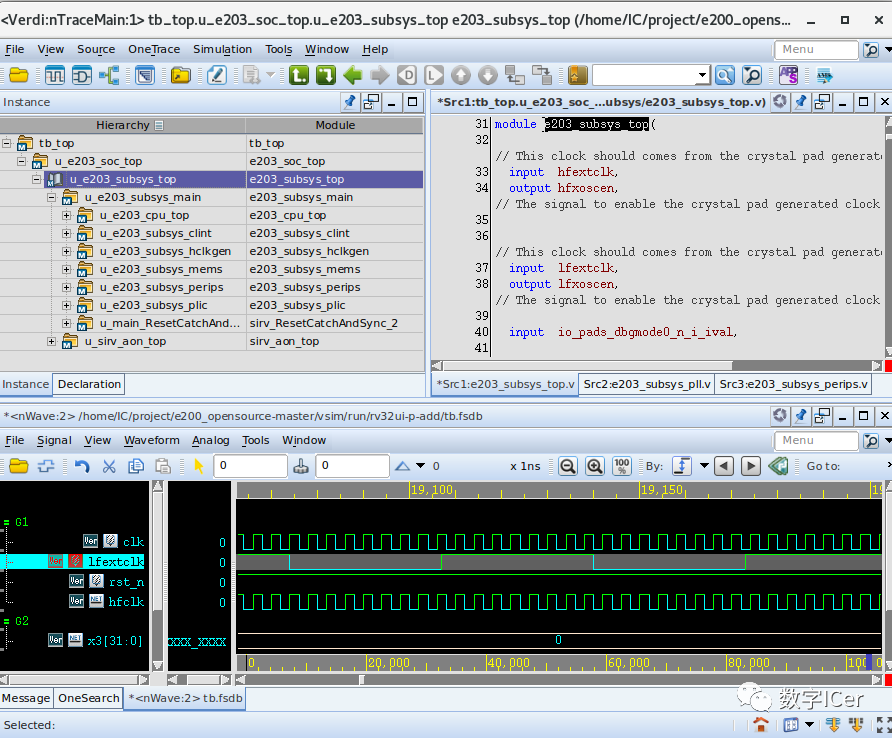

步骤3:打开verdi,加载波形

使用如下命令:make wave

如果希望运行所有的回归测试,请参见步骤4。

步骤4 运行回归 regression 测试集 ,使用如下命令

make regress_run CORE=e203

该命令使用e200_opensource/riscv-tools/riscv-tests/isa/generated目录中E203 Core testcases 逐个的运行各testcase.

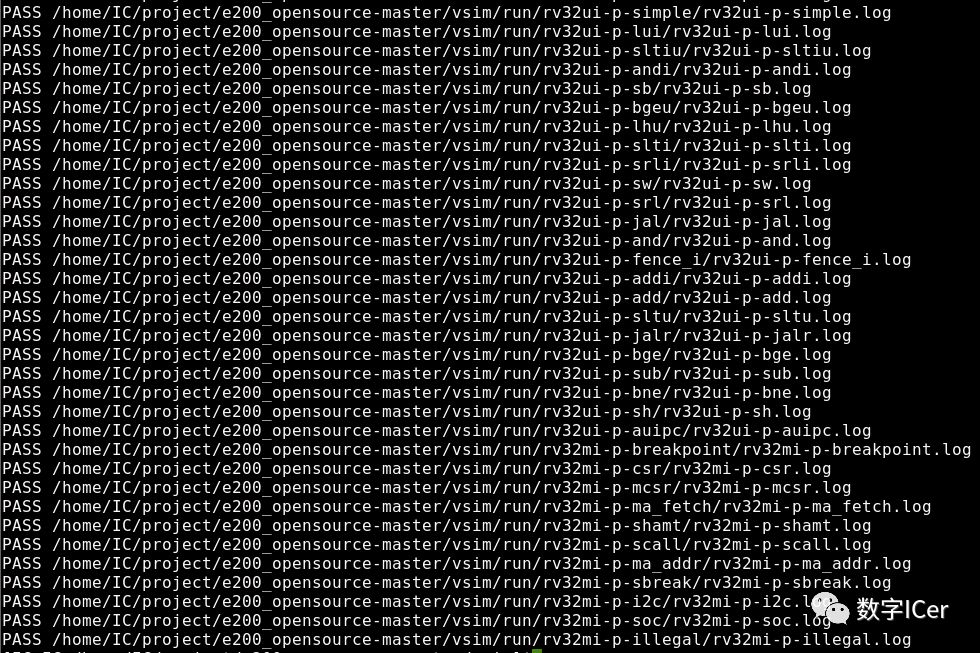

步骤5:查看回归测试结果

make regres_ collect CORE=e203

该命令将收集步骤4中运行的测试集的结果,每行对应一个测试用例,如果测试用例运行通过则打印 PASS ,如果运行失败则打印 FAIL;

审核编辑:郭婷

-

处理器

+关注

关注

68文章

20332浏览量

254916 -

仿真

+关注

关注

55文章

4535浏览量

138659

原文标题:开源RISC-V Hummingbird E203 | vcs+verdi仿真

文章出处:【微信号:数字ICer,微信公众号:数字ICer】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

利用vcs+verdi仿真工具蜂鸟E200系列处理器仿真分析

利用vcs+verdi仿真工具蜂鸟E200系列处理器仿真分析

评论