作为集成电路设计领域现场可编程门阵列 (FPGA) 技术的创造者之一,赛灵思一直积极推广高层次综合 (HLS) 技术,通过这种能够解读所需行为的自动化设计流程打造出可实现此类行为的硬件。赛灵思刚刚推出了一本专著,清晰介绍了如何使用 HLS 技术来创建优化的硬件设计。

这本名为《FPGA 并行编程》的专著出自赛灵思首席工程师 Stephen Neuendorffer 以及来自 UCSD 的 Ryan Kastner 和来自 Cognex 的 Janarbek Matai。该书对于任何有兴趣构建 FPGA 系统的人来说都实属具有实用意义的指南。对于高年级本科生和研究生的课程而言,本书也具有特殊价值。此外,这本书对于在职系统设计人员及嵌入式编程人员同样非常实用。

该书读者只要求具备 C/C++ 编程工作知识,也就相当于汽车驾驶员掌握自动档驾驶水平,而且读者应当熟悉其他基本的计算机架构概念。此外,该书还包含了大量实例代码。我们强烈建议该书读者打开Vivado HLS 并亲自尝试这些实例代码。我们通过 Vivado WebPack Edition 提供免费的 License,或者 Vivado System Edition 的 30 天免费试用期。

此外,该书还提供一些类似教科书的功能,对于课堂教学尤其具有价值。例如,书中每章都会提出问题,向读者提出挑战,有助于读者在阅读时巩固对材料的理解。书中还提供了由加州大学圣迭戈分校 (UCSD) 开发并用于 HLS 课堂教学的有关项目。如欲获得有关项目文件,讲师可向 UCSD 提出申请。各项目在不同程度上都与书中某个章节有关,包括针对 FPGA 板的参考设计,您可以随时联系赛灵思大学计划(XUP)获取。

正如您所预料的那样,随着所读内容的深入,每个项目的复杂性也会提升,因此本书应该循序渐进地阅读。采用这样的阅读方法,读者就能了解到例如 HLS 方法的优化如何能直接应用于特定应用。每款应用也将进一步介绍如何编写 HLS 代码。不过,通过举例法来教学也有其不足之处。首先,大多数应用都需要一些额外的背景知识,以便读者更好地理解正在执行的计算。要真正理解相关计算,通常需要对应用的数学背景进行广泛的讨论。这对只希望了解 HLS 基础知识的读者来说可能缺乏吸引力,不过 Neuendorffer 坚信要想掌握实现最佳设计所必需的代码重构技巧,就必须有这样深入的了解。

虽然《FPGA 并行编程》的章节安排是按照阅读顺序设计的,并且随着读者阅读的深入,章节的复杂性也会提升,但是针对更高级的 HLS 用户,如果只希望了解特定应用领域,那么也可以直接阅读个别章节。例如,对生成硬件加速分类引擎感兴趣的读者可跳至第十章,而无需阅读此前的所有章节。

赛灵思强烈建议将 HLS 作为一种开发 FPGA 集成电路的高效设计流程,从而构建可在汽车、飞机、卫星和其他新兴技术领域中智能且高效工作的硬件。《FPGA 并行编程》将成为推进此类产品开发的重要而高效的指南。欢迎将本书收入实验室的藏书之列以备不时之需。

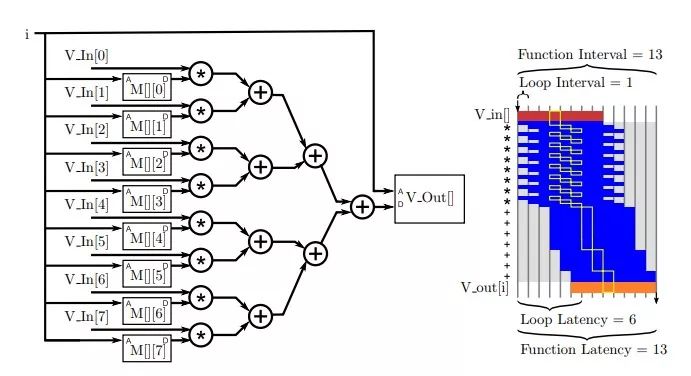

矩阵—矢量乘法架构,配合具体阵列分区和流水线。

已省略流水线寄存器,并将行为显示在右侧。

-

赛灵思

+关注

关注

33文章

1798浏览量

133646 -

硬件设计

+关注

关注

18文章

496浏览量

45688 -

C语言编程

+关注

关注

6文章

90浏览量

22063

发布评论请先 登录

赛灵思FPGA电源解决方案全解析

酷赛智能亮相阿里云通义智能硬件展,展示AI技术应用成果

强强联合进军万亿晶振市场,赛思电子与一晶科技成立合资公司

【精选直播】openDACS2025开源EDA与芯片赛宣讲 赛题一:网表评估和优化

如何在Unified IDE中创建视觉库HLS组件

使用AMD Vitis Unified IDE创建HLS组件

授时系统厂家,授时系统哪家好?赛思高精度授时系统助力华福证券授时服务新升级!

赛灵思推出一本专著,介绍如何使用HLS技术来创建优化的硬件设计

赛灵思推出一本专著,介绍如何使用HLS技术来创建优化的硬件设计

评论