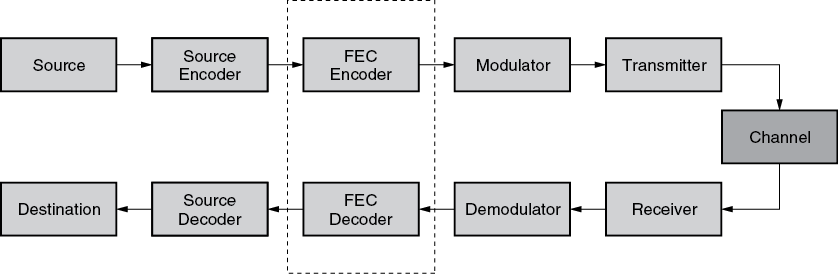

无论是无线还是有线数据通信,保持传输可靠性都是高质量解决方案的基本要求。此类系统的关键构成部分在于高性能软判决前向纠错 (SD-FEC) 功能,发送(编码器)和接收(解码器)路径都需要这个功能。

图 1:典型的数据通信系统

随着数据带宽的不断提升,例如 5G 新无线电 (5G NR) 技术和有线电缆数据服务接口规范 3.1 (DOCSIS 3.1),上述系统对数据吞吐量要求极高,因此,SD-FEC 块必须实现高效处理。

赛灵思推出业界首款可配置集成型 (SD-FEC) IP 块

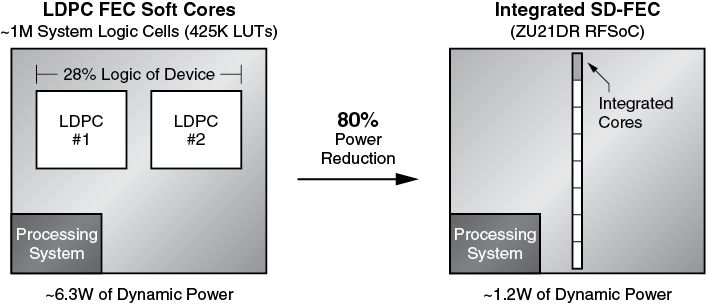

此类 SD-FEC 功能通常在高性能 FPGA 的可编程逻辑中实现。随着为了支持数千兆位速率而进一步推进系统要求,性能、功耗和成本均成为了关键设计因素。相对于集成型解决方案而言,上述功能的软实现不尽人意。

因此,赛灵思推出了业界首款可配置集成型 SD-FEC IP 块,可实现:

缓解性能和吞吐量瓶颈 → 约 3 Gb/s 的峰值 LDPC 解码吞吐量

大幅降低资源需求 → 每个 SD-FEC 实例减少约 10 万 LUT

大幅降低功耗 → 转向集成型解决方案,功耗降低 80%

图 2:集成型 SD-FEC 与软 LDPC 解码器的功耗对比

采用 SD-FEC 功能集成成果的应用实例

如前所述,类似于 ASIC 的 SD-FEC 块相对于软实现而言能提高吞吐量,降低时延,并降低功耗。由于能够为 Turbo 解码的长期演进发展 (LTE) 以及 LTE-A 应用提供支持,因此构成了 4G 和 5G 前系统的低功耗解决方案。

利用低密度奇偶校验 (LDPC) 对解码和编码的支持,我们能够为无线市场的 5G 基带和回传平台等应用提供支持。除 Zynq UltraScale+ RFSoC (ZU28DR) 系列中的 RF-ADC/DAC 之外,SD-FEC 还为 DOCSIS 3.1 标准的远程 PHY 提供了极富吸引力的解决方案。

-

集成

+关注

关注

1文章

178浏览量

30820 -

可编程逻辑

+关注

关注

7文章

526浏览量

45307

发布评论请先 登录

RDMA设计4:技术需求分析2

易灵思助力上海集成电路紧缺人才培训项目顺利结课

跨越域冲突:多实例并发与PTP可配置性的融合之道

Aurora接口的核心特点和应用场景

赛昉科技携手英思集成,共建“中国高等院校RISC-V芯片设计及应用实验室”

芯片引脚成型设备与芯片引脚整形设备的区别

易灵思 FPGA TJ375的PLL的动态配置

中微爱芯推出可配置多功能逻辑门电路AiP74LVC1G99

Xilinx Shift RAM IP概述和主要功能

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

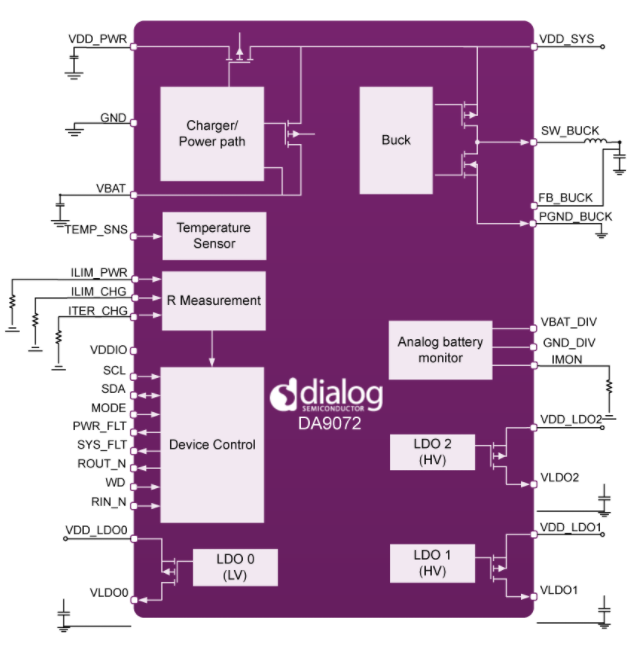

高度集成、可配置的低静态电流电源管理IC DA9072数据手册

RF-Labs手工成型电缆组件

国产EDA亿灵思®接入DeepSeek

赛灵思推出可配置集成型IP块大幅降低资源需求

赛灵思推出可配置集成型IP块大幅降低资源需求

评论