重定时概述

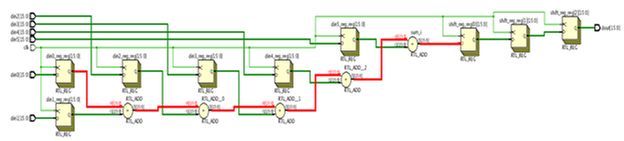

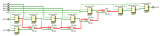

重定时是一种顺序优化技术,旨在不会影响电路的输入/输出行为的前提下在组合逻辑之间移动寄存器,以提高设计性能。图 1 所示电路的关键路径使用了一个 6 输入加法器。以红色突出显示的路径是对整个电路的性能起限制作用的路径。

图 1:寄存器到寄存器路径设计示例:使用 6 个输入加法器逻辑

通过将加法器输出上的寄存器重定时到电路的组合逻辑,可以提升这里所示电路的性能。

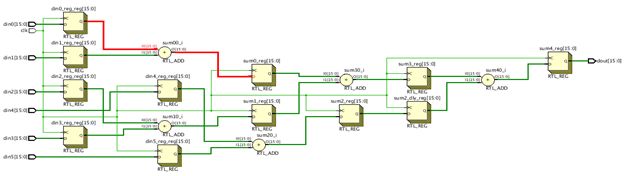

电路的整体时延为 4。图 2 显示移动寄存器使逻辑最小化的一种方法。将输出寄存器移动到逻辑锥中被称为后向重定时。完成此操作后,关键路径将减少为只使用一个 2 输入加法器。

图 2:寄存器到寄存器路径设计示例:通过应用反向重定时使用一个 2 输入加法器

注意:在上述示例中,寄存器的数量改变了。

图 1 使用了 9 条不同的寄存器总线。图 2 使用了 12 条不同的寄存器总线。这样做的原因是,当执行向后重定时时,即当它从输出移动到输入时,门的两个输入一定各有一个寄存器。

有两种不同类型的重定时:后向重定时和前向重定时。后向重定时从门的输出中移除寄存器,并在同一个门的输入处创建新的寄存器。前向重定时完全相反,它从门的输入端移除寄存器,并在输出端创建一个新的寄存器。

要执行后向重定时操作,组合逻辑必须仅驱动寄存器,而不是扇出到其他逻辑。要执行前向重定时操作,门的每个输入必须由具有相同控制逻辑的寄存器驱动。图 3 显示的是采用前向或后向重定时的同一个电路。

图 3:前向重定时或后向后重定时的与门

全局重定时与局部后重定时

在 Vivado 综合中,有两种启用重定时的方式:“全局”和“局部”。

全局重定时对整个设计进行重定时,并根据设计时序在大型组合逻辑结构中移动寄存器。

它会对设计中的所有逻辑进行分析,并在最坏情况的路径中移动寄存器,以便设计能够跑得更快。为了完成此操作,设计必须在 .xdc 文件中含有准确的时序约束。使用 synth_design 命令行中或 Vivado GUI 中综合设置下的 -retiming 开关启用全局重定时。 此外,此功能还可以与综合中的 BLOCK_SYNTH 功能一起使用,作用于您设计中的特定模块。

局部重定时是指用户明确告诉工具使用 retiming_forward/retiming_backward RTL 属性执行重定时时的逻辑。

在执行局部重定时时应小心,由于这种重定向不是时序驱动的,工具会完全按照要求进行操作。

如需了解更多有关使用重定时的信息,请参阅《Vivado Design Suite 用户指南:综合》 (UG901)。

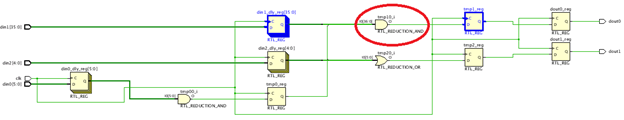

分析日志文件中的消息,图 4 显示的是可以改善逻辑层次的重定时示例。该结构的关键路径有 3 个来自 37 位的与门的逻辑层次。源寄存器被称为 din1_dly_reg,目标寄存器被称为 tmp1_reg,在 tmp1_reg 后面还有一个逻辑层次为 0 的额外寄存器。

这是重新定时的理想途径,因为我们可以把一个有 3 个逻辑层次的路径(后跟逻辑层次为 0 的路径)切换到有 2 个逻辑层次的路径(后跟一个有 1 或 2 个逻辑层次的路径)。

图 4:可以向后重定时的电路

综合日志文件类似于以下内容:

INFO: [Synth 8-5816] Retiming module "test"

Effective logic levels on critical path before retiming is: 3

Total number of crtical paths = 30

Optimizing at the module level

Optimizing locally to improve critical paths (may not reduce worst delay)

Effective logic levels on critical path after retiming is: 2

Total number of crtical paths = 30

Numbers of forward move = 0, and backward move = 1

Retimed registers names:

tmp1_reg_bret

tmp1_reg_bret__0

INFO: [Synth 8-5816] Retiming module "test" done

从此日志文件中,您可以看到重新定时之前和之后报告的逻辑层次,以及创建的新寄存器的名称。当综合从重定时创建新寄存器时,它会对后向重新定时的寄存器使用后缀“bret”、对前向重定时的寄存器使用“fret”。

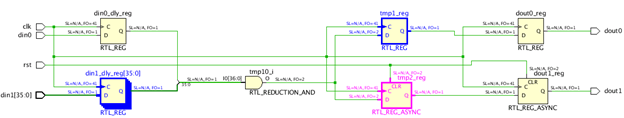

图 5 中显示的电路展示的是不兼容的寄存器元件会让重定时变为非法操作。该结构使用的仍是一个名为 din1_dly_reg 的启动寄存器,通过一个 37 位的与门,产生 3 个逻辑层次,然后最后是一个名为 din1_dly_reg 的寄存器。此外,与门还有另一个以粉红色突出显示的寄存器扇出。

图 5:无法重定时的电路示例

由于以粉色突出显示的寄存器的存在,此示例无法重新定时。该寄存器采用了异步复位,而 tmp1_reg 没有采用异步复位。由于两个寄存器的控制集不相同,因此它们无法后向重定时到与门逻辑。此示例中的日志文件会显示以下内容:

INFO: [Synth 8-5816] Retiming module "test"

Effective logic levels on critical path before retiming is: 3

Total number of crtical paths = 60

Optimizing at the module level

Cannot find a feasible solution:

backward propagation for flip-flop tmp1_reg:FD along instance tmp1_i_1:LUT2 fails due to incompatible flip-flops

Optimizing locally to improve critical paths (may not reduce worst delay)

Effective logic levels on critical path after retiming is: 3

Total number of crtical paths = 60

Numbers of forward move = 0, and backward move = 0

Retimed registers names:

tmp1_reg_bret

tmp1_reg_bret__0

INFO: [Synth 8-5816] Retiming module "test" done

日志文件内含有关不兼容触发器的消息,并且之前和之后的逻辑层次不会改变。

在以下情况下不能进行重定时:

寄存器上加有时序异常约束(多周期路径、可忽略路径、最大延迟)。

存器有保留类型的属性(DONT_TOUCH、MARK_DEBUG)。

带有不同控制集的寄存器。

寄存器驱动输出或由输入驱动(除非设计被标记为 out-of-context)。

重定时无法提升反馈循环中的关键路径的示例

当路径的源寄存器和目标寄存器相同时,重定时优化有可能无法改善逻辑层次。

例如:

寄存器“dout_reg”的关键路径以红色突出显示。它通过一个减位与运算符,并在同一寄存器的复位引脚处结束。减位与运算符将基于我们采用的宽度(即 16 位)占用 2 个逻辑层次。

下面的屏幕截图显示综合对关键路径的性质的描述。

它还提到了作为关键路径一部分的单元名称。

INFO: [Synth 8-5816] Retiming module "test"

Effective logic levels on critical path before retiming is: 2

Total number of crtical paths = 192

Optimizing at the module level

Cannot find a feasible solution:

Worst path is a self-loop from dout_reg[14] to dout_reg[14]

Optimizing locally to improve critical paths (may not reduce worst delay)

Effective logic levels on critical path after retiming is: 2

Total number of crtical paths = 192

Numbers of forward move = 0, and backward move = 0

-

电路

+关注

关注

173文章

6064浏览量

177589 -

寄存器

+关注

关注

31文章

5590浏览量

129197

发布评论请先 登录

Vivado综合操作中的重定时(Retiming)

如何在Vivado 2016.1中进行寄存器平衡/寄存器重定时?

如何为管道设计插入寄存器并进行重定时?

Vivado 全局重定时vs 局部重定时

基于vivado的fir ip核的重采样设计与实现

Vivado 2017.1和Vivado 2016.4性能对比分析

Tcl在Vivado中的基础应用

Vivado中的重定时概述和应用

Vivado中的重定时概述和应用

评论