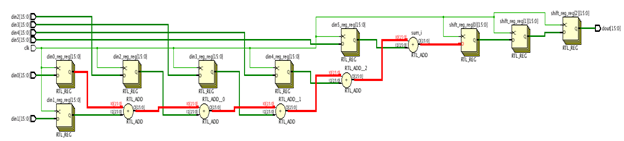

重定时(Retiming)是一种时序优化技术,用在不影响电路输入/输出行为的情况下跨组合逻辑寄存器从而提高设计性能。图1所示的电路是六输入加法器,其中有一条关键路径,红色推出显示的路径是限制整个电路性能的关键路径。

图1:六输入加法器寄存器到寄存器之间的信号路径示例

通过对加法器输出路径上寄存器进行重定时设计,调整电路的组合逻辑,可以改变整个电路的性能。

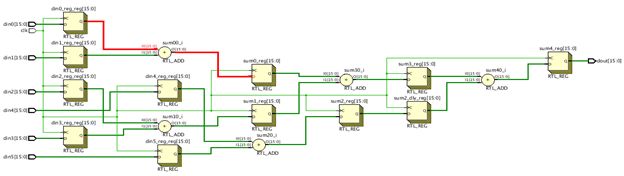

整个电路的延迟是4,图2展示的是一种寄存器组合方法可以将逻辑最小化,将输出寄存器融合到逻辑寄存器中称为向后重定时设计,这一步完成后关键路径被压缩为二输入加法器。

图2:采用向后重定时方案二输入加法器寄存器到寄存器路径设计的一个示例

关于上述 示例需要注意的另一点是寄存器数量的变化。

图1采用9个不同寄存器总线,图2使用了12个不同寄存器总线,产生这样结果的原因是当采用向后重定时设计时,当寄存器从输出移动到输入时,逻辑门的两个输入都必须增加一个寄存器。

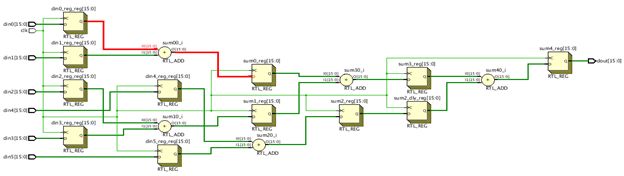

有两种不同的重定时方法,向后重定时和向前重定时。向后重定时从门的输出中删除寄存器,并在同一逻辑门的输入出创建新的寄存器。向前重定时的作用正好相反,它从逻辑门的输入中删除寄存器,并在输出中创建新的寄存器。

若要向后重定时,组合逻辑必须仅用来驱动寄存器,而不能向其他逻辑寄存器展开,为了使前向重定时正常工作,逻辑门的每个输入必须有具有相同控制逻辑的寄存器来驱动。

图3:逻辑与门(AND)采用前向重定时和后向重定时的效果

全局重定时vs 局部重定时

在Vivado 综合操作中有两种方法实现自动重定时:全局重定时和局部重定时。

全局重定时是对整个设计而言的,基于设计时的时序要求优化大型组合逻辑结构中的寄存器设计。

这种方式需要分析设计中的所有逻辑,优化最坏路径情况下的寄存器从而使整体设计反应速度更快。为了实现这一点设计时必须在.xdc文件中规定准确的时间限制。在synth_design或Vivado GUI综合设置下通过-retiming命令启用全局重定时,此外该特性还可以与合成中的BLOCK_SYNTH特性一起用于设计中的特定模块。

局部重定时是指用户明确告诉工具使用retiming_forward、retiming_bbackward RTL属性时需要执行的重定时逻辑。

执行局部重定时操作是应该要小心,因为它不是计时器驱动的,而是工具将完全按照用户要求去执行。

有关重定时使用的更多信息,请参阅(UG901)Vivado设计工具用户指南:Synthesis(综合)。

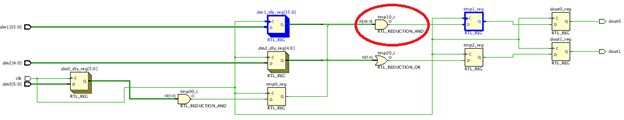

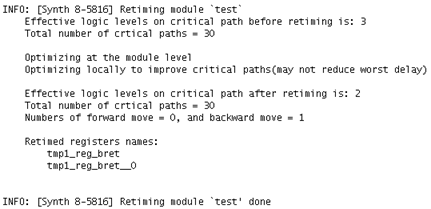

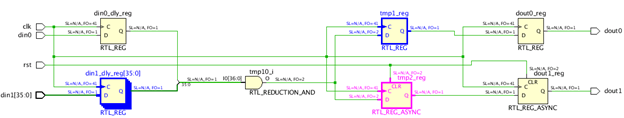

分析日志文件中的信息

图4是通过重定时提升逻辑水平的一个例子,该电路结构中有一个关键的路径分为三个逻辑层,组成的是一个37位的逻辑与门(AND),源寄存器命名为din1_dly_reg,目标寄存器命名为tmp1_reg,在逻辑级别为0的tmp1_reg后面增加一个额外的寄存器。

这是一个理想的重定时逻辑路径设计,因为我们可以切换为三个逻辑级别的路径,由0、1、2三个局部逻辑电路模块组成。

图4:采用后向重定时设计的电路

综合操作日志文件包含的信息大致如下:

从这个日志文件中你可以看到重定时操作前后的逻辑门信息对比,以及创建的新寄存器名称,当synthesis通过重定时创建新寄存器时,它将对后向重定时的寄存器使用后缀“bret”,对前向重定时寄存器使用后缀“fret”。

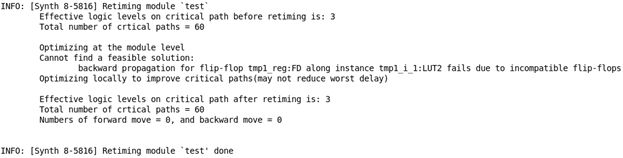

图5展示的电路中一些不兼容的寄存器将无法进行重定时操作,这个结构中同样有一个名为din1_dly_reg的源寄存器,它经过37位逻辑与门生成三级逻辑电路结构,然后在din1_dly_reg寄存器前结束。此外逻辑与门还有一路连接到另外一个寄存器,如下图粉色高亮显示的部分。

图5:不能进行重定时操作电路的示例

这是示例不能进行重定时操作是因为粉红色高亮显示的部分,这个寄存器需要一部重置,而tmp1_reg没有这个功能,因为这两个寄存器没有相同的控制集,所以它们不能向后重定时到新的逻辑与门电路中,本例的日志文件信息如下:

这个日志文件包含的信息是关于 不兼容的FIFO寄存器的,前后的电路的逻辑层级不变。

以下情况下不能进行重定时操作:1. 寄存器时序异常(多循环路径、错误的路径、最大延迟路径)2. 寄存器的类型属性不能改变(DONT_TOUCH, MARK_DEBUG)3. 采用不同控制级的寄存器

驱动输出的寄存器或者被输入驱动的寄存器(除非这部分是与前后电路不相关的)

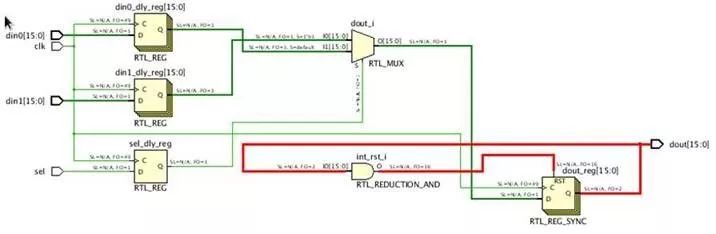

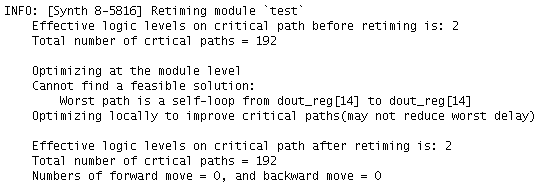

重定时无法改善反馈循环回路中关键路径的性能的一个例子:

当路径中具有相同的源寄存器和目标寄存器时,重定时优化操作可能无法改进整个逻辑电路的结构。

举个例子:

寄存器“dout_reg”的关键路径如下图中红色所示,要经过一个逻辑与运算,然后连接到同一寄存器的复位管脚上才算结束。

根据数位宽度(16比特)逻辑与门电路要占用两个逻辑操作。

下面的屏幕截图显示了综合操作如何描述关键路径的

其中还提到了关键路径中一部分模块或寄存器的名字。

-

寄存器

+关注

关注

31文章

5620浏览量

130432 -

总线

+关注

关注

10文章

3060浏览量

91870 -

Vivado

+关注

关注

19文章

860浏览量

71408

原文标题:Vivado综合操作中的重定时(Retiming)

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Vivado 高层次综合

探索Vivado HLS设计流,Vivado HLS高层次综合设计

vivado 2015.3 综合报错

Vivado 2015.4许可证与Windows 10操作系统工作出现综合错误

Vivado综合操作中的重定时(Retiming)

运行综合时Vivado崩溃

在vivado中综合Soc设计时发现的错误,请问如何解决?

如何为管道设计插入寄存器并进行重定时?

Vivado 全局重定时vs 局部重定时

使用Vivado高层次综合 (HLS)进行FPGA设计的简介

Vivado综合引擎的增量综合流程

Vivado综合参数设置

Vivado综合操作中的重定时(Retiming)

Vivado综合操作中的重定时(Retiming)

评论