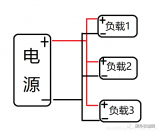

前段时间有跟大家分享过去耦电容的有效使用方法——“要点一”使用多个去耦电容,今天为大家继续介绍“要点二”降低电容的ESL(等效串联电感)

去耦电容的有效使用方法要点一点击链接

要点2:降低电容的ESL(等效串联电感)

去耦电容的有效使用方法的第二个要点是降低电容的ESL(即等效串联电感)。虽说是“降低ESL”,但由于无法改变单个产品的ESL本身,因此这里是指“即使容值相同,也要使用ESL小的电容”。通过降低ESL,可改善高频特性,并可更有效地降低高频噪声。

即使容值相同也要使用尺寸较小的电容

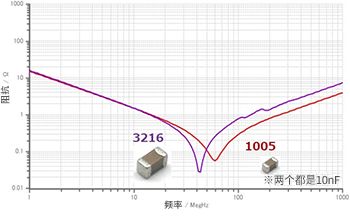

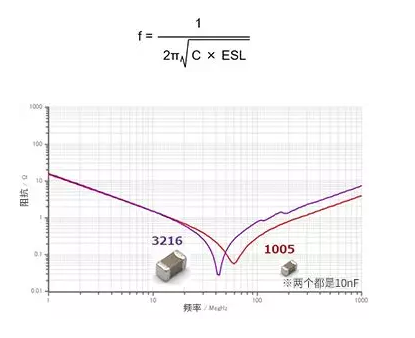

对于积层陶瓷电容(MLCC),有时会准备容值相同但尺寸不同的几个封装。ESL取决于引脚部位的结构。尺寸较小的电容基本上引脚部位也较小,通常ESL较小。

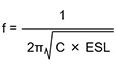

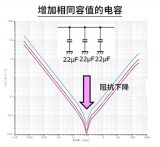

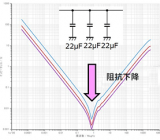

下图是容值相同、大小不同的电容的频率特性示例。如图所示,更小的1005尺寸的谐振频率更高,在之后感性区域的频率范围阻抗较低。这正如在“电容的频率特性”中所介绍的,电容的谐振频率是基于以下公式的,从公式中可见,只要容值相同,ESL越低谐振频率越高。另外,感性区域的阻抗特性取决于ESL,这一点也曾介绍过。

关于噪声对策,当需要降低更高频段的噪声时,可以选择尺寸小的电容。

使用旨在降低ESL的电容

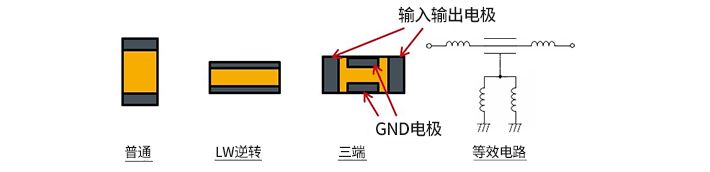

积层陶瓷电容中,有些型号采用的是旨在降低ESL的形状和结构。

如上图所示,普通电容的电极在短边侧,而LW逆转型的电极则相反,在长边侧。由于L(长度)和W(宽度)相反,故称“LW逆转型”。是通过增加电极的宽度来降低ESL的类型。

三端电容是为了改善普通电容(两个引脚)的频率特性而优化了结构的电容。三端电容是将双引脚电容的一个引脚(电极)的另一端向外伸出作为直通引脚,将另一个引脚作为GND引脚。在上图中,输入输出电极相当于两端伸出的直通引脚,左右的电极当然是导通的。这种输入输出电极(直通引脚)和GND电极间存在电介质,起到电容的作用。

将输入输出电极串联插入电源或信号线(将输入输出电极的一端连接输入端,另一端连接输出端),GND电极接地。这样,由于输入输出电极的ESL不包括在接地端,因此接地的阻抗变得非常低。另外,输入输出电极的ESL通过在噪声路径直接插入,有利于降低噪声(增加插入损耗)。

通过在长边侧成对配置GND电极,可抑制ESL;再采用并联的方式,可使ESL减半。

基于这样的结构,三端电容不仅具有非常低的ESL,而且可保持低ESR,与相同容值相同尺寸的双引脚型电容相比,可显著改善高频特性。

关键要点:

去耦电容的有效使用方法有两个要点:

①使用多个电容,②降低电容的ESL。

通过降低电容的ESL,可改善高频特性,并可更有效地降低高频噪声。

有的电容虽然容值相同,但因尺寸和结构不同而ESL更小。

-

引脚

+关注

关注

16文章

2123浏览量

56061 -

去耦电容

+关注

关注

12文章

325浏览量

23619 -

高频噪声

+关注

关注

1文章

22浏览量

3376

发布评论请先 登录

去耦电容的接地原则

关于去耦电容的有效使用方法要点分享

关于去耦电容的有效使用方法要点分享

评论