乘法器是众多数字系统中的基本模块。从原理上说它属于组合逻辑范畴:但从工程实际设计上来说,它往往会利用时序逻辑设计的方法来实现,属于时序逻辑的范畴。

通过这个实验使大家能够掌握利用FPGA/CPLD设计乘法器的思想,并且能够将我们设计的乘法器应用到实际工程中。乘法器的设计方法有两种:组合逻辑设计方法和时序逻辑设计方法。采用经合逻辑设计方法,电路事先将所有的乘积项全部计算出来,最后加法运算。采用时序逻辑设计方法,电路将部分已经得到的乘积结果右移,然后与乘积项相加并保存和值,反复迭代上述步骤直到计算出最终乘积。

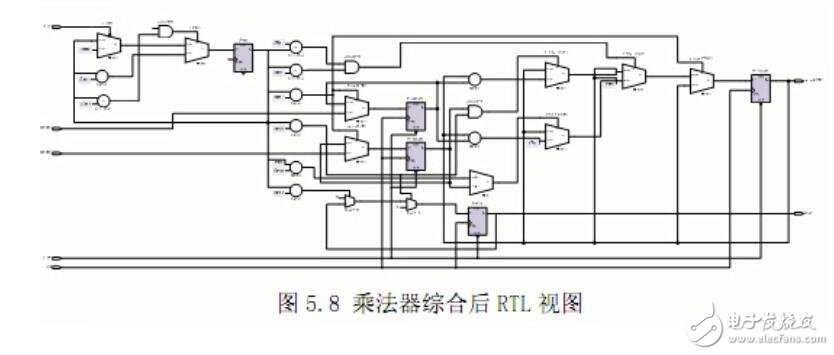

在该实验中就是要利用时序逻辑设计方法来设计-一个16位乘法器,既然是利用时序逻辑设计方法那么就得利用时钟信号控制乘法器运算。用时序逻辑设计方法与用组合逻辑设计方法比较,它有什么好处呢?利用时序逻辑设计方法可以使整体设计具备流水线结构的特征,能适用在各种实际工程设计中。

更多关于BJ-EPM240学习板之乘法器设计实验请看视频。

-

FPGA

+关注

关注

1655文章

22283浏览量

630223 -

乘法器

+关注

关注

9文章

221浏览量

38520

发布评论请先 登录

使用Xilinx 7系列FPGA的四位乘法器设计

E203在基于wallace树+booth编码的乘法器优化后的跑分结果

E203V2长周期乘法器核心booth算法解读

蜂鸟E203乘法器的优化——基8的Booth编码+Wallace树

Verilog实现使用Booth编码和Wallace树的定点补码乘法器原理

改进wallance树乘法器优化方法

关于E203内核高性能乘法器优化(一)

蜂鸟乘法器设计分享

基4-Booth单周期乘法器的具体设计

改进型乘法器结构设计

蜂鸟E203乘法器改进

蜂鸟E203内核乘法器的优化

优化boot4乘法器方法

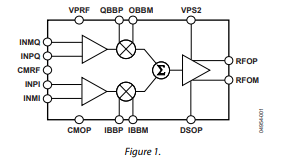

ADL5390 RF矢量乘法器技术手册

BJ-EPM240学习板之乘法器设计实验

BJ-EPM240学习板之乘法器设计实验

评论