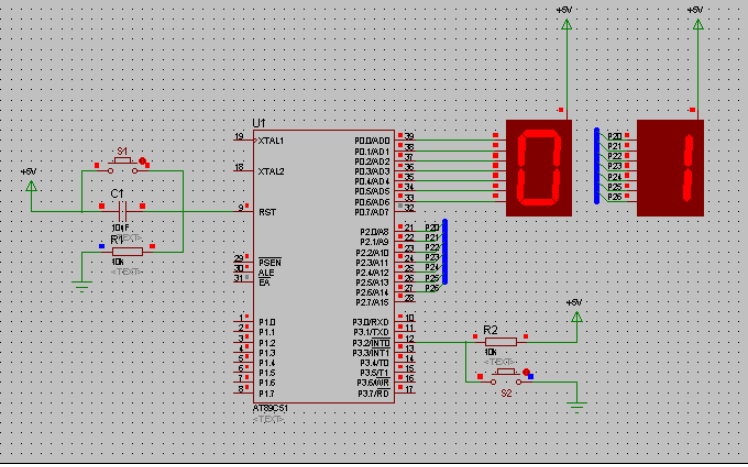

数码管动态显示接口是单片机中应用最为广泛的一种显示方式之一,动态驱动是将所有数码管的8个显示笔划"a,b,c,d,e,f,g,dp"的同名端连在一起,另外为每个数码管的公共极COM增加位选通控制电路,位选通由各自独立的I/O线控制,当单片机输出字形码时,所有数码管都接收到相同的字形码,但究竟是哪个数码管会显示出字形,取决于单片机对位选通COM端电路的控制,所以我们只要将需要显示的数码管的选通控制打开,该位就显示出字形,没有选通的数码管就不会亮。通过分时轮流控制各个数码管的的COM端,就使各个数码管轮流受控显示,这就是动态驱动。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22503浏览量

639264 -

单片机

+关注

关注

6078文章

45580浏览量

673679 -

数码管

+关注

关注

32文章

1894浏览量

94427

发布评论请先 登录

相关推荐

热点推荐

【正点原子FPGA连载】第十二章 动态数码管显示实验

/1WzZfnb0gGPkthV7x_SrsKw 提取码:vjpn4)对正点原子FPGA感兴趣的同学可以加群讨论:712557122点击加入:5)关注正点

发表于 06-15 22:54

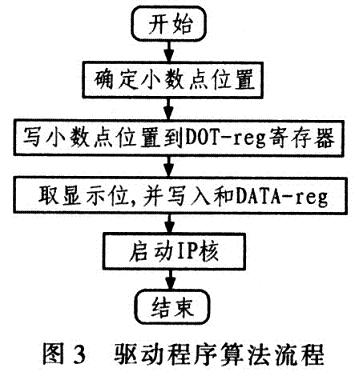

基于FPGA的8段数码管动态显示IP核设计

基于FPGA的8段数码管动态显示IP核设计

引言

数码管可显示简单的字符和数字,由于其价格低廉、性能稳定、

发表于 02-03 10:03

•2669次阅读

FPGA入门系列实验教程之使用FPGA实现数码管动态显示的资料免费下载

实现开发板上 8 个数码管动态显示 0~7。通过这个实验,掌握采用 Verilog HDL语言编程实现 7 段数码管显示译码器以及

发表于 06-12 16:32

•15次下载

正点原子开拓者FPGA:数码管动态显示实验

正点原子开拓者FPGA:数码管动态显示实验

评论