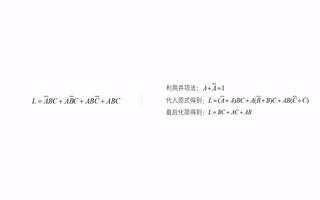

多数表决器常见于信号处理。例如,在自动控制中,对三个针对同一事物的信号使用多数表决器进行运算,并按照其中两个一致的结果执行。这样既可以提高信号的可靠性(信号不止一个),又避免信号源错误(出错的信号在表决中被排除)造成不必要的损失。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22503浏览量

639279 -

IP核

+关注

关注

4文章

345浏览量

52100 -

表决器

+关注

关注

2文章

15浏览量

11741

发布评论请先 登录

相关推荐

热点推荐

74ls151应用电路图大全(全加器\表决器)

本文主要介绍了74ls151应用电路图大全(全加器\表决器)。五人表决器,只要赞成人数大于或等于三,则表决通过。因此,只需将每位表决人的结果相加,判断结果值。设五个开关A、B、C、D、

发表于 05-07 11:38

•13.7w次阅读

锆石FPGA A4_Nano开发板视频:三人表决器的功能叙述与设计

表决器,是投票系统中的客户端,是一种代表投票或举手表决的表决装置。表决时,与会的有关人员只要按动各自表决器上“赞成”、“反对”、“弃权”的某

锆石FPGA A4_Nano开发板视频:三人表决器的设计与分析

表决器,是投票系统中的客户端,是一种代表投票或举手表决的表决装置。表决时,与会的有关人员只要按动各自表决器上“赞成”、“反对”、“弃权”的某

数字设计FPGA应用:调用IP核实现多数表决器

数字设计FPGA应用:调用IP核实现多数表决器

评论